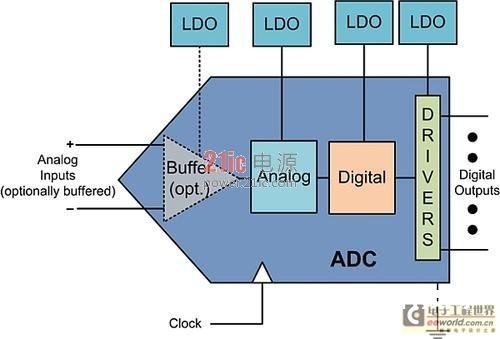

考虑到现在可用ADC的采样速度以及典型ADC内部的很多不同电压和时钟域,一般主张把不同电源输入分隔。 让不同电源输入分属不同的域,电源之间的串扰便可降至最低,噪声将更难以跨过不同的域,防止蠕升并形成ADC功能问题。 假如无法将其放在不同的域上,至少应运用铁氧体磁珠等元件,在不同电源域之间供给必定的阻隔。 别离驱动不同电源输入的一种办法是运用低压差(LDO)稳压器。 实例如下面的图1所示。

Figure 1

图1

用不同的LDO驱动不同的ADC电源

LDO一般是最安全的电源类型,驱动ADC电源输入的危险也最小。 一般来说,LDO的噪声十分低,电源按捺比(PSRR)则很高。 低压差一般意味着,LDO的输入电源能够低到仅比LDO的输出电压高出数百毫伏。 例如,ADP1741 2A LDO的裕量小至400 mV(Vin有必要比Vout高出400 mV)。 关于典型ADC的1.8 V供电轨,这意味着LDO的功率约为Vout/Vin = 1.8/2.2 = 81.8%。

这在任何含义上说都不是低功率,但咱们会发现,能够运用更高功率的器材来驱动ADC电源输入。 可是,这些器材的高功率不是随便取得的。 方才说过,LDO的两个首要优势是低噪声和高PSRR。 其它器材一般是用噪声来交换功率。

关于ADP1741,输出电压为2.5 V时,10 Hz到100 kHz规模的输出噪声典型值为65 µVrms。 下面经过一个比如阐明这种噪声奉献的影响。 一个14位250 MSPS ADC的满量程输入为2.0 Vpp,SNR为70 dB,噪底为20 nVrms/rt-Hz。 在榜首奈奎斯特区,ADC噪声将是223.61 µVrms (20 nVrms/rt-Hz * sqrt(250 MHz/2))。 这种情况下,ADP1741输出噪声远低于ADC噪声。 此外,ADC的PSRR(典型值为60 dB)会将ADP1741噪声从65 µVrms进一步下降至65 nVrms (65 µVrms X 1 mV/V)。 这样便很简单理解为什么LDO是驱动电源输入的超卓挑选。 它对ADC噪声简直无影响。

可是,这是有价值的。 运用LDO的一个显着缺陷是其潜在的功耗。 例如,假定上例中的14位ADC是一个四通道器材,总功耗为2 W,其间1 W是AVDD电源所需。 本例中,LDO的输入电源受到限制,咱们只要6 V输入可用来驱动1.8V AVDD电源。 这意味着,ADP1741将需求耗费大约(6 V – 1.8 V)/1800 mA = 2.33 W的功率。 ADP1741的最高结温(Tj)将被推高至TA + Pd X Θja = 85°C + (2.33 W X 42°C/W) = 183°C,超越LDO的150°C最大额定值。

当然,这是一个极点比如,但它阐明晰需求为LDO供给低输入电压的重要性。 这或许导致需求运用多个LDO来将电压从较高输入供电轨下降至ADC所需的较低输入供电轨。