The S3C2440A memory controller provides memory control signals that are required for external memory access.

The S3C2440A has the following features:

— Little/Big endian ( selectable by a software)

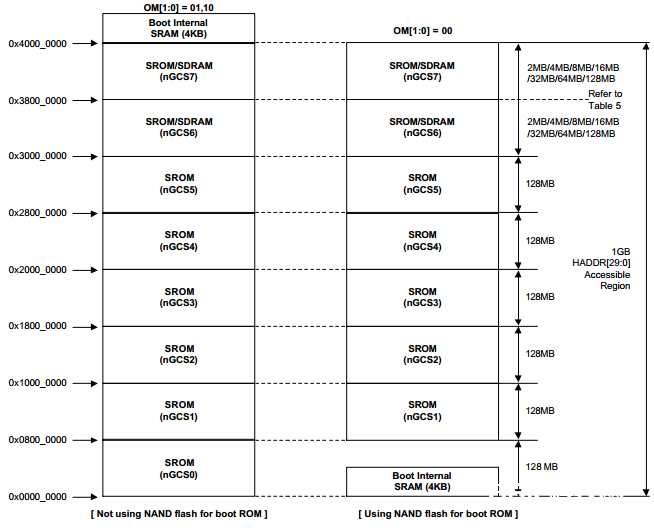

— Address space: 128Mbytes per bank (total 1GB/8 banks)

— Programmable access size (8/16/32-bit) for all banks except bank0 (16/32-bit)

— Total 8 memory banks

Six memory banks for ROM, SRAM, etc.

Remaining two memory banks for ROM, SRAM, SDRAM, etc .

— Seven fixed memory bank start address

— One flexible memory bank start address and programmable bank size

— Programmable access cycles for all memory banks

— External wait to extend the bus cycles

— Supporting self-refresh and power down mode in SDRAM

翻译如下:

在S3C2440A存储器操控器供给所需求的外部存储器存取的存储器操控信号。

该S3C2440A具有以下特色:

– 小/大端(可选择由软件)

-地址空间:每个bank128Mbytes(共1GB/8bank)

– 可编程拜访的巨细(8/16/32位),适用于一切银行,除了区0(16位/ 32位)

-共8个内存bank

六个内存bankROM,SRAM等。

剩下的两个存储体的ROM,SRAM,SDRAM,等等。

-七个固定内存区的开端地址

– 一个灵敏的存储体的开端地址和可编程bank规划

-对一切存储体的可编程拜访周期

– 外部等候延伸总线周期

– 支撑自刷新和掉电形式的SDRAM

左面的图可知,左面是从nor flash发动,也便是SDRAM,nor flash的地址0x30000000,这便是咱们在之前所以只为什么卸载到0X30000000这个地址中

右边的图可知,右边是从nand flash发动

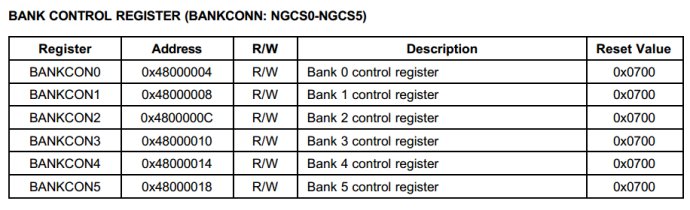

下面开端设定BANK0~5

从上图能够看出,BANKCON0~5坚持默许0X0700,因为SDram是bank6,bank7中,因而不需求设定

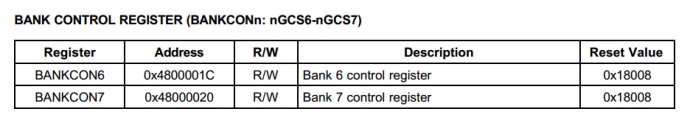

开端设定BANK6~7

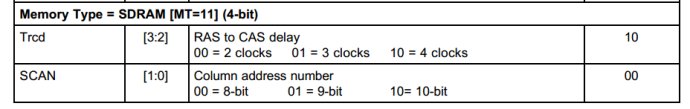

因为运用的是SDRAM,因而对应如下:

也便是0b 11 0000 0000 0000 0001=0x00180001