STM32F103RB有4个IO口(A~D),每个IO口都有7个寄存器控制,他们分别是:端口配置寄存器(32位,共两个,CRL和CRH)数据寄存器(32

STM32F103RB有4个IO口(A~D),每个IO口都有7个寄存器操控,他们分别是:

端口装备寄存器(32位,共两个,CRL和CRH)

数据寄存器(32位,共两个,IDR和ODR)

置位/复位寄存器(32位,一个,BSRR)

复位寄存器(16位,一个,BRR)

锁存寄存器(32位,一个,LCKR)

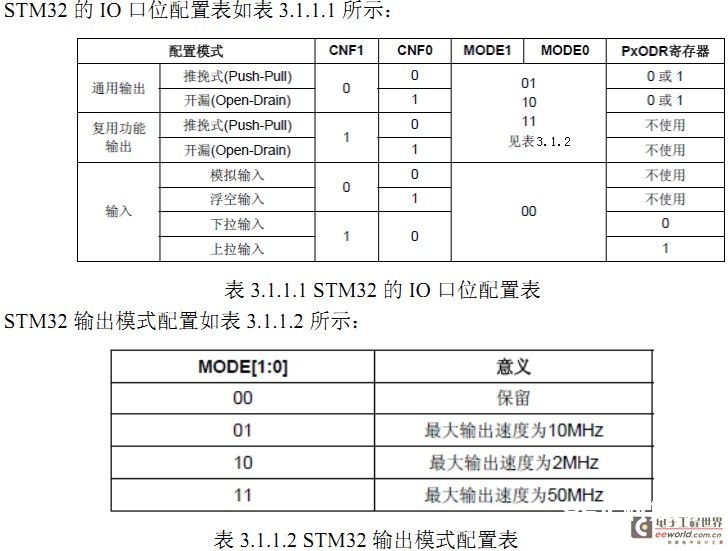

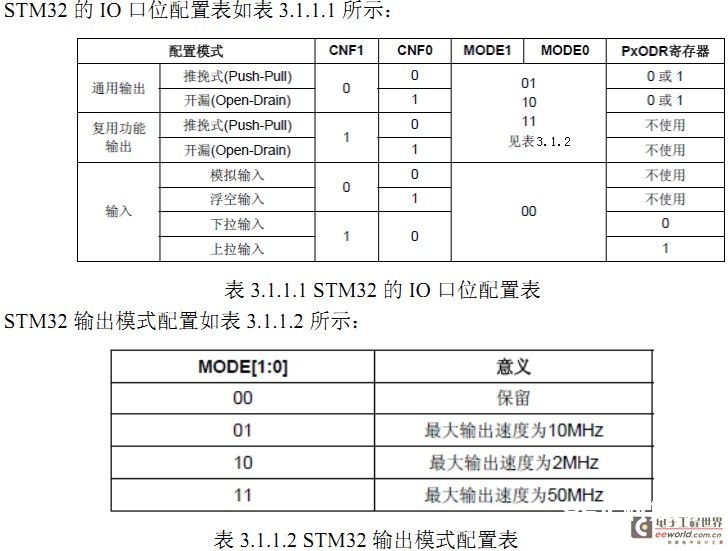

常用的IO寄存器只要四个,即CRL、CRH、IDR、ODR,他们分别是设置IO口作业状况和输入/输出数据的,其间CRL和CRH共2个32位寄存器操控16个IO口的状况(CRL和CRH彻底相同,仅仅CRL操控的是低8位输出口GPIOx(0:7),CRH操控的是高八位GPIOx(8:15)),即每四位操控一个IO口状况(高2位CNF,低2位MODE),寄存器状况如图所示:

常用的状况装备:

0X0 模仿输入形式(ADC用)

0X3 推挽输出形式 (作输出口用50Mhz速率)

0X8 上/下拉输入形式 (作输进口用)

0XB 复用输出 (作IO口的第二功用50Mhz速率) 留意:这个是第二功用即复用输出功用

举例:

咱们乃至PORTC的11位位上拉输入,12位为推挽输出,代码如下:

GPIO->CRH&=0XFFF00FFF; //铲除本来的设置,不影响其他位

GPIO->CRH|=0X00038000; //PC11输入,PC12输出

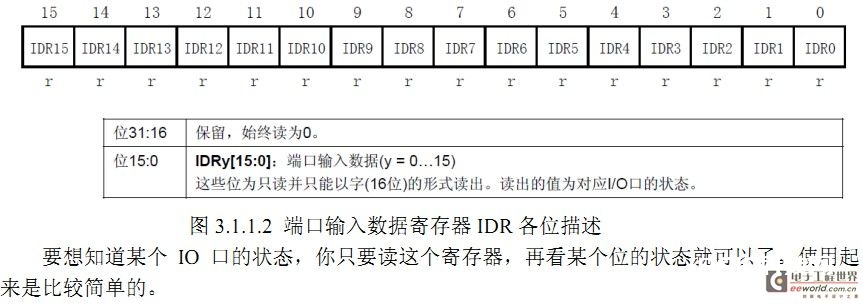

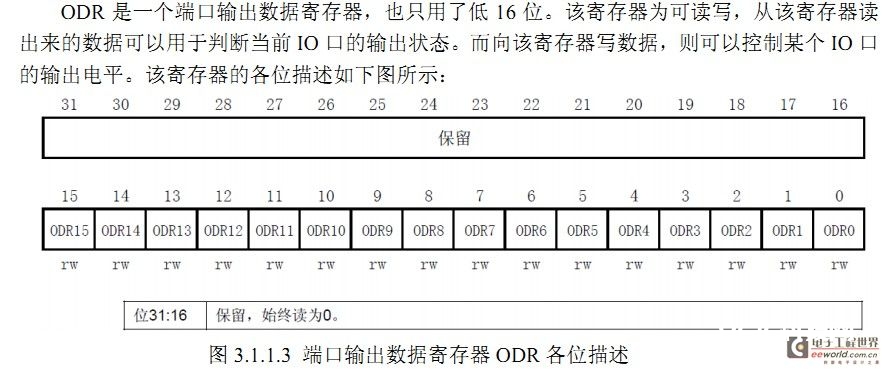

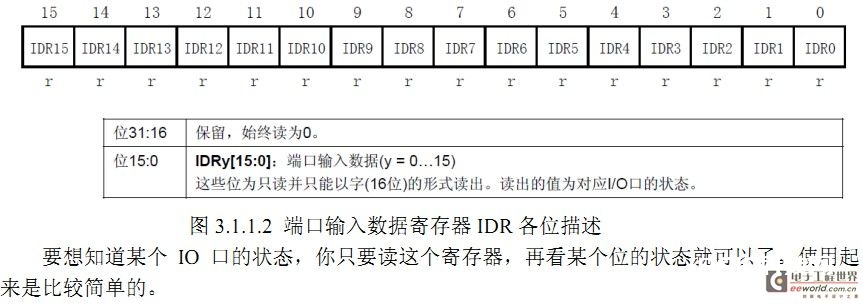

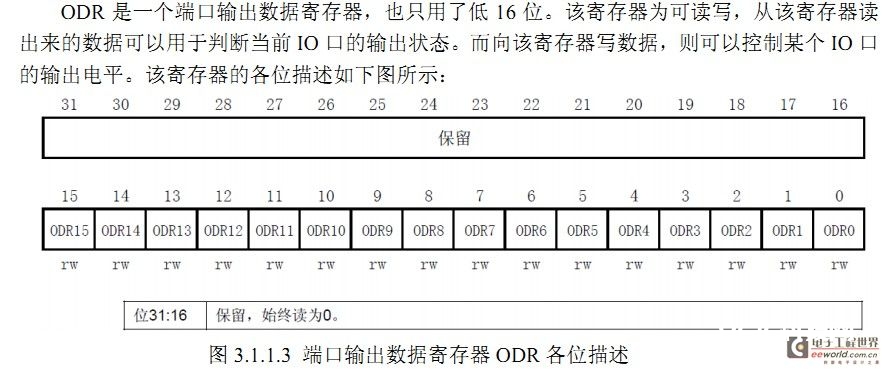

GPIO->ODR=1<<11; //PC11上拉IDR 输入数据寄存器,只使用了低16位,只读寄存器,同理,ODR也只使用了低16位,位可读写寄存器。

IDR寄存器描绘如图:

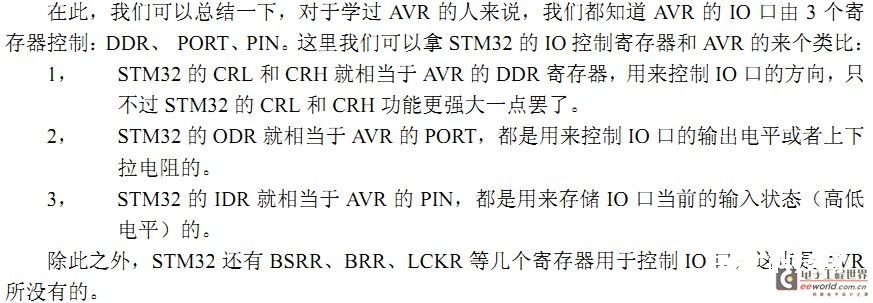

STM32和AVR单片机IO口的比较:

弥补遇到的一个问题:http://www.openedv.com/posts/list/0/378.htm#94993

GPIOA->CRL&=0X000FFFFF; //先将Pin5 6 7 对应的装备为清零,其他位不变

GPIOA->CRL|=0XBBB00000; //PA5.6.7复用推挽输出(50MHz)

GPIOA->ODR|=0X7<<5; //PA5.6.7上拉

PA5-SCLK;PA6-MISO;PA7-MOSI;

第二行中,为什么PA6 也装备为推挽输出呢? PA6 不是应该装备为输入吗 ?

为什么最终还有用GPIOA->ODR|=0X7<<5 装备为上拉呢? ODR寄存器不是只要在输入形式设置上拉或许下拉时才用吗 ?

原子的回答:

1,请留意,这里是复用输出.在复用功用下面,输入输出的方向,彻底由内部操控.不需要你的程序处理.

2,装备为上拉,是常用的设置,这样设置的优点,便是能够让你的IO处于一个电平,而许多时分,外设默许的电平便是高电平的.所以设置为高,是有道理的.

复用功用下,操作ODR是不能输出的!可是ODR是能够操作的,能够设置上拉。