确认PLL 进程:

1.确认 cpu频率

2.确认晶振频率

3.核算M值

4.核算P值

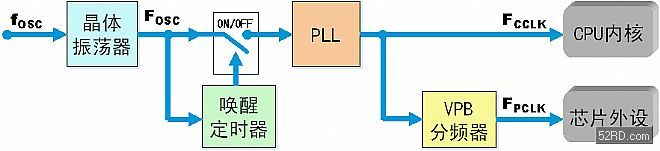

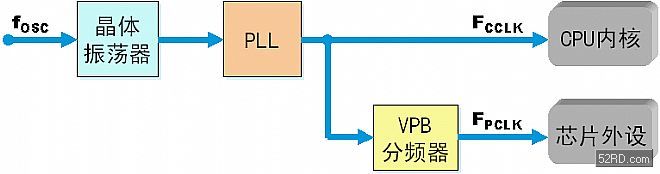

PLL :

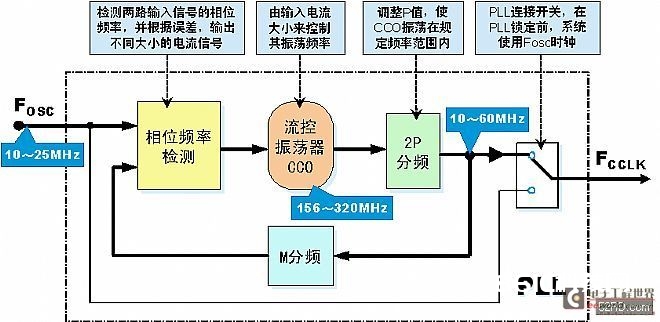

Fcco为PLL电流操控振荡器的输出频率

Fcclk = M×Fosc

相位频率检测:把两个输入的时钟相位差值 ==》

流控震动器:电流值 ==》 频率

当检测输入的两个相同时,安稳了

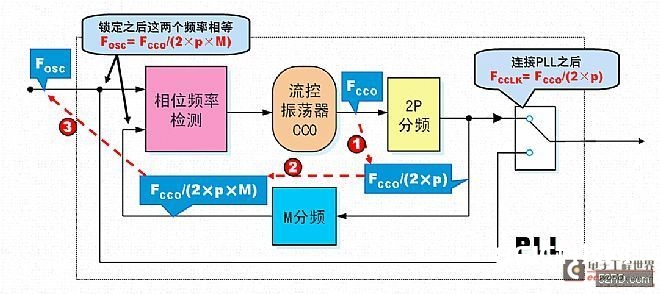

PLL的确认进程:

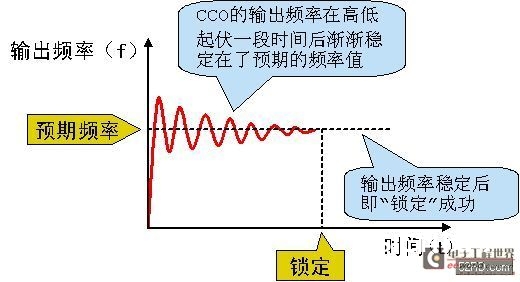

CCO的输出频率遭到“相位频率检测”部件的操控,输出所需频率的进程不是一蹴即至的,而是一个拉锯重复的进程。

举例:

体系要求Fosc=10MHz,Fcclk=60MHz。

- 确认Fcclk=60MHz;

- 挑选Fosc=10MHz;

- 核算M= Fcclk/Fosc=60MHz/10MHz=6。M-1=5,所以写入 PLLCFG[4:0]=00101;

- 核算P=Fcco/( Fcclk*2),其间Fcco为156~320 MHz。当Fcco=156MHz时,P=156MHz/(2*60MHz)=1.3当Fcco=320MHz时, P=2.67