咱们越过一切对ARM介绍性的描绘,直接进入工程师们最关怀的问题。

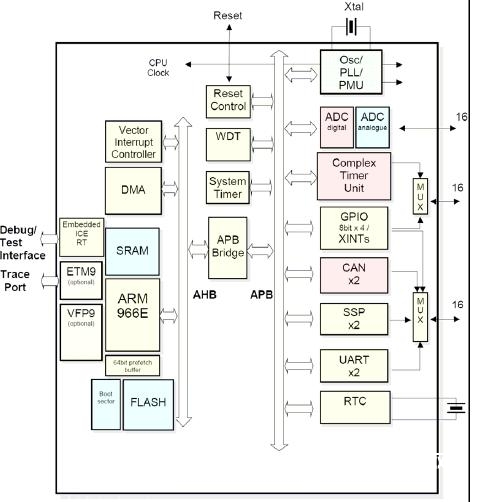

要规划一个根据ARM的SoC,咱们首先要了解一个根据ARM的SoC的结构。图1是一个典型的SoC的结构:

图1

从图1咱们能够了解这个的SoC的根本构成:

- ARM core:ARM966E

- AMBA 总线:AHB+APB

- 外设IP(Peripheral IPs):VIC(Vector Interrupt Controller), DMA, UART, RTC, SSP, WDT……

- Memory blocks:SRAM, FLASH……

- 模仿IP:ADC, PLL……

假设公司现已决议要开端进行一个根据ARM的SoC的规划,咱们将会面对一系列与这些根本构成相关的问题,鄙人面的篇幅中,咱们测验评论这些问题。

1. 咱们应该挑选那种内核?

的确,ARM为咱们供给了十分多的挑选,从下面的表-1中咱们能够看到各种不同ARM内核的不同特色:

表1

ARM现已给出了根本的参阅定见:

- 假设您在开发嵌入式实时体系,例如轿车操控、工业操控或网络运用,则应该挑选Embedded core。

- 假设您在开发以运用程序为主并要运用操作体系,例如Linux, Palm OS, Symbian OS 或 Windows CE等等,则应挑选Application core。

- 假设您在开发象Smart card,SIM卡或许POS机相同的需求安全保密的体系,则需求挑选Secure Core。

举个比方,假设今日咱们需求规划的是一个VoIP电话运用的SoC,咱们这个运用不需求运用到操作体系,所以咱们能够考虑运用没有MMU的内核。其他咱们网络协议盏对实时性的要求较高,所以咱们能够考虑ARM9系列的内核。又咱们VoIP有语音编解码方面的需求,所以需求有DSP功用扩展的内核,所以ARM946E-S或ARM966E-S应该是比较适宜的挑选。

当然,在实践作业中的问题要比这个比方要杂乱的多,比方在上一个比方中,咱们也能够挑选ARM7TDMI内核加一个DSP的处理计划,由ARM来完结体系操控以及网络协议盏的处理,由独自的DSP来完结语音编解码的功用。咱们需求比照不同计划的面积,功耗和功用等方面的优缺点。一起咱们还要考虑Cache size,TCM size,实践的内核作业频率等等相关问题,所以咱们需求的一个能构快速建模的东西来协助咱们决议这些问题。现在的EDA东西为咱们供给了这样的或许,例如Synopsys®的CCSS(CoCentric System Studio)以及Axys®公司的Maxsim®等东西都能够协助咱们完结快速建模,并在硬件还没有完结从前就能够供给一个软件的仿真渠道,让咱们在这个渠道上进行软硬联仿,评价咱们想象的硬件是否分量需求。

2.咱们应该挑选那种总线结构?

在供给内核给咱们的一起,ARM也供给了多种的总线结构。例如ASB,AHB,AHB lite,AXI等等,在界说运用何种总线的一起,咱们还要评价究竟怎样的总线频率才干分量咱们的需求,而一起不会耗费过多的功耗和片上面积。这便是咱们平常常说的Architecture Exploration的问题。

和上一个问题相同,这样的问题也需求咱们运用快速建模的东西来帮咱们作决议。一般,这些东西能为咱们供给笼统等级很高的TLM(Transaction Level Models)模型来协助咱们建模,常用的IP在这些东西供给的库中都能够找到,例如各种ARM core,AHB/APB BFM(Bus Function Model),DMAC以及各种外设IP。这些东西和TLM模型供给了比RTL仿真快100~10000倍的软硬联仿功用,并供给体系的剖析功用,假设体系架构不能分量需求,那么瓶颈在体系的什么地方,是否是内核速度不行?总线频率太低?Cache太小?仍是中止呼应开支太多?是否需求添加DMA?等等,诸如此类的问题,咱们多能够在东西的协助下处理。

当然,机器不是全能的,不要盼望东西能告知你问题在哪里并告知你怎样处理,东西能供给给你的仅仅一些计算的数据,而需求咱们工程师去剖析问题出在哪里并想出处理办法,所以了解AMBA体系结构和ARM内核是十分必要的。

3.怎么挑选外设IP,运用现成的IP仍是自己定制?

运用IP最大的优势是Time to Market,ARM供给了相当多的外设IP供咱们挑选。ARM供给的外设IP集(PrimeCell® IP)包含了常用的绝大部分外设,咱们能够参阅表2:

表2:

PrimeCell®的IP一直在添加,ARM会不定期在网站上发布最新可用的PrimeCell® IP,概况情参阅:

http://www.arm.com/products/solutions/PrimeCellPeripherals.html

ARM除了供给这些IP的RTL之外,还供给这些外设的驱动程序及测验程序。

运用现成IP便利的,但一起也带来灵敏性的约束。举个比方,当咱们需求一个SPI总线接口的时分,咱们应该运用ARM的SSP(Synchronous Serial Interface)这个IP,可是这个IP为了供给能与Motorola SPI,TI SSP,NS Microwire都兼容的功用,献身了片上面积,导致IP杂乱度添加了。假设咱们的运用仅仅是需求和Motorola SPI的规范兼容,那咱们又何须需求一个这样杂乱的IP呢?

自己定制IP尽管得到了灵敏性的优势,可是确需求规划工程师完结自己的一套验证,一起也要为这个IP开发驱动程序,作业添加了许多。我的主张是详细状况详细剖析,在挑选IP的时分也能够考虑第三方公司供给的根据AMBA总线规范的IP,比方Synopsys®的DesignWare® IP库中就有许多根据AMBA规范的IP可供挑选,有时这些IP能够供给比ARM的IP更好的灵敏性并一起运用更少的片上面积和功耗。比方相同是Memory Controller,DesignWare®的DW_memctl就比ARM的MPMC(Multi-port Memory Controller)更灵敏,能够定制更多的参数。关于DesignWare® IP的详细资料,请参阅:

http://www.synopsys.com/products/designware/designware.html

4.自己规划的衔接在AMBA总线上的IP怎么验证?

假设咱们的确要自己规划衔接在AMBA总线的IP,那么了解AMBA的总线规范是有必要的。可是规划往往不是问题,问题是怎么验证咱们的IP能契合一切AMBA规范界说的行为 呢?

作为一个IP的验证,咱们常常会运用所谓的Component-Based Verification,详细做法如图-2所示:

图2

在图2中咱们要验证的是一个USB的IP,这个USB模块直接连到AHB总线上,在咱们的testbench中需求如图中所示的各种VIP(Verification IP),如图中所示的BFM,Bus Monitor,才干够模仿一个USB模块会在实在的总线结构中会遇到的悉数状况。这些VIP能够由EDA vender供给,也能够由工程师自己编写,但一般这些VIP不会运用HDL言语编写,而是运用HVL(Hardware Verification Language)言语。例如:e®, Vera等言语,当然一起也要运用支撑这些言语的东西,如Verisity®的Specman®。咱们体系高速总线(一般是AHB或AXI)上的行为比较杂乱,所以我主张这样的VIP不要由工程师自己开发,而尽量运用EDA vender供给经过了完善测验的VIP。关于低速外设总线(APB)或SPI,I2C,USB等总线,则自己开发BFM模型和Monitor是可行的。

5. 搭建好的渠道怎么验证?

咱们挑选了适宜的ARM core和总线结构,挑选了适宜的IP,然后搭好了积木,TOP完结了,问题也来了,TOP该怎么验证?

关于SoC的验证的确是个大题目,特别是在以IP为根底的SoC规划办法呈现今后,在工程师的规划才能和验证才能中心呈现了真实,也便是咱们能在短时刻内完结规划,却需求化数倍于规划的时刻和人力来验证。最耗费时刻的作业一般来说发生在软硬联仿(SW/HW Co-simulation/Co-verification)的阶段。

咱们知道,笼统级越高的仿真越快,反之越慢,所以假设在咱们的TOP文件中一切的模块都是RTL或Gate level的(包含ARM core),那么仿真的速度是谁也无法承受的,所以实践一点的办法是运用ARM core的DSM(Design Simulation Model)模型。详细办法如图-3所示:

图3

咱们在图3中能够看到,关于内核(Processor)和Memory Controller咱们都运用了运用府第言语编写的行为模型,并在这些行为模型和真实的RTL之间运用PLI(Program Language Interface)言语编写的接口。当然,一切其他外设IP和总线结构都仍是运用RTL(我们咱们便是要验证这些RTL)。DSM模型大多由IP供给商供给,假设运用的是ARM core,当然就由ARM供给了。软件由ARM供给的开发东西(ADS,RealView)编译好,发生bin文件,然后贮存的Memory的模型中。

这时咱们现已能够开端仿真了,ARM的DSM模型会在仿真的过程中发生一个log.eis文件,这个文件次序记录了ARM core从前碑文过的一切指令,经过这个文件,咱们就能够对软件进行debug了。

当然,运用这个文件对软件进行debug是很苦楚的,我们工程师不只不能中止、盯梢、单步碑文软件,更不能运用Semihosting功用进行文件操作和调试信息传递。假设能够运用AXD或Realview Debugger来对软件进行debug将给工程师带来极大的便利,所以EDA公司也推出了相关的产品,例如Mentor Graphics®公司的Seamless®以及咱们前面说到的Axys®公司的Maxsim®等东西都能供给与AXD或许Realview Debugger协同仿真的接口。这样咱们就能够象在方针板上调软件相同在仿真渠道上调试软件了。

在这个笼统等级的仿真速度比纯RTL渠道要快一些,大约能够做到1~100指令每秒的速度。在这样的渠道上进行驱动程序和发动代码验证是可行的,可是假设要进行运用程序的全功用验证,特别是有操作体系的运用,这样的渠道仍是太慢了。比方在这样的渠道上发动一个uClinux™,往往需求化数周的时刻。明显,在这样的速度下验证运用程序仍是不实践的。

处理这个问题咱们有两个个挑选:

(1) 运用硬件加快器

某些EDA vender会供给相关的处理计划,例如Cadence®公司的PALLADIUM® Accelerator/Emulator 和Mentor Graphics®的VStationPRO® Emulation system。这些都是能够加快咱们仿真的加快器,可是一般价格昂贵,所以对大多数的Design House来说,这个办法不光性价比不高,并且也没有必要。

(2)运用FPGA原型进行测验

这个办法关于大多数公司来说是比较实践的。这正是咱们的下一个问题。

6. 怎么完结FPGA原型验证?

完善的FPGA验证对芯片功用验证是十分必要的,一起正如咱们在上一个问题中说到的,要完结完好的功用验证,没有FPGA原型的协助是十分困难的。详细到根据ARM的SoC,咱们能够挑选以下的一些办法:

(1) 由ARM公司供给的Integrator® prototyping board

ARM供给了一套名叫Integrator®开发套版,使工程师能够在这个套版上搭建和规划芯片尽量共同的验证渠道。简略来说,ARM供给了Integrator® CT (Core Tile)来完结相应的ARM Core的功用和行为;运用Integrator® LT(Logic Tile)来完结咱们芯片中除了ARM Core以外的一切数字逻辑(Integrator® LM上有个FPGA),运用Integrator® IM(Interface Module)衔接模仿器材,再把这三个板作为子板通通插接到Integrator® AP(AS%&&&&&% development Platform)。这样咱们就像装电脑相同装出了一个SoC。在这个渠道上,根本上一切的功用验证都能够做到,只需你对频率的要求不是太高(比方在你的运用中ARM core要跑在100MHz),这个渠道是能够完结实时测验的。

(2) 由第三方供货商供给的FPGA验证渠道

例如ALDEC®公司的Riviera-IPT FPGA verification system。这个体系的硬件是一块PCI接口的板卡,这个板卡的中心的一个FPGA,咱们的数字逻辑仍是放在这个FPGA中。一起,在这个母板上能够插上不同的ARM core的Integrator® CM,这样就完结了数字部分的搭建了。这个体系相同能供给与ARM的计划差不多的功用,可是它比ARM的计划有更多一些的灵敏性。

Riviera供给了一个能让ARM core, FPGA中的已归纳逻辑和未归纳的RTL三方协同仿真的功用。这个功用的优点的咱们能够复用本来在作业站环境下仿真时运用的Testbench、鼓励和参阅输出,并能够把RTL象搬积木相同一块一块的搬到FPGA中。也便是说,在开端时一切RTL和Testbench都能够在PC机上进行仿真(当然是运用Riviera供给的仿真器),这时仿真的速度是比较慢的;一旦工程师觉得哪一块的RTL现已OK了,那么他就能够将这一块RTL归纳到FPGA中,跟着越来越多的模块进入FPGA,仿真的速对会越来越快。最终,一切的数字逻辑都归纳到了FPGA中。在RTL仿真和FPGA之间树立交互还有一个优点是在FPGA debug的时分给咱们带来了许多便利。调试过FPGA的工程师常常有着苦楚的回想,咱们FPGA内部的信号不行见,FPGA的debug往往十分耗时,Riviera在供给RTL和FPGA联仿的一起,还能够供给调查FPGA内部信号的功用,相似Xilinx®的CHIPSCOPE。详细资料请参照网页:

http://www.aldec.com/products/riviera-ipt/pages/coverification/

(3) 自己开发FPGA原型板

当然,假设自己规划FPGA原型板,那么工程师就会具有最大的灵敏性,自己的开发板上能够放置任何需求的器材。选用的FPGA能够尽量靠近实践SoC的运转速度,假设有Analog IP对应的Analog器材,那么功用验证的覆盖率将会十分小,最大程度削减投片不成功的危险。这个计划的价值是规划和调试验证板的时刻,有时这个时刻还会超越芯片规划的时刻,一起也需求工程师具有规划高速PCB的相关常识。

ARM core的测验样片是验证板的中心,这个测验样片实践上便是直接将内核拿去流片得到的(当然还要加上必要的PLL)。一般,ARM授权的Foundry会供给这样的测验样片,需求留意的是这个测验样片是否能到达运用所要求的速度,假设不能,那么实时测验将不或许完结。

其他一个需求留意的问题是FPGA的容量。在做AMBA总线结构FPGA归纳的时分工程师会发现以AMBA总线为根底的RTL对FPGA资源的耗费十分惊人,有时一个150K Gate Count的数字逻辑会无法归纳到一个150万门的FPGA中(如Xilinx®的XC2V1500),所以在验证板的规划初期一定要挑选一个留有余量的FPGA(或几个FPGA组成阵列)。