1.stm32的发动文件startup_stm32f10x_hd.s

发动文件是在处理器复位之后最早运转的一段汇编程序。在运转C言语代码之前,需求汇编为C言语树立一适宜的环境发动文件的效果首要分为:

- 初始化仓库指针。

- 初始化计数器指针。

- 设置仓库的巨细。

- 设置反常向量表的进口地址。

- 装备外部的SRAM作为数据存储器。

- 设置C的进口的导入__main、__SystemInit。首要调用SystemInit()装备体系时钟,然后进入咱们在了解不过的main函数。

2发动文件中的体系时钟装备

咱们会发现startup_stm32f10x_hd.s发现这一段汇编代码:

Reset_Handler PROC

EXPORT Reset_Handler [WEAK]

IMPORT __main

IMPORT SystemInit

LDR R0, =SystemInit

BLX R0

LDR R0, =__main

BX R0

ENDP

下面就来剖析下这段汇编代码,待处理器复位从外部导入__main,SystemInit函数,首要是调用的是SystemInit函数。然后会盯梢到System_stm32f10x.c文件。首要咱们剖析c文最开端的代码:

#if defined (STM32F10X_LD_VL) || (defined STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

//#define SYSCLK_FREQ_HSE HSE_VALUE

//#define SYSCLK_FREQ_72MHz 72000000

#else

// #define SYSCLK_FREQ_HSE HSE_VALUE //对应外部晶振不超频(外部晶振是8MHZ)

#define SYSCLK_FREQ_24MHz 24000000 //超频到24MHZ

/* #define SYSCLK_FREQ_36MHz 36000000 */ //超频到36MHZ

/* #define SYSCLK_FREQ_48MHz 48000000 */ //超频到48MHZ

/* #define SYSCLK_FREQ_56MHz 56000000 */ //超频到56MHZ

//#define SYSCLK_FREQ_72MHz 72000000 //超频到72MHZ

#endif

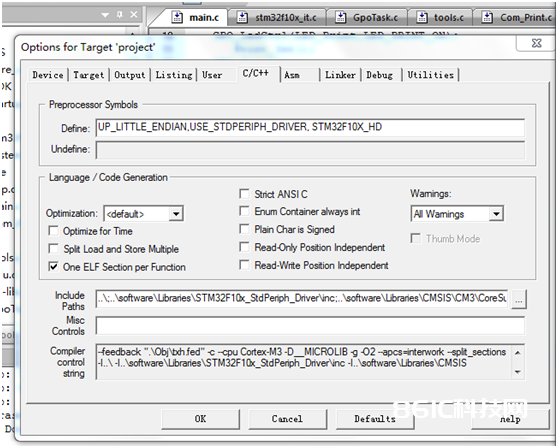

是一段预编译。而这儿正是咱们需求装备时钟的巨细。而界说宏界说变量真实咱们keil里边装备的。如下图

而keil界说的stm32F10X_HD高速的芯片。而此刻#define SYSCLK_FREQ_24MHz 24000000会被编译。(假如说在#id或#else没有界说的变量。默许的会发动芯片内部的HIS高速时钟)在SystemInit函数中又会调用SetSysClock();

static void SetSysClock(void)

{

#ifdef SYSCLK_FREQ_HSE

SetSysClockToHSE();

#elif defined SYSCLK_FREQ_24MHz

SetSysClockTo24();

#elif defined SYSCLK_FREQ_36MHz

SetSysClockTo36();

#elif defined SYSCLK_FREQ_48MHz

SetSysClockTo48();

#elif defined SYSCLK_FREQ_56MHz

SetSysClockTo56();

#elif defined SYSCLK_FREQ_72MHz

SetSysClockTo72();

#endif

}

然后SetSysClockTo24();

#else

/* PLL configuration: = (HSE / 2) * 6 = 24 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLXTPRE_HSE_Div2 | RCC_CFGR_PLLMULL6);

#endif /* STM32F10X_CL */

本规划中外部时钟是选用8M晶振,首要对应RCC_CFGR_PLLXTPRE_HSE_Div2(外部时钟除以8/2=4M)然后RCC_CFGR_PLLMULL6(4*6=24M)这样体系时钟便是24MhZ。这样超频就现已成功。弥补:

RCC->CR |= ((uint32_t)RCC_CR_HSEON); /*敞开外部高速时钟*/

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; /*AHB 分频*/

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1; /*APB2 分频*/

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1; /*APB1 分频*/

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /*挑选PLL作为systick*/

假如咱们外部晶振选用12MHZ咱们能够依据自己的需求修正(RCC_CFGR_PLLXTPRE_HSE_Div | RCC_CFGR_PLLMULL)进行超频到24MHZ.

此刻SystemInit函数调用完毕。下面进入到main()函数。