在电费占运营本钱 (OPEX) 很大一部分,而运营本钱则占总本钱约 70% 的情况下,下降功耗对运营商来说已刻不容缓。曾经,芯片提供商想办法经过晶体管和工艺技能来下降功耗。尽管晶体管是发生功耗的主要原因,但并非仅有要素,并且经过晶体管来下降功耗效果是有限的。

经过更全面的体系级办法可以更有效地下降功耗。只要全面统筹芯片工艺技能,充分发挥功率感知型 (power-aware tool) 东西的效果,在代码规划时即考虑到低功耗需求,调全体系级架构,一起选用可以明显下降体系级功耗的算法(如在长途射频头运用中运用数字预失真 [DPD]),就能取得最佳成效。

挑选适宜的芯片技能合作伙伴将使您收获颇丰。赛灵思正是选用上述全面而体系的办法来处理电源办理问题的,而不是单纯狭窄地注重晶体管和工艺节点技能。Xilinx® FPGA 渠道处理计划能协助规划人员选用功率优化规划计划和体系级规划与集成办法,全面处理功耗问题。从规划层面来说,赛灵思功率感知型东西和广泛的低功耗参阅规划库以及运用攻略都能协助工程师优化全体功耗。此外,赛灵思技能精巧的运用工程师团队还可协助规划人员到达严厉的功耗方针。赛灵思工程师可以协助客户逐渐采纳规划优化技能,如折叠 DSP 密集型规划以缩小规划尺度等,然后运用尺度更小的器材来下降静态功耗和本钱。

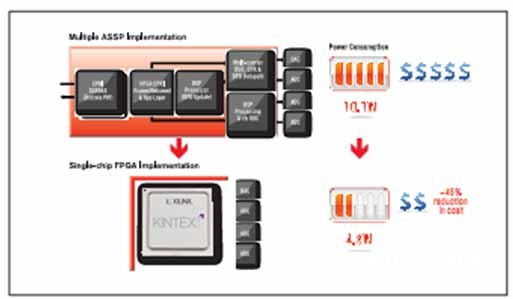

从体系级层面来说,赛灵思对集成度的注重也取得了非常好的成果。例如,在单个 FPGA 上高度集成多个分立组件可以大幅下降体系 I/O 的总量,从而明显下降功耗。此外,在长途射频头中选用 DPD 等高档算法也能使电信设备制造商 (TEM) 运用功耗和本钱均较低的功率放大器,这将对体系级功耗发生巨大影响。

明显,赛灵思认识到不能彻底忽视晶体管和工艺节点技能在下降功耗方面的效果。与其前代 40 纳米系列比较,赛灵思 28 nm 7 系列 FPGA 将整体功耗锐降 50%。在晶体管技能方面,赛灵思的低功耗工艺及其对多种晶体管尺度的运用,可以最大极限地下降静态功耗。赛灵思 FPGA 针对DSP、存储器以及 SERDES 运用硬模块,这与同类竞赛 DSP 和其它 FPGA 规划比较最大极限地下降了动态功耗。

在晶体管层面处理功耗难题仅仅下降功耗和节省运营本钱的一个起点,而只要全面归纳地精细化改善一切相关方面,才干取得最出色的成果。

根据赛灵思 FPGA 的规划可充分利用业界抢先的功用密度和高档无线电算法(如 DPD)来最小化外部电路并下降功率放大器的功耗,然后将整个体系的功耗降至最低。