摘要 在杂乱试验条件下,需选用非易失性铁电存储器记载重要数据。为避免二次上电时试验数据被掩盖,需规划防掉电功用。文中介绍了一种F-RAM的防棹电规划思路,并依据现场可编程门阵列完成,板级验证作业正常,并已在相关项目中得到运用且达到了预期功用。

关键词 非易失铁电存储器;防掉电;现场可编程门阵列

在弹载、密闭舱等某些杂乱试验条件下,为记载试验数据,国内外一般选用SRAM加后备电池、EEPROM、NVRAM的3种办法。其间SRAM加后备电池的办法添加了硬件的杂乱性,一起又下降了体系的可靠性;EEPROM的写操作时刻较长;NVRAM的价格约束了其的遍及运用。鉴于以上状况,越来越多的规划者将注意力投向了新式的非易失性铁电存储器(F-RAM)。非易失性铁电存储器具有实时写入,读写操作简略,可擦写次数可达亿次量级,并具有低功耗等杰出长处。

体系试验中或许会呈现二次上电状况,此刻体系再次正常作业,将向F-RAM中从头写入数据,形成已收集有用数据的掩盖,为避免数据掩盖的产生规划中需添加防掉电功用。本文首要介绍一款F-RAM芯片的硬件装备、读写操作时序,阐明晰防掉电规划思路及其FPGA完成,一起验证了办法的正确性。

1 F-RAM及FPGA

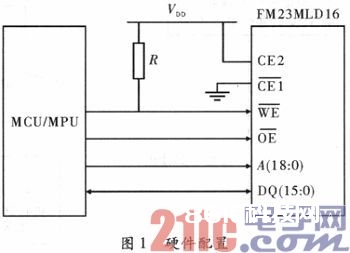

本文挑选FM23MLD16的8 Mbit F-RAM存储器,48个管脚BGA封装,可抗高过载,作为FPGA的外设器材。首要器材装备应正确,硬件装备决议了软件的操控及时序。依据手册,本文挑选如图1所示的装备办法。

硬件上

接为低电平、CE2接为高电平,程序中将UB、LB接成低电平以装备成数据位宽16bit形式。依据硬件装备,读写操作运用

、

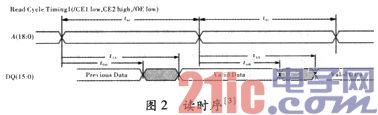

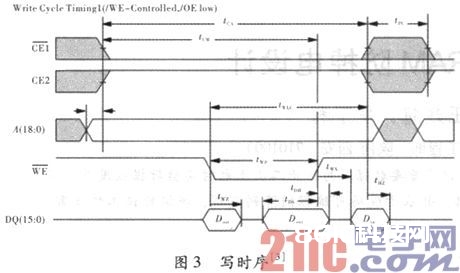

两信号操控,且时序联系确认,如图2和图3所示。硬件装备中需注意的是

上拉电阻务必要参加,以确保在上电及掉电时

信号不为低电平。

规划需满意时序要求,对F-RAM的读写时钟终究确认为5 MHz。由图2可知该装备下,读操作相对简略,

为低,

为高,地址改变即可;写操作需注意

的上升沿与地址、数据间满意树立时刻、坚持时刻要求,文中

的上升沿处于数据中段。

FPGA既具有门阵列的高逻辑密度和高可靠性,又具有用户可编程特性,可削减体系规划和保护的危险,下降产品成本,并缩短规划周期。FPGA有着规整的内部逻辑块阵列和丰厚的连线资源,适合于细粒度和高并行度结构特色的数字信号处理使命,可大幅进步体系处理速度。管脚资源丰厚是选用FPGA完成的重要原因,且时序操控便利。

2 防掉电规划思路

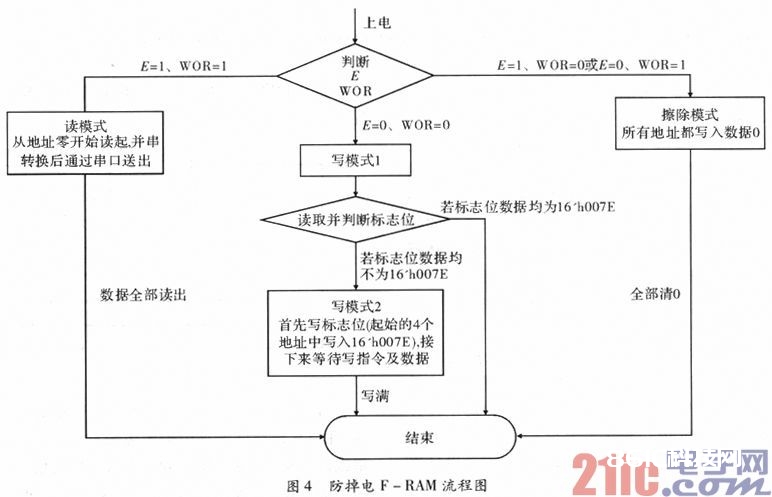

正常的读写操作,在所挑选硬件装备下满意时序要求即可。防掉电功用经过在写形式上电后,首要以判别标志位的办法完成,若标志位未写入标志信息,则履行写操作,不然进入闲暇形式不再写入。而读形式将存储器内数据正常读出即可。规划添加擦除形式,将F-RAM中一切数据清零,且标志位也清零。

读写及擦除形式间的切换是经过两外置管脚的输入电平来操控的,两管脚可完成4种组合满意本文的需求,上电时经过判别管脚电平进入相应形式。其规划流程如图4所示。

图4中E、WOR为两个外置的操控管脚,0、1代表凹凸电平。为数据剖析便利,规划每包数据均加帧头、帧尾标志信息。开端的规划思路为在标志位写固定值,上电写操作形式下先读取该标志位,擦除也仅仅将标志位清零。后经剖析可将帧头作为标志信息,这样大幅简化了规划杂乱度。每包数据帧头均由4个16’h007E构成,将其作为标志位,则写形式下,判别初始4个地址中是否为该标志位即可判别是否已写入数据,完成防掉电功用。擦除形式下将一切存储数据均清为0。每次上电后体系从头判别E、WOR状况,而读写地址均从0开端从头改变。

3 板级验证

因为该器材为FPGA外置芯片,因而读写操作的正确性需在信号处理板上进行调试,规划中的仿真只确保读写时序与规划思路共同。

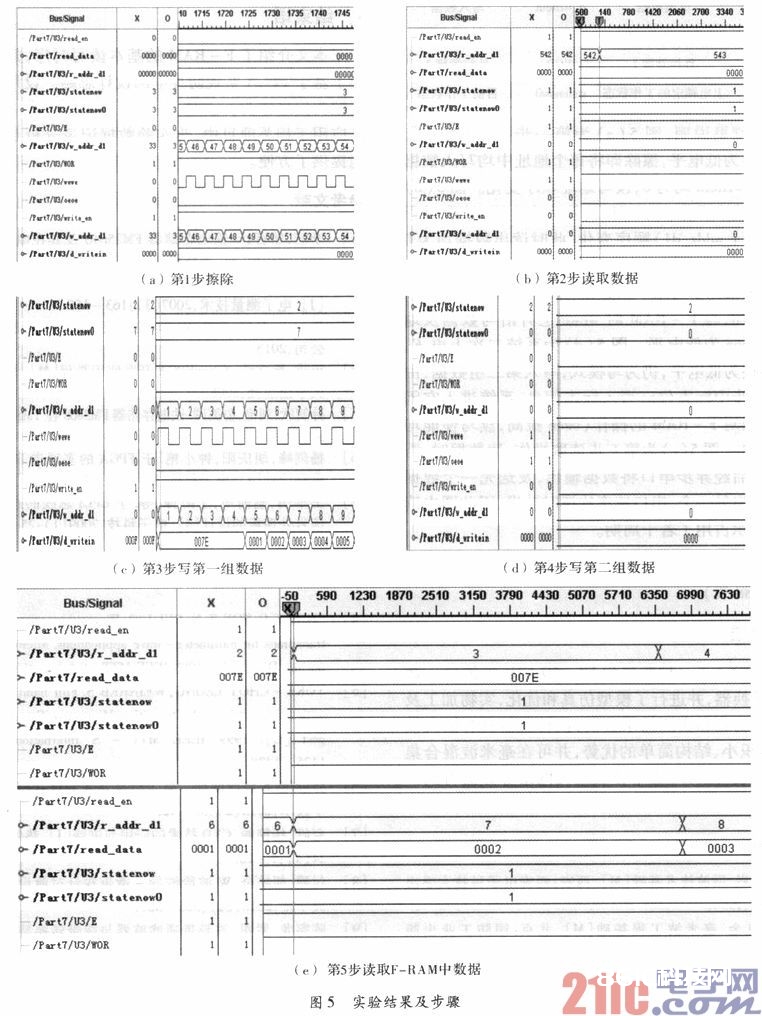

板级验证办法:试验前操控E、WOR为擦除形式,数据清空。再接为写形式,则可正常写入数据,从头上电,仍处于写形式,此刻标志位已写入标志信息,则完毕进入空形式而不再从头写入,最终再进入读形式。具体过程为:(1)进行擦除操作,然后体系掉电。(2)读操作看是否将F-RAM中数据清为0,然后体系掉电。(3)写操作重复写入同一组已知格局的数据(16 bit位宽),本文选用:4个帧头(16’h007E)+数据(16’d 1、2、…、800)+2个帧尾作为第一组数据,写满后体系掉电。(4)二次写操作,仍坚持E、WOR为低电平,此刻每帧数据封装格局不变,将数据调整为800,799,…,1,然后体系掉电。(5)读操作,从F-RAM中读取数据,若为第一组数据则成果正确。试验成果如图5(a)~图5(c)所示,别离对应(1)~(5)步试验过程。

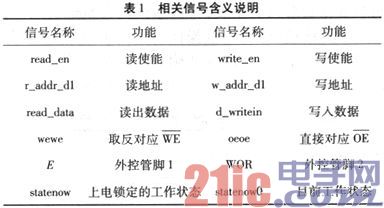

图5为运用同一bit文件观测,图中相关信号的阐明如表1所示。

试验成果阐明,图5(a)为第一步擦除操作,E、WOR均接为低电子,擦除行将每个地址中均写入数据0,对应d_writein均为0,按写地址次序改变。图5(b)为第二步读取操作,E、WOR均接为高电平,读取过程中读地址(r_addr_d1)次序改变,此刻读出数据均为0(read_data),阐明第一步擦除有用已将标志位清零。图5(c)为第三步写第一组数据,如图所示写地址随数据次序添加,写F-RAM时wewe上升沿与数据及地址对齐,oeoe为低电平。图5(d)为体系二次上电E、WOR均接为低电平,仍为写形式,写入第二组数据,因为在第三步中标志位已写入标志信息,体系进入闲暇形式,完毕对F-RAM的操作(oeoe拉高,读写使能均为低电平)。图5(c)为第五步读取操作,读数据时,需并串转化后经异步串口将数据输出,发送完一个数据后将再读出另一个,串口速率比读时钟慢,因而图中读一个数显现占用了若干周期。

图5(c)的成果阐明读出数据为试验第三步即第一次写入的数据,重复验证成果不变,阐明达到了防掉电的意图,且读写功用正常,契合规划要求。

规划中考虑试验时或许遇到的E、WOR线断状况,故给两操控管脚均接入下拉电阻,避免了操控写操作时E、WOR变为高电平,从而避免了误操作的产生。

4 完毕语

本文介绍了F-RAM的根本读写时序,并侧重阐明晰依据FPGA完成防掉电的规划思路。规划运用数据帧头信息作为标志位,简化了逻辑杂乱度。该办法已运用于相关项目中,为试验数据记载剖析及查找问题供给了便利。