光电编码器是许多传感器和自动操控体系的重要部件,可用来丈量位移、速度、加速度等。近年来在研讨和运用方面,不断有所创新和开展。因为光电编码器具有精度高、体积小、重量轻、呼应速度快、牢靠性高、抗搅扰才能强等特色,因此在国防、科研及工业自动化等范畴使用越来越广泛。

在导弹的舵机伺服操控体系中,选用光电编码器作为方位检测设备时,光电编码器固定在电机轴上,并跟从电机同轴滚动。为了减小舵机的体积,选用1个操控器操控4个舵机。舵机操控器选用DSP+FPGA的架构,DSP作为主控CPU,FPGA用于做接口处理。本文以Altera公司的型号为EP3C40F48417的FPGA为根底,选用Verilog言语,规划了可与DSP相连的编码器计数器接口,该接口具有数字滤波、方向辨别、双向计数、复位等功用。

1 光电编码器原理

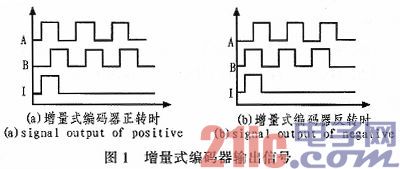

光电编码器依据构成代码办法不同,分为增量式和肯定式两种。肯定式编码器是直接输出数字量的传感器,在任何时间编码器的示值都是仅有固定的;增量式编码器依据中心轴所转过的视点,输出一系列脉冲,典型输出为两个相位相差为90°的方波脉冲信号A、B和基准点定位脉冲信号I。增量式编码器的A、B两路信号的脉冲数标志着编码器所转过的视点,A、B两路信号的相位联系标志着编码器的转向,A相超前B相90°时,编码器正转;A相滞后B相90°时,编码器回转;当I相输出一个脉冲时,表明编码器旋转了一周。增

量式光电编码器输出信号如图1所示。

因为光电编码器的转速随时间或许产生不断改变,所以脉冲周期T很难确认。可是在每个脉冲周期内,A、B两相方波之间的相位联系是确认的。

2 FPGA规划

光电编码器挑选MAXON公司的MR型编码器,旋转一周的脉冲数为500个。舵机的舵偏角规模为±30°,速比为125。编码器A、B两相信号一个周期内信号产生四次改变,编码器旋转一圈对应的计数器值应为2000,所以当舵偏角从-30°到+30°改变时,计数值最大应为41667。FPGA与DSP相连的数据线为16位,最大数值为65536,计数器的初始值为32768,计数存在溢出的或许。所以每逢舵机抵达中心0°时,DSP宣布复位指令,计数器值复位为32768,这样在计数进程中就不会产生数据的溢出。为了减小搅扰,A、B两相信号计数之前要对其进行数字滤波。编码器接口结构图如图2所示。

2.1 数宇滤波规划

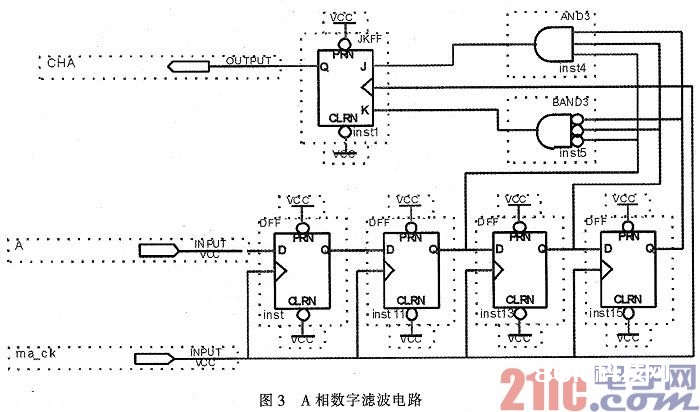

尽管编码器输出信号经过了硬件电路的前期处理,可是大都情况下仍然会产生噪声信号,然后严重影响了计数的精确性,降低了整个体系的精度。为了消除噪声信号,在FPGA内部规划了一个数字滤波器来滤除颤动脉冲,避免计数器的误计数。数字滤波电路如图3所示。

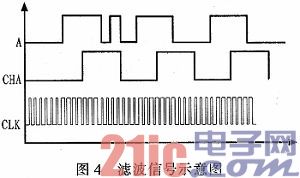

本规划选用4个D触发器、一个JK触发器和一些逻辑电路来完结滤波,原理为:A相信号经过4路D触发器锁存今后产生3路信号,3路信号相与之后作为JK触发器的J端输入,3路信号取反再做与逻辑之后作为JK触发器的K端输入。依据JK触发器的原理核算各个时间的信号输出可知,当搅扰信号频率大于主时钟频率的1/3时,搅扰信号将会被滤除去。如图4所示。A代表有搅扰的编码器信号,CLK为主时钟信号,CHA为滤波之后的编码器信号。

时钟周期的挑选与搅扰信号的脉冲宽的有必定的联系,要依据屡次试验成果确认搅扰信号的频率规模,再结合编码器信号的脉冲频率合理选取,这样才干满意最终的要求,经过试验确认主时钟频率为75 MHz,也就是说25 MHz以上的搅扰信号不会对计数器产生影响。

2.2 计数器规划

完结计数的进程一般有两种办法:一种办法是处理器内部守时计数器完结计数;另一种办法是由可逆计数器完结计数。榜首种办法结构简略,较为简略完结,可是不具有通用性,并且一个处理器上面的接口数量有限,无法对多个编码器一起进行计数。后一种计划使用FPGA完结,具有较好的通用性,功用扩展便利,可以对多个编码器一起进行计数。

增量式编码器依据轴所转过的视点,输出一系列脉冲,经过计数电路,对脉冲进行计数,得到相对的角位移。在脉冲周期T内,A、B两相信号共产生四次改变,在每一次改变时计数器进行计数,这样计数脉冲的周期减小到T/4,然后使光电编码器的角位移丈量精度进步4倍。

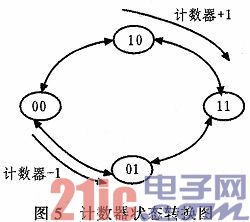

在采样主时钟的下降沿对A、B两相信号进行采样,采样值与前一时间的采样值进行比较来判别计数器的加减。当电机正转时,A相超前B相90°,则在一个周期内,两相信号共有四次相对改变:00→10→11→01→00,每产生一次改变,计数器便完结一次加计数,一个周期内共可完结4次加计数,然后完结正转状况下的四倍频计数。当电机回转时,A相滞后B相90°,则在一个周期内,两相信号共有四次相对改变:00→01→11→10→00,每产生一次改变,计数器便完结一次减计数,一个周期内共可完结4次减计数,然后完结回转状况下的四倍频计数。当没有状况转化时,计数器不进行计数。如图5所示。

选用D触发器来进行旋转方向的判别,B相信号作为时钟输入,在B相信号的上升沿采样A相信号的状况,当输出为高电平时,A相超前B相,表明电机正转;当输出为低电平

时,A相滞后B相,表明电机回转。

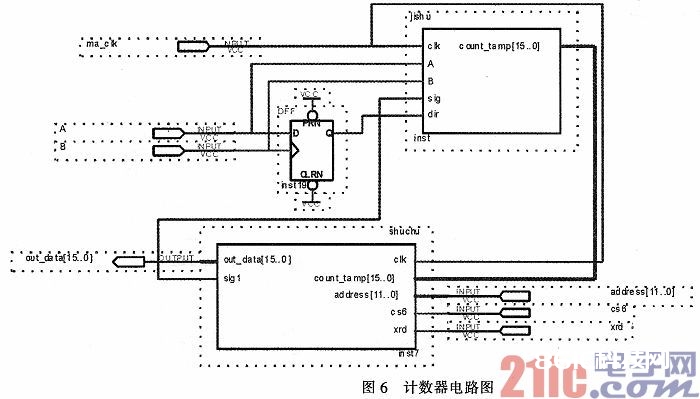

FPGA与DSP之间经过16位数据线、12位地址线,片选信号、时钟信号和读写信号线相连。地址线上面不同的数据代表DSP对FPGA的不同操作,地址线协议如表1所示。计数器电路如图6所示。

3 试验成果

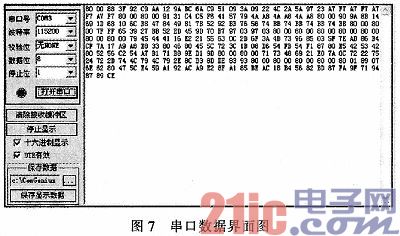

在试验室条件下,DSP经过串口将计数值发送到核算机上,选用十六进制表明,串口协议如下:发送周期为10 ms,波特率为115200kbit/s,无校验位,8位数据位,1位中止位。成果如图7所示。

经过串口宣布的数据可以看出,计数器的初始值为32768(十六进制为8090)。当电机正转时计数器添加,当电机回转时计数器削减,当电机中止旋转时,计数器坚持当时数值。可以依据DSP宣布的复位指令,计数器复位到初始值32768。DSP和FPGA作业正常,DSP经过片选信号和读信号可以实时的读取计数器的数值,可以满意电机操控的要求。

4 定论

从以上可以看出,使用FPGA规划光电编码器的接口电路,削减了体系芯片的数量,仅用一片芯片即可完结整个体系的规划,降低了体系的功耗,缩小了体系的体积,进步了体系的牢靠性和抗搅扰才能,用Verilog规划电路,只需要修正程序句子即可,进步了体系维护和晋级的快捷性。本文的规划办法结构简略,无溢出,无误码,可以精确的检测码盘方位的改变,运转牢靠,可以与DSP相连。