因为当时国税、地税、各省、各税种发票不同,区分难度较大,因而给造假者待机而动。本文规划的依据FPGA的税控算法加密卡可有用地处理上述问题,供给了高效的防伪办法。该加密卡经过PCI总线内置于税控加密机中,将发票上的数据加密成一组防伪码,打印在相应的区域上,因为选用国家暗码办理局的高安全性税控暗码算法芯片,因而发票难以被篡改,然后可满意税务机关对发票办理和身份认证的要求。

1 体系整体架构规划

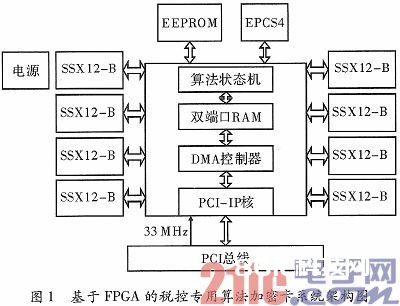

图1是依据FPGA税控算法加密卡的体系架构图。其间包含FPGA芯片、8片税控暗码算法芯片SSX12-B、FPGA装备芯片EPCS4、存储器EEPROM和电源芯片。

FPGA是整个加密卡的操控中心,在其内部使用嵌入式PCI—IP核完结与物理32位PCI总线的通讯;规划算法状况机模块完结了FPGA与8片税控暗码算法芯片的数据交互;别的,规划了DMA操控器和双端口RAM完结了数据的传输及存储。PCI总线的时钟信号33 MHz作为FPGA的主时钟。此外,33 MHz时钟也作为SSX12-B芯片的作业时钟,整个体系选用了时钟彻底同步的规划方法。EPCS4芯片与FPGA相连,每次上电后FPGA需读取EPCS4内的程序进行加密卡的装备与初始化。EEPROM用于存储体系密钥等要害参数。

数据运算的进程如下:

(1)经过上位机软件设置好运算指令字和待运算的数据包,FPGA依据指令字可指定一片SSX12-B作业或多片SSX12-B一起作业。

(2)发动数据传输,将数据包经过PCI总线传入FPGA的双端口RAM。RAM由8个1 kB的RAM单元构成,每个RAM单元对应一个SSX12-B的数据缓冲区,RAM单元和SSX12-B的数据总线宽度均为8 bit,整个RAM的容量为8 kB,数据总线宽度为64 bit。

(3)待一切数据包传输到对应的RAM单元后,FPGA设置相关进程,发动算法状况机,将数据包并行传送给RAM单元对应的SSX12-B芯片。

(4)各SSX12-B芯片一起开端作业,此刻FPGA等候运算的完结。

(5)各SSX12-B芯片运算完结后在算法状况机的操控下将数据包传回到对应的RAM单元。待一切数据包传完后状况机发生中止信号,之后FPGA经过PCI总线将数据包传回到上位机,至此完结了一次数据运算进程。

2 首要芯片选型

(1)FPGA芯片。选用美国Altera公司CycloneⅢ系列的EP3C16F484C8器材,该芯片总引脚数为484,其间I/O引脚为346,RAM总量为63 kB,逻辑单元(LE)15 408个,可满意加密卡的规划要求。FPGA的开发东西选用Altera公司的EDA软件Quartus II9.1,其可完结归纳、仿真、布局布线、体系调试等功用。

(2)税控暗码算法芯片。选用国家暗码办理局的税控暗码算法芯片SSX12-B,该芯片专用于税控等信息安全范畴,功用首要有数据加密、解密、生成收据防伪码等,有用确保了用户进行买卖时数据的安全性。

其首要特色为:每片算法芯片均有各自独立的ID,一切加密运算均在片内完结,运算速度快且安全性高。

(3)FPGA装备芯片。选用Altera公司的EPCS4芯片,该芯片用以存储加密卡的装备程序。加密卡每次上电后,FPGA首先从EPCS4里加载程序。

(4)EEPROM。选用Microchip公司的24LC512I2C串行总线EEPROM,容量为64×8 kbit,8脚SO%&&&&&%封装。100万次的擦写周期,数据坚持时刻>200年,最大5 ms的写入周期。此芯片首要用于存储加密卡的密钥等要害数据。

3 数据传输模块

规划了FPGA的DMA操控器和双端口RAM作为数据传输模块。DMA传输关于高效能嵌入式体系算法和网络是要害,其答应不同速度的硬件设备进行交流,而无需依靠CPU的很多中止负载。不然,CPU需求从来历将每一片段的材料复制到暂存器,再写回到新的当地,在这段时刻中CPU无法参加其他作业。DMA传输的重要作用是将一个内存区从一个设备复制到另一个。当CPU初始化DMA传输后,传输动作自身由DMA操控器履行。

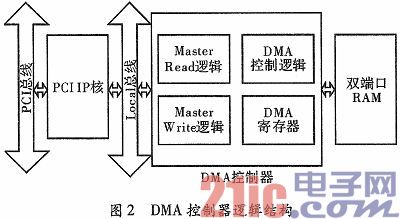

如图2所示,DMA操控器包含Master Read逻辑、Master Write逻辑、DMA操控逻辑和DMA寄存器。Master Read逻辑完结数据由上位机到加密卡的传输;Master Write逻辑完结数据由加密卡到上位机的传输;DMA操控逻辑完结传输的操控功用;DMA寄存器包含操控状况寄存器CSR、地址计数寄存器ACR、字节计数寄存器BCR、中止状况寄存器ISR和本地地址计数寄存器LAR。在完结DMA传输时,由DMA操控器直接掌管总线。因而,存在一个总线操控权搬运的问题。即DMA传输前,CPU要将总线操控权交给DMA操控器,而在完毕DMA传输后,DMA操控器应立即将总线操控权再交回给CPU。一个完好的DMA传输进程包含DMA恳求、DMA呼应、DMA传输和DMA完毕4个进程。

DMA操控器完结数据传输的具体进程如下:

(1)上位机设置待传输的数据包,并顺次设置CSR、LAR、BCR和ACR寄存器,并对DMA操控器初始化。

(2)上位机发动DMA读(Master Read)的进程,将数据包一次性传入税控加密卡的双端口RAM。

(3)DMA操控器发动算法状况机模块,操控暗码算法芯片SSX12-B一起作业。

(4)暗码算法芯片SSX12-B完毕作业后,将运算完结的数据传回到相应的双端口RAM存储单元。

(5)DMA操控器设置ISR和CSR寄存器,发动DMA写(Master Write)的进程,将运算完结的数据包传回到上位机。

双端口RAM的作用是缓存数据,其供给2组独立的数据读写端口。因而,上位机和FPGA可对RAM进行独立的拜访,使规划愈加灵敏。

4 暗码算法状况机模块

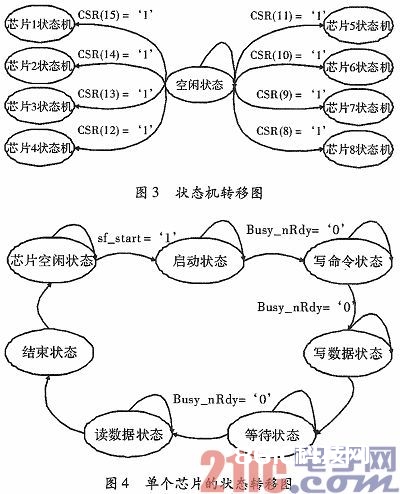

状况机是数字时序逻辑中重要的规划内容,经过状况搬运图规划手法可将杂乱的操控时序图形化表明,分解为状况之间的转化联系,将问题简化。算法状况机模块完结对SSX12-B芯片的时序操控。状况机的状况搬运图如图3所示,由上位机软件经过设置CSR寄存器相应位的值发动对应的暗码芯片作业,FPGA依据CSR寄存器可发动多片SSX12-B一起并行作业。单个芯片的状况搬运图如图4所示,由闲暇状况、发动状况、写指令状况、写数据状况、等候状况、读数据状况及完毕状况组成。对各状况的编码选用格雷码的方法,可有用地避免毛刺的发生,使体系安稳。

算法状况机的规划是经过FPGA的硬件描绘言语VHDL完结的,单个芯片的状况机具体作业进程如下:

(1)算法开端信号sf_start=‘0’时状况机一直处于闲暇状况。(2)上位机设置CSR寄存器相应的位后,FPGA使sf_start=‘1’,状况机进入发动状况。(3)当状况机检测到芯片处于不忙的状况时,即SSX12-B芯片的Busy_nRdy引脚为低电平,状况机进入写指令状况。(4)在写指令状况,FPGA将相应的指令字写入SSX12-B芯片,Busy_nRdy=‘0’时进入写数据状况。(5)在写数据状况,FPGA将待运算的数据包顺次写入SSX12-B芯片。(6)状况机进入等候状况,等候SSX12-B芯片的运算完结。(7)当检测到Busy_nRdy引脚为低电平时,状况机进入读数据状况,并将运算完结的数据传回到对应的RAM单元。(8)待本次运算的数据读取完毕,状况机进入完毕状况,至此完结了一次数据运算进程。(9)之后状况机回来闲暇状况,等候下一次数据运算恳求的到来。

5 体系作业进程

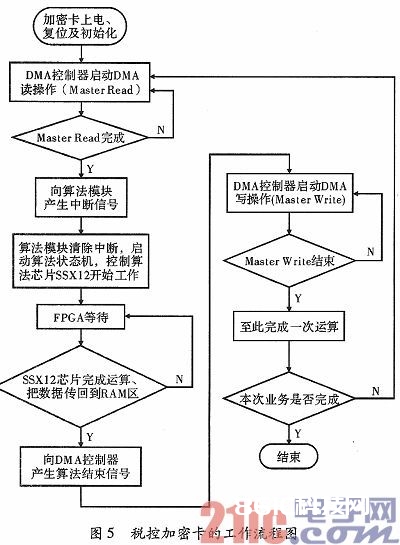

税控加密卡的一次事务一般包含屡次运算进程的组合。例如生成一次收据防伪码的事务包含自检、生成非对称密钥对、读入签名密钥密文、读入账户密钥密文等运算进程。图5是税控加密卡的事务流程图,具体作业进程如下:

(1)税控加密卡上电、复位及初始化完毕后,上位机对DMA操控器初始化,其间包含设置待传送的数据包,设置DMA相关的寄存器,供给要传送数据的开端方位和数据长度。

(2)DMA操控器对DMA恳求判别优先级及屏蔽,向总线判决逻辑提出总线恳求。当上位机CPU履行完当时总线周期即可开释总线操控权。此刻,总线判决逻辑输出总线应对,表明DMA已呼应,经过DMA操控器告诉加密卡开端DMA传输。

(3)DMA操控器获得总线操控权后,上位机CPU立刻挂起或只履行内部操作,由DMA操控器输出读指令,直接操控内存区与加密卡的双端口RAM进行DMA读操作(Master Read)。此刻,数据包经过PCI总线顺次传入到双端口RAM的相应地址单元。

(4)Master Read完结后,DMA操控器向算法操控模块发生中止。算法操控模块收到中止后将其铲除,之后发动算法状况机进程。状况机进程读取双端口RAM中的数据,再将数据传送到外部的算法芯片SSX12-B。

(5)SSX12-B芯片开端并行作业,此刻FPGA等候运算完结。

(6)SSX12-B芯片将运算完结后的数据包传回到相应的RAM地址单元,之后算法操控模块发生完毕信号,DMA操控器收到此信号后设置相应的进程,并发动DMA写操作(Master Wr ite),将数据包经过PCI总线传回到上位机。

(7)当完结DMA写操作后,DMA操控器开释总线操控权,上位机CPU从头获得总线的操控权并履行一段查看本次DMA传输操作正确性的代码,至此完结一次运算。

(8)依据上位机的指令顺次处理屡次运算,如生成非对称密钥对、读入签名密钥密文、读入账户密钥密文等,直至完结生成收据防伪码或数据加解密的事务。

6 试验成果剖析

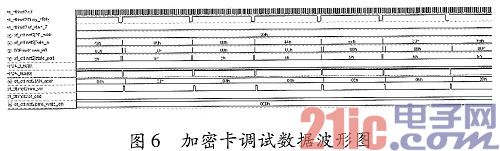

整个规划在Quartus II 9.1软件中先后完结归纳、功用仿真、布局布线后,经过逻辑剖析仪SignalTap并结合上位机软件进行了调试。除掉SignalTap,FPGA的终究编译成果是:占用存储单元15.75 kB,逻辑单元4 950个。参加SignalTap编译后占用FPGA的存储单元为37.8 kB,占用率为60%,因为资源充裕较大,所以参加SignalTap调试对体系的数据成果不会形成影响。FPGA各模块的时钟信号同步于33 MHz时钟,选用了彻底同步的方法进行规划,从理论上经过优化FPGA的电路结构可满意信号的树立、坚持时刻要求。

终究使用Quanus II的时序剖析东西TimeQuest对体系的时序进行了剖析,测得最高时钟频率>46.01 MHz,一切信号的树立、坚持时刻无违规途径。

图6是在SignalTap中调试经过的波形图,图中显现了单芯片生成收据防伪码及将数据写到双端口RAM的进程。Busy_nRdy信号是SSX12-B芯片的状况引脚,高电平表明芯片正在运算中,低电平表明输出数据有用;FPGA_i_nD[0]信号是SSX12-B的指令/数据引脚,高电平表明数据总线上是指令,低电平表明数据总线上是数据;FPGA_nLE[0]是SSX12-B的数据总线状况引脚,低电平表明总线上的数据有用,高电平表明总线为三态;Data_in信号是SSX12-B输出的数据:73h是应对字,09h是回来的有用数据长度,00h表明无过错,44 h,E7h,33h,FEh……是生成的8 Byte防伪码;ram_wr是双端口RAM的写信号,WR_addr是双端口RAM的写地址线,ram_in0是RAM的数据输入端口,dma_write_len表明写入的数据长度,图中显现了SSX12-B在输出收据防伪码数据的一起状况机将数据写入到了双端口RAM,WR_addr地址顺次递加,state_port是状况机的状况改变信号。

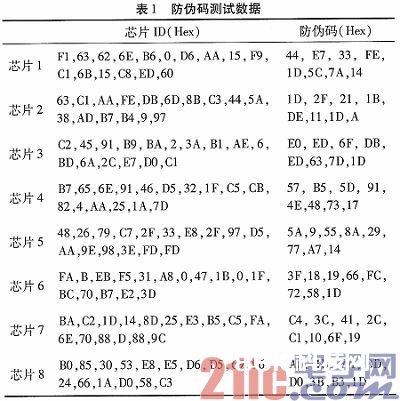

表1是在不带有SignalTap的加密卡上测得的8片SSX12-B芯片生成的防伪码数据,其与带有SignalTap的加密卡测得的数据相一致,且生成的防伪码经核验服务器核验后均是正确的防伪码数据。

加密卡的驱动程序依据Linux2.6内核开发,API接口程序和上位机软件是在RedHat Linux AS4.6环境下开发完结的的。最终对加密卡生成收据防伪码的功能进行了测验,在程序中设置8片暗码算法芯片SSX12-B一起并行作业,经过10 000次循环测验,测得生成收据防伪码的速度为827次/s。经过压力测验加密卡作业安稳,且生成数据正确。

7 完毕语

规划了一种依据FPGA的税控算法加密卡,介绍了各模块的规划,经过FPGA完结了对税控暗码算法芯片的高效操控。该加密卡具有加密速度快、效率高、功耗小的长处,经过PCI总线内置于税控加密机中,可确保发票数据的正确加解密及生成发票数据防伪码,满意了税务部门对发票办理的要求。