摘要:在某归纳操控计算机体系中为了完结对多路AD信号实时高精度收集,选用了以TMS320C6713B为中心,与AD7656芯片相组合的高精度、实时A/D数据收集砹计完结计划。要点剖析硬件接口电路的规划、PCB规划中应留意的问题和软件规划完结流程。经过体系联试等多方验证,该规划计划实时性强,精度高,满意某归纳操控计算机体系的性能指标要求。

关键词:TMS320C6713B;AD7656;接口电路

0 导言

为完结对某归纳操控计算机对整个归纳操控体系作业状况的实时状况监控以及毛病检测,在规划中考虑到归纳操控体系对监测信号精度和实时性要求较高,模仿量收集模块规划中选用了AD7656作为模/数转化芯片,该芯片支撑6路通道,可同步进行模数转化,A/D转化输出可到达16位。数据处理和操控选用TI公司的TMS320C6000系列的高速32位浮点DSP芯片TMS320C6713B,该芯片经过EMIF总线接口完结对AD7656拜访。

1 芯片介绍

1.1 TMS320C6713B首要特色

TMS320C6713是美国德州仪器公司(TI)推出的一款浮点32位DSP芯片,依据高性能、先进的VelociTI超长指令字体系结构,该芯片的内部结构包含如下特色:

(1)处理速度快,作业主频最高可到达200MHz,峰值运算才能为1800MIPS/1350MFLOPS450MMACS;

(2)具有8个功用单元的高档VLIW体系结构CPU,集成2个乘法器和6个ALU,指令打包削减代码数量;

(3)集成了32×32比特的乘法器,其成果可为32bit;

(4)片内存储器选用两级高速缓存结构,包含4KB的榜首级高速程序缓存器(L1P)、4KB榜首级高速数据缓存(L1D),第二级共256KB内存储容量(64KB的L2一致缓存/映射RAM,192KB的附加L2RAM);

(5)32位外部存储器接口(EMIF总线接口),无缝接口到SRAM、EPROM、FLASH、SBSRAM和SDRAM。

1.2 AD7656模数转化器

1.2.1 AD7656特色

AD7656是美国模仿器材公司(ADI)公司推出的一款选用iCMOS工艺制作的高集成度、6通道16位SAR型ADC,该器材具有4LSB(INL),每通道达250kSPS的采样速率,内置一个2.5V内部基准电压源和基准缓冲器。该芯片功耗仅为160mW。AD7656特色如下:1)供电电源电压:5V,±15V;2)可经过装备挑选模仿量输入电压规模-10V~10V或-5V~5V;3)片内集成2.5V基准电压源和基准缓冲器;4)通道可同步采样,采样速率可达250kSPS;5)支撑并行和高速串行接口拜访。

1.2.2 AD7656的原理及结构

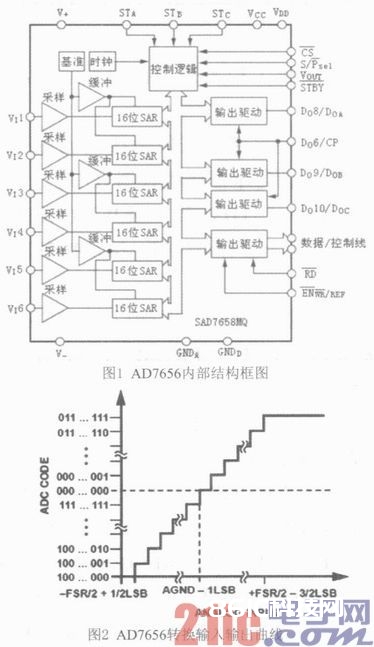

AD7656的内部结构见图1所示,AD7656内置时钟电路,外部模仿量信号从VI引脚输入,经过一个高带宽的线性跟从器(T/H)单元进行采样,确保满量程的输入正弦波时转化精度到达16位。AD7656处理的最高频率为8MHz;经过AD7656中心单元16位SAR转化,将模仿信号转化为数字信号,经过操控逻辑单元,将数字信号输出驱动。

AD7656的模仿信号输入采纳了单端输入方法,输入信号的电平规模为两种±10V和±5V,可经过两种方法挑选输入信号电平规模,硬件上经过RANGE管脚设置,软件上经过装备操控寄存器的RNGX位来挑选。

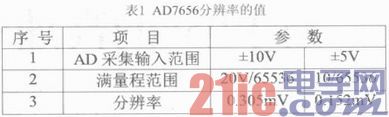

AD7656的转化后输出的数据格式见图2所示,分辨率与输入信号的规模设置有关,详细分辨率值见表1所示。

2 模仿转化电路规划

2.1 AD7656前端调度电路

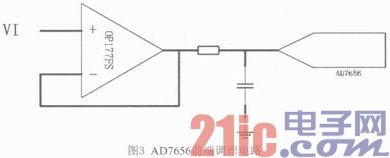

因为在归纳操控计算机收集的信号源与AD7656要求的输入信号不匹配,所以对信号源的信号进行前端调度电路调整,在AD7656前端调度电路规划首要考虑了如下要素:

(1)阻抗匹配。因为输入信号的信号源纷歧定是低阻抗,AD7656的输入端很可能会对信号源信号分压,然后影响收集转化信号的精度。在AD7656前级输入选用运算扩大缓冲器处理该问题,因为运算扩大缓冲器具有很高的输入阻抗,因而不会对信号源分压,一起它的低输出阻抗合适驱动AD7656的输入端;

(2)减小容性负载的影响。AD7656输入端具有容性负载特性,一般需求一个电阻和电容组成外部补偿电路,选用该电路给信号源增加了容性负载。

AD7656前端调度电路规划见图3所示。AD7656前端调度电路选用的运算扩大缓冲器为ADI公司的OP177FS,其具有低输入失调电压(25μV),失调电压时刻漂移最大0.1 μV/℃,开环增益最小12V/μV,电源电流2.0mA。

2.2 AD7656与TMS320C6713B接口电路规划

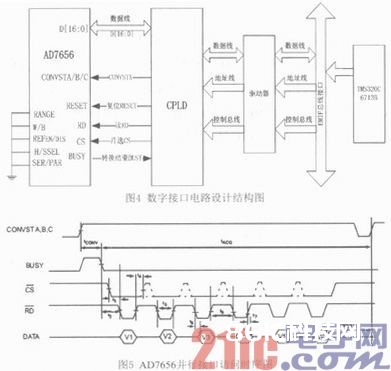

AD7656与TMS320C6713B接口电路采纳并行接口规划。在电路规划时将AD7656的“SER/PAR”管脚设置为并行接口方法,“W/B”管脚设置为字方法,“H/S SEL”管脚设置为硬件发动转化方法。TMS320C6713B经过外部存储器接口(EMIF)总线完结对AD7656拜访,发动对AD7656转化,读取转化成果数据,接口电路结构图见图4所示。

TMS320C6713B经过CPLD完结对AD7656操控逻辑译码,来满意AD7656的拜访时信号的逻辑要求,AD7656拜访时序图见图5所示。

AD7656包含6通道ADC转化,可完结6通道ADC同步转化,削减了多路ADC转化采样时刻。在CPLD逻辑规划中选用一起操控“CONVSTA”

“CONVSTB”“CONVSTC”管脚输出有用完结6通道ADC通道同步转化。

依据图5所示AD76565经过“CONVSTA,B,C”信号的上升沿发动ADC转化,ADC转化过程中,“BUSY”信号为逻辑“高”标识,ADC正在转化过程中,ADC转化时钟由内部时钟发生,从“CONVSTA,B,C”信号的上升沿发动转化3 μs后ADC转化完毕,“BUSY”信号为逻辑“低”表明ADC转化完毕。TMS320C6713B经过EMIF总线接口完结对转化成果的读取。对AD7656芯片转化成果读取,经过“CS”片选信号和“RD”读信号操控,6个通道转化完毕后,TMS320C6713B操控“CS”为有用和6个“RD”读有用信号,完结对模仿量输入“V1”信号、“V2”信号、“V3”信号、“V4”信号、“V5”信号、“V6”信号转化成果的读取。

2.3 AD7656规划中应留意问题

2.3.1 电压基准电路规划

因为AD7656转化的精度与参阅电压基准电压的精度有很大联系,参阅电压基准输出电压值用来确认数据转化体系的满量程输入规模,一起参阅电压基准电压的任何差错都会严重影响ADC的线性和无杂散动态规模。

因为AD7656内部集成的电压基准参数精度低,一般在关于分辨率大于12位的ADC使用中选用高精密外部电压基准,本规划选用高精密外部电压基准AD780BR作为AD7656转化的电压基准。经过表2对两种电压基准参数比较,看出外部高精密电压基准精度高,具有更低的温度系数、热迟滞和长时间漂移。

3 PCB规划

3.1 数\模区域切割

在高速AD收集电路的规划中,到达高精度与PCB规划是密不可分的,所以进行PCB规划过程中,依照电路完结的功用能够简略地划分为数字电路和模仿电路两部分,将数字区域与模仿区域进行切割,构成每个区域的独立电源和地,这样能够有用按捺干与的传导和RF能量的辐射。

AD7656芯片在管脚界说时将模仿量和数字量信号按区域界说,有利于PCB规划中数字量和模仿量区域切割,布线时留意模仿信号区域布模仿信号线,数字信号区域布数字信号线,不要将数字信号线和模仿信号线并行布线。

在本体系中模仿地和数字地选用一个电势参阅点,所以模仿地和数字地选用单点共地,共地址尽可能地接近AD7656。

3.2 电源去耦规划

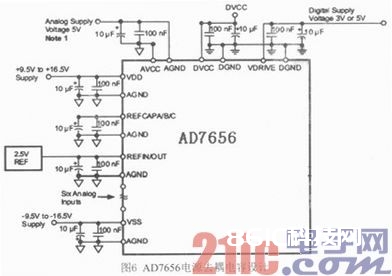

因为AD7656芯片存在多个电源管脚,在每个电源管脚需求连接去耦电容。去耦电容的规划中选用并联100nF和10 μF电容。电容挑选时可选用具有小等效串联电感(ESL)瓷介质电容。AD7656的去耦%&&&&&%规划见图6所示。

4 AD收集软件规划完结

TI公司供给杰出的C/C++编译器,在TMS320C6713B软件敞开过程中支撑C/C++言语规划。而且供给的杰出的库函数(DSPLIB),支撑TMS3 20C6713B的数学运算和矢量运转。

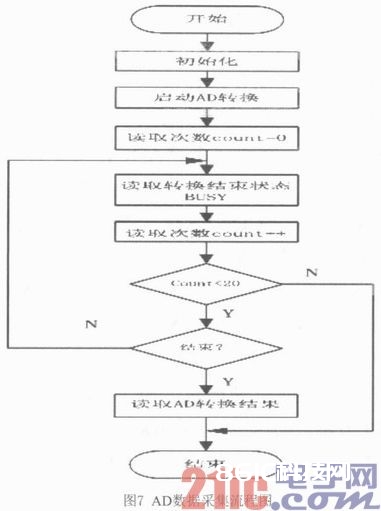

收集软件规划选用了模块化规划,首要包含初始化函数、AD7656转化发动函数和AD7656转化成果读取函数。

初始化函数完结对TMS320C6713B体系时钟、EMIF总线时钟装备,EMIF总线接口拜访时序的装备。经过该初始化函数装备,装备CS(片选)RD读信号相对时序联系,满意AD7656拜访时序联系。

AD7656转化发动函数完结发动AD7656的AD转化,该函数操控AD7656转化发动信号CONVSTA,B,C为有用状况,同步6路AD转化。

AD7656转化完毕标识查询函数完结对AD7656转化状况标识信号BUSY查询,判别AD7656内部ADC转化是否完毕。

AD7656转化成果读取函数完结档查询到AD转化完毕标识后,读取AD转化成果。该函数经过接连的6次读操作,读取6路AD同步转化成果。 AD收集软件流程见图7所示。

5 完毕语

针对要求高精度、多路信号监测和实时收集,本规划选用了AD7656和TMS320C6713B相结合作为某操控体系作业状况实时监控以及毛病检测体系计划,本规划接口电路规划简略,收集精度高、速度快,可一起完结对多路信号的收集。体系联试证明,本体系彻底满意某操控体系对作业状况监控以及毛病检测信号的收集精度和实时性的要求。