导读:在曩昔25年里,微操控器的内部外设产生了巨大的改变。开始许多微操控器只包括RAM、ROM,或许还有根本的定时器。跟着微操控器的开展,更多的外设被根底到这种单价不超越一美元的器材中。定时器/计数器、PWM和包括UART、SPI和I2C在内的规范串行接口常用于这些廉价的微操控器。另一个严重改变是32位CPU正在替代同一价格规模的8位器材。

可是即使有如此丰厚的特性,关于廉价微操控器而言,随时都存在微操控器厂商不能敏捷支撑的项目专用硬件接口或新的第三方接口。往往这要求规划人员运用外部硬件或是经过位拆裂在固件中完结接口。位拆裂运用固件触发IO端口,一般可用于完结串行接口。假如要监测端口以解码串行数据的时分,也能够运用这种办法。无论是运用外部硬件仍是位拆裂来完结接口,都会产生额定的规划本钱。尽管增加外部硬件带来的本钱是显着的,但运用软件完结串行接口或许也会要求运用速度更快因此也愈加贵重的CPU。

大多数通用微操控器今日都支撑 SPI、UART和I2C接口,但依然有许多时分,某些内部用户可编程逻辑会十分有用。Atmel、赛普拉斯、Microchip和NXP等多家公司现已把部分用户可定义逻辑增加到自己的部件上,用于修正部分此类问题。这些器材首要是带附加逻辑的微操控器。CPU依然是首要的处理器材,附加逻辑的作用是进步CPU的作业功率。这类器材常见于本钱敏感性产品中,但也在初级使命中用作小型协处理器,以减轻主处理器的担负,然后进步功率。

另一方面FPGA也正在朝着相似的方针行进,尽管是从另一个方向。赛灵思和Altera多年来一直在增加软硬核处理器以创立片上体系。FPGA办法一般本钱较高,但假如项目需求很多定制逻辑,这便是一种高本钱效益的办法。这些器材关于构建ASIC、小批量产品的原型而言极具价值。这类运用的上市时刻至关重要,而较大型产品需求继续的硬件灵活性。

微操控器调配逻辑与FPGA调配CPU,这两种器材类型都能为现场供给硬件灵活性。一旦根据闪存的器材成为惯例,现场晋级就会成为规范。最早规划人员只能够晋级固件,但现在硬件(逻辑)和固件都能够在现场轻松完结晋级。从核算机鼠标到高速网络路由器等设备均能够从头编写设备的固件和硬件,然后进行现场晋级。

上文提及的四家公司(Atmel、赛普拉斯、Microchip和NXP)均可供给“胶连”逻辑,协助减轻主处理器的负荷,或是无需运用外部逻辑。就供给的逻辑模块类型和这些逻辑模块互相互联的办法以及与定时器、UART和IO引脚等板载模块互联的办法而言,每家公司都采取了不同的办法。

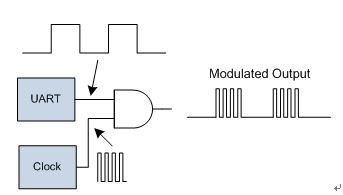

因此有必要了解这些厂家各自是怎么完结内部可编程逻辑的,以便为挑选最合适自己项意图解决方案做出最佳决议计划。只需一个简略的内部AND或许OR门控就足以防止运用外部组件,或是改进CPU功用。一切四种办法都支撑用定制逻辑门控输入和输出信号。这类办法可凭借时钟门控输入,以便运用计数器丈量外部时钟频率。这四类逻辑模块均支撑的一个简略比如是一种调制UART输出,使之用于IR通讯的办法。在此例中,不只要图1所示的内部AND门控,还能够将来自时钟或计数器的信号及UARTTX输出路由到AND门控。

图1 简略调制的UART

AtmelXMEGA定制逻辑(XCL)

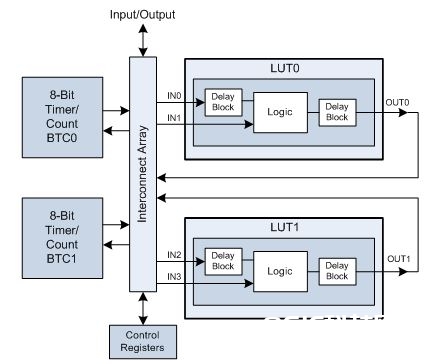

AtmelXCL模块内置两个LUT(查找表)模块,配套两个8位定时器/计数器模块。这两个LUT不用衔接到定时器/计数器模块,而是与UART、 EVENT模块或IO引脚互联。这两个LUT可用作两个独立的2输入单元或一个独自的3输入单元。该逻辑模块可装备为组合逻辑,如AND、NAND、 OR、NOR、XOR、XNOR、NOT或MUX功用。它们也可装备为次序逻辑功用,例如D触发器、D锁存器或RS锁存器。因为能够与其它逻辑模块和IO 引脚互联,这些简略的LUT模块能够方便地让规划人员防止运用某些外部逻辑,或许节约CPU周期。例如AtmelXCL模块运用手册(AT01084)解说了怎么装备XCL模块,以防止在产生额定CPU开支或运用外部逻辑的情况下,为UART输出供给曼彻斯特编码。AVRXMEGAE器材内置一个XCL模块。

图2 Atmel的XMEGA定制逻辑(XCL)

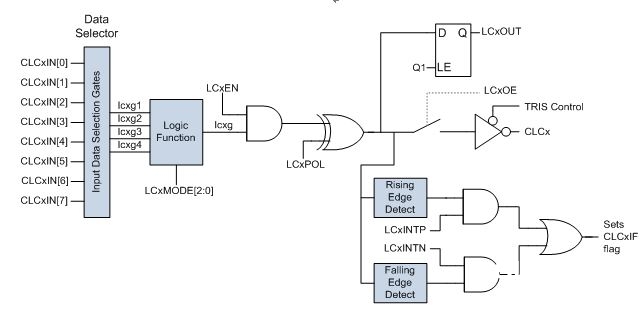

Microchip可装备逻辑单元(CLC)

MicrochipCLC答运用户从八路输入中挑选最多四个信号。这些输入可所以两个IO引脚、内部时钟、外设或寄存器位的组合。这四个信号随后路由到可编程逻辑模块中。该逻辑模块可编程为AND-OR、OR-XOR、4输入AND、S-R锁存器的8种组合之一,也可装备为4种其它触发器组合之一。 Microchip在其《可装备逻辑单元提示与技巧》运用手册中给出了部分实例。其间的实例之一演示了怎么装备这些模块以解码正交信号。在不运用这些额定的逻辑模块情况下,CPU需求以高得多的速率采样信号,才干防止正处于转化阶段的信号产生伪旋转,让CPU只被有用转化中止。 MicrochipP%&&&&&%10(L)F320/322器材每个都包括一个CLC模块,而每个CLC模块都包括四个图3所示的模块。

图3 Microchip的可装备逻辑单元(4个中的一个)

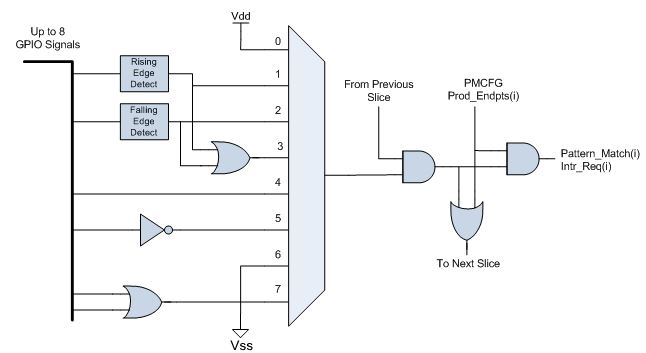

NXP形式匹配引擎

NXP供给的用户可装备逻辑被称为形式匹配引擎。该逻辑模块的输入可挑选最大八个GPIO输入。这八个输入可为杂乱的布尔表达生成乘积项。这些输出可用于触发中止,驱动特别IO引脚,或是路由到下一个逻辑模块或slice。其它特性则支撑上升或下降信号以及反相信号的边际检测。该附加硬件经装备后,只要产生杂乱(或简略)事情组合时才中止CPU。NXPLPC81x器材内置一个形式匹配引擎。

图4 NXP引脚中止/形式匹配引擎

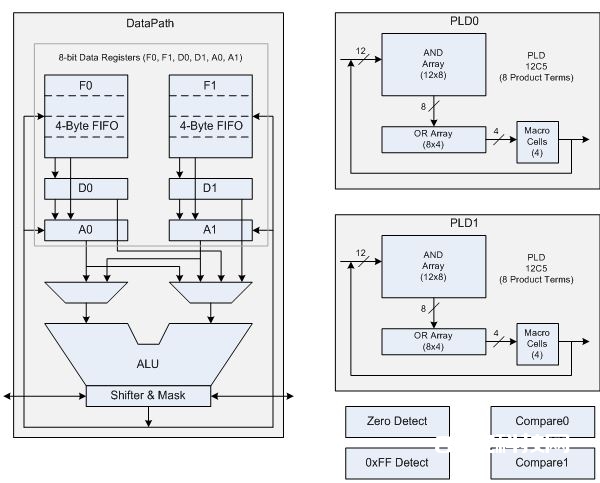

赛普拉斯PSoC通用数字模块(UDB)

赛普拉斯经过运用通用数字模块或UDB,选用更先进的办法在上文介绍的其他三个厂商的办法和FPGA之间别出心裁。一个UDB由两个12C4PLD和一个数据通路构成。PLD可用于操控数据通路的操作和数据流,也可用作通用逻辑和状况机。数据通路是一种能供给8位功用(AND、OR、ADD、SUB、INC、DEC、XOR)、移位功用(左和右)以及供数据排队的两个4字节FIFO的定制模块。这些模块也能够结合在一起供给16位、24位或32位功用。

UDB的输入和输出可路由到任何 GPIO、外设/组件IO、中止等。UDB、固定功用模仿和数字模块以及GPIO之间的互联都运用数字信号接口(DSI)处理。UDB经编程可完结为任何功用,包括从简略的逻辑门到计数器和PWM以及UART和I2C外设等通用串行接口。

就运用UDB完结规划而言,用户能够挑选多种选项。既可把简略的逻辑门布局在原理图中,也可在Verilog中完结规划。还可供给定制图形界面,无需运用Verilog即可完结规划。PSoC3、 PSoC4和PSoC5系列微操控器可包括4个到24个此类逻辑模块(UDB)。

图5 赛普拉斯PSoC通用数字模块(UDB)

定制接口实例

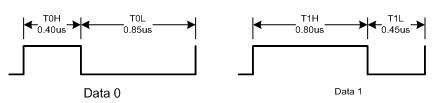

最近我注意到Worldsemi出产的一些RGBLED很有意思。部件编号分别为WS2811、WS2812和WS2812B,但它们作业办法共同。只需求一个GPIO引脚,您就能够驱动1,000个或许更多的此类部件。这适当令人感兴趣,因为我能够用一个GPIO引脚操控如此大数量的RGBLED。衔接这些LED的接口不是SPI、UART或I2C,而是定制接口。通讯信号选用异步信号,每一位开始于上升沿。数据为1或0由下图所示的高脉冲长度决议。

图6 WS2811/12数据0/1时序

每个部件需求24位数据,每一种色彩(红、绿、蓝)为下列格局的8位。

图7 WS2811/12数据格局

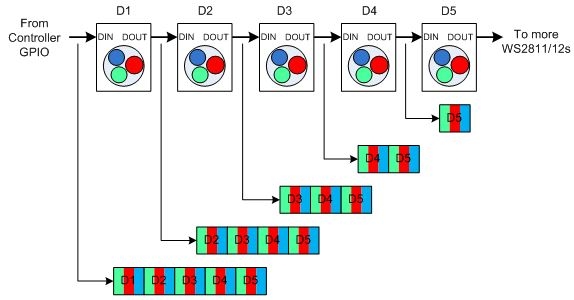

WS2811/12部件选用DIN(数据输入)和DOUT(数据输出)信号,以便简略地进行串行衔接。每个部件都保存其看到的头24位数据,然后把剩下数据从DOUT引脚输出。拜见下面的图8。

图8 衔接多个WS2811/12部件

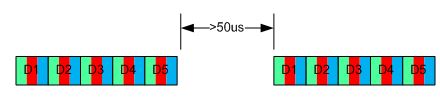

当数据流发动后,每个部件将看到继续的数据流。假如数据信号的上升沿不超越50微秒,部件会锁存数据,将紧邻的24位数据视为自己的数据,并将其他数据从头发送出去。

图9 数据流搁置时刻超越50微秒时器材复位

正如您所看到的,其原理并不杂乱,但它并不能轻松地适配到规范的微操控器硬件上。我的确发现有人运用SPI接口来保持时序,但这要求每个实在的数据位运用至少三个SPI数据位,关于经过位拆裂取得CPU功用而言优势不大。因为时序并不严厉,假如您在固件中完结接口(位拆裂),CPU将专门用于翻转驱动信号直至LED悉数更新。这意味着您需求禁用一切中止,在整个过程中不对任何其它输入做出呼应。假如您有1,000个LED,则更新时刻为(0.40微秒+0.85)*24位*1,000个LED=30,000微秒或30毫秒。这或许并不是什么问题,但假如您要以30Hz的频率更新LED,将简直占用 100%的CPU!

在编写代码时,我习惯于在不得不较长时刻禁用中止的当地防止堵塞代码或条件,特别在体系中有用户接口或是需求与其它处理器通讯的情况下尤为如此。我的意图是尽量减轻CPU的担负,让硬件完结大部分作业,就好像今日常见的内部UART或SPI模块所做的作业相同。赛普拉斯PSoCUDB有几项特功用让这项作业变得十分简洁。每个UDB在数据通路中有两个4字节FIFO和一个移位器。在完结UART时,您可将一个FIFO 用作TX缓存,另一个用作RX缓存。关于WS2811/12,我只需求一个输出FIFO和移位器。我决议装备硬件,为每个器材每次生成一次中止。中止处理器将加载24位(3字节)数据,直到FIFO为空时回来。选用这种办法,能够每30微秒中止一次,而不用以150毫微秒或更短距离禁用悉数中止和位拆裂。我决议运用的微操控器是赛普拉斯PSoCCY8C4245AXI。该微操控器大批量收购价格约为一美元,有四个UDB,运转频率为48MHz,足以满意此项作业所需的速度和硬件要求。

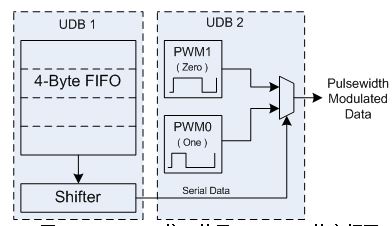

规划运用了PSoC供给的四个UDB中的两个。一个用于运用FIFO缓冲数据和移位数据,这样每个器材的悉数24位(3字节)可一次性写入。第二个UDB可运用两个比较输出创立PWM。一个比较输出用于创立逻辑0,另一个用于创立逻辑1。该串行数据可用于操控数字多路复用器,挑选波形1或0。敬请拜见下图10的方框图。

图10 WS2811/12接口运用PSoCUDB的方框图

UDB中四个PLD(每个UDB有2个)的大多数乘积项可用于操控数据通路,生成中止,供给状况和操控功用,但这也运用了这种低本钱微操控器中一半的UDB资源。

接下来的作业是清晰这一附加硬件能为规划节约多少CPU开支。以1,000个LED组成的阵列为例,其改写频率为30Hz。假如规划运用固件对接口进行位拆裂操作,会差不多占用100%的CPU资源。运用PSoC器材中的可编程硬件依然能够做到每30微秒中止一次,尽管这也是较重的负荷,但运转在 48MHz的ARMCortex-M0足以敷衍。为测验CPU开支,我创立了一个简略的环路,以大约30Hz的频率改写显现器。在主环路中,我触发了一个引脚,然后运用示波器核算40毫秒内的触发数量。然后我禁用中止,再次运转项目,并比较成果。与运用固件中的位拆裂形成的简直100%的CPU占用比较,继续显现改写只占用大约12%的CPU资源。这样别的88%的CPU周期可用于外部通讯和用户界面。假如为规划增加DMA,该开支或许会从12%下降到 2%或更低。我运用的最廉价PSoC(约1美元)只包括UDB但未包括DMA,不过一些较大型的部件的确内置有DMA。

随后我实践制造了一个由60×16个LED(960个LED)网格组成的真实RGBLED板,用于测验该组件。该组件的运转契合预期,可用作显现根本的直线、矩形、圆圈以及文本的图形界面。

图11 运用960个RGBLED制造的广告牌

无论是大型LED板仍是简略的定制界面,部分内部可编程硬件会给规划功用形成严重影响。不是每一种定制界面都需求多字节FIFO或全硬件状况机,但具有这种灵活功用为您供给更多规划挑选、进步功用,或是让现有规划敏捷合适产品需求。