摘要:为了满意某型车栽产品关于操控终端叠加字符信息的需求,依据视频字符叠加基本原理,剖析了几种字符叠加计划,提出一种依据字符叠加芯片MB90092的字符叠加体系规划,并给出该体系的硬件电路规划及其软件编程。实验室运转结果表明,该体系运转安稳,能够将指定字符信息叠加于指定方位,且叠加内容依据需求可快速替换,能够用于工程运用。

视频字符叠加,是指在显现屏幕的指定区域以必定的透明度显现指定的图画符号或字符。字符叠加在多媒体、监控体系、电视等范畴有着广泛需求,以视频监控为例,在监控端需求接纳外部数据并实时的显现在监控屏幕上,如时刻、机号、地址等信息。一同许多工业运用的人机界面和视频播映场合也需求能够叠加各种图文信息,视频字符叠加的运用能够明显进步操控终端的操控功用和人机成效。

本文结合某型车载产品的要求:电视与热像可自在切换、叠加器与上位机通过CAN总线进行通讯的需求进行规划,给出依据视频叠加芯片MB90092和单片机AT89S53的OSD体系规划,包括硬件电路和软件规划两部分,并通过实验验证了计划的可行性。

1 叠加原理

将一系列静态图画以电信号方法加以捕捉、记载、处理、存储,运用人眼的视觉暂留特性,以高于人跟闪耀频率的速度进行图画传输就构成了接连的感觉,在接纳端进行重现就构成了视频。

每一幅图画都是由若干像素组成的,视频传输时依照次序制将一个个像素的光学信息转化成电信号,用一条通道顺次传输出去,在接纳端再依照相同的次序将各电信号在相应的方位上转化成光学信息。字符由24×32 dots(象素)构成,每个象素对应屏幕上一个点,叠加字符的实质便是把相应的字符象素叠加到用户指定的方位。屏幕光栅由电子束在水平方向和笔直方向扫描构成,用内部时钟作为点时钟对屏幕上的象素点进行计数,行同步信号为换行信号操控像素的叠加。

2 计划挑选

常用的视频字符叠加有以下4个计划:1)通用中小规划集成电路:选用通用中小规划集成电路完结单路视频字符及时刻叠加,这种计划需过于杂乱,可靠性差;2)依据FPGA的计划:共用一片CPU、字库ROM和实时时钟,运用FPGA集成若干独立的显现RAM计数扫描电路,完结多路字符叠加。但在多路显现中,有必要运用多片RAM和大规划多路开关处理RAM的时分复用问题,大大增加了电路的杂乱性,一同进步了本钱;3)依据单片机的计划:运用软件完结在消隐期内对显现RAM的计数扫描和点阵数据的移位输出,只适用于字符数量少的运用,简单形成视频信号的不接连;4)依据专用字符叠加器的计划:专用字符叠加芯片一般答使用户叠加文字和图画,一同设置行距、字符巨细等特色,一般将字符信息做成字符库存放于外部ROM中以便利调用。计划功用强,适用于显现字符较多的场合,且价格适中。鉴于以上各计划特色,规划选用第四种计划,视频处理流程如图1所示。

3 体系规划

3.1 电源电路规划

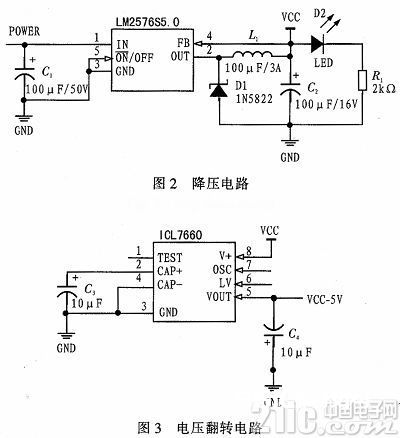

体系预留24 V供电口,规划中除视频切换开关AD8184选用±5 V供电外,其它芯片选用5 V供电。因为24 V与5 V的压差太大,考虑到转化功率以及散热问题,规划选用开关型稳压器LM2576取得5 V电压,运用电源翻转芯片%&&&&&%L7660取得负极性电压。LM2576电路中电容C2的耐压值应大于额外输出电压的1.5~2倍,5 V输出挑选耐压16 V的电容。电压翻转电路中C3、C4选用漏电小、介质损耗低的钽电容进步电源转化功率,如图2、3所示。

3.2 视频箝位电路

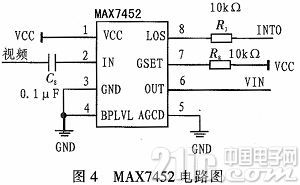

视频信号中包括沟通和直流重量,信号经沟通放大器处理时,因为放大器存在耦合电容,在处理过程中信号会丢掉直流重量,而直流重量是图画的黑电平(即同步电平),同步电平无法固定在同一电平大将严重影响视频信号的行、场同步。选用MAX7452作为完好的前端视频信号调节器,对输入视频信号进行预处理。

如图4所示。将VBPLVL端直接箝位到地,能够省去输出耦合电容,下降行时刻失真的可能性,一同减小板上空间的需求。设置芯片引脚AGCD=0、GSET=1,可向规范视频负载(150Ω)输出2 Vp—p的满幅视频信号,并满意MB90092需求1 V偏置电压的要求。MAX7452的输入至少在15行内没有同步时,其LOS检测器输出一个逻辑高电平,与单片机的外部中止0衔接,能够有用指示摄像机或线缆的毛病状况。

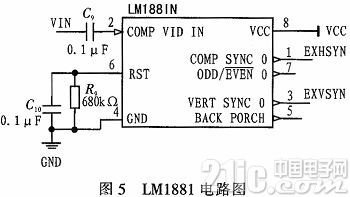

3.3 视频同步别离电路

全电视信号包括有视频信号、复合同步信号、复合消隐信号、槽脉冲信号以及前后均衡脉冲信号,若要对视频信号进行处理,就有必要精确的提取出各信号并掌握信号间的逻辑联系。LM1881是针对电视信号的视频同步别离芯片,用于从峰峰值0.5~2 V的规范负极性PAL制视频信号中提取守时信息。如图5所示,芯片的2脚接一个复合输入耦合电容,6脚接一个电流耦合%&&&&&%以及一个680 kΩ的电阻用于设置内部电流值,该电阻使LM1881能用于水平扫描频率不同于15.734 kHz的信号源。

3.4 字符叠加电路规划

MB9009是一款专用视频字符叠加芯片,用以显现操控视频中的文字和图画。芯片外部只需衔接少数的电子元件就能够显现汉字和图形,可便利的嵌入各种数字视频监控体系中,因而在各个职业和各种范畴得到广泛运用。

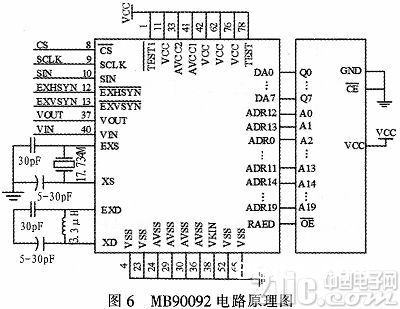

MB90092首要通过CS、SCLK、SIN3个引脚与MCU相连来接纳外部操控指令和数据。MB90092共有13种指令和两种保存指令,单片机通过这些指令完结对字符显现的操控,每个指令由两个字节组成,第一个字节的前5位为指令码,其他位和第二个字节为数据。

芯片可通过地址和READ信号读取外部字体存储器中的字体数据,最大可操控外部16Mbits的字库内存。时钟模块的输入时钟作为字符叠加的点时钟,LM1881输入的行、同步信号作为X、Y轴的复位时钟来操控时序。汉字字库存储在外挂Flash存储器。依据电路与外部字符存储器的地址接口联系及电路读取点阵数据的次序,将所需求叠加字符的点阵生成可烧结的HEX文件,烧录到外部存储器中。外挂的字库模块运用户能够依据需求随时更改字符点阵。

通过单片机向MB90092发送显现以及写数据操控指令,视频信号经调节后与复合同步信号以及场同步信号一同被送入MB90092,MB90092依据微操控器的指令从字库中调取字符,将原始视频信号及叠加字符按必定份额混合,送出叠加后视频,如图6所示。

3.5 单片机体系

单片机担任两方面的作业:1)通讯:单片机运用SJA1000和TJA1050从CAN总线接纳信息及数据;2)视频叠加:单片机依据操控终端的恳求,改换进入视频叠加板的视频信号,单片机的P1.2、P1.3端口衔接到视频切换开关AD8184的A0、A1,编程操控决定要进入叠加板的视频信号,并依据从CAN总线取得的数据和指令进行叠加。

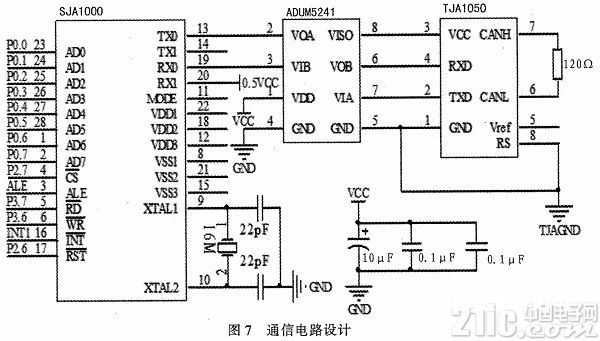

3.6 通讯电路规划

视频叠加电路通过CAN总线与上位机进行通讯,因为AT89S53单片机没有自带CAN总线接口,挑选PHILIPS公司的SJA1000作为CAN总线操控器,TJA1050作为总线驱动器。二者之间通过电磁阻隔器ADum5241相连,能够完结总线上各CAN节点之间的电气阻隔。

SJA1000作为独立CAN总线操控器,完结上位机与现场微处理器之间的数据通讯。通过CAN总线接纳来自上位机的数据进行剖析组态然后传给下位机的操控电路完结操控功用,当CAN总线接口接纳到上位机的下传数据,SJA1000就发生一个中止,引发微处理器发生中止,通过中止处理程序接纳每一帧信息。AT89S53是CAN总线接口电路的中心,其承当CAN操控器的初始化、CAN的收发操控等使命。TJA1050是CAN协议操控器和物理总线的接口,引脚RS接地默许进入高速形式。挑选电磁耦合进行电气阻隔,相较于光耦阻隔,磁阻隔下降了功耗,比光耦具有更高的数据传输速率、时序精度和瞬态共模按捺才能,一同也消除了光耦不安稳的电流传输率、温度和运用寿命等方面的问题。

规划通讯电路时应留意:1)SJA1000的中止输出漏极开路,驱动单片机中止引脚时应加上拉电阻;2)因为运用外接驱动器,RX1应接到CAN电平(比较器电平)的中点以旁路CAN比较器,削减延时;3)阻抗不接连和阻抗不匹配将导致信号反射,为了消除通讯电缆中的信号反射,CAN总线通讯时必定要加上120Ω的终端电阻,终端电阻对匹配总线阻抗起着非常重要的作用。疏忽此电阻会使数字通讯的抗干扰性和可靠性大大下降,乃至无法通讯。

4 软件规划

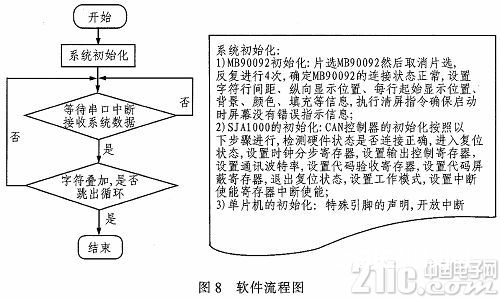

视频叠加板的软件分为CAN通讯和叠加显现两个部分。软件运转时首要完结单片机、SJA1000、MB90092芯片的初始化,开CAN中止等候接纳数据,接纳到数据后置位标志位并进入中止服务程序,依据指令完结MB90092的指令与数据传输,完结字符叠加后铲除标志位,持续等候CAN中止。

字符叠加程序首要包括模仿SPI总线通讯、MB90092的数据传输、芯片关于显现字符的特色设置、初始化程序以及片外存储器寻址的一些函数。软件流程如图8所示。

5 定论

通过实验验证,该字符叠加器现已能够正常运用,在不影响原视频显现作用的基础上,字符及图形能够以指定的方位、巨细精确的叠加在视频上。本文规划的字符叠加器现已运用在某型车载产品中,能够精确接纳外部指令及数据,恣意切换电视以及热像视频,具有广泛的运用价值和很高的性价比。