摘要:针对数字基带信号的特色和通讯体系对信号传输的要求,使用DDS数字频率组成技能进行波形规划。选用了ADI公司的AD9958芯片为中心规划完结了全数字频率组成器,构建了具有FSK调制,PSK调制及线性扫描功用的全数字通讯体系。具体介绍了该通讯体系的首要构成和完结全数字波形规划的软件操控办法,使其具有多种信号方法,较宽的作业频带、依据作业需求随时改换波形的功用。该体系具有可重复编程和动态重构的长处,使其易于修正,灵敏可控,可适用于通讯工程实践中。

要害词:DDS;波形规划;FSK;PSK;线性扫描调制;AD9958

0 导言

现在在各类通讯体系中的波形规划,一般是指调制波形的规划问题。一个完善的通讯体系一般有多种信号方法、较宽的输出作业频带、依据作业需求随时改换波形,以到达最好的作业作用。

直接数字式频率组成器(Direct Digital Synthesizer,DDS)是近年来跟着数字集成电路和微电子技能的快速开展而敏捷鼓起的一种新的频率组成技能。它将先进的数字信号处理理论和办法引进到频率组成范畴中,有用处理许多模仿组成技能无法处理的问题。模仿的办法最大的问题是不能完结波形捷变,而数字的办法处理了这个问题,并且还能够进行幅相补偿,杰出的灵敏性使得数字波形的发生办法越来越遭到重视。

1 DDS作业原理

DDS频率组成技能具有ns量级的捷变频时刻,mHz量级频率分辨率,相对带宽较宽,高优秀的相位噪声功用,能够便利的完结各种调制,是一种全数字化、高集成度、可编程的体系。其作业原理如图1所示。

DDS使用于各类通讯体系时,参阅频率源fr多选用安稳的晶体振荡器,以得到频谱纯洁的作业时钟。累加器由多个级联的加法器和寄存器组成,当参阅频率源fr输入一个时钟脉冲时,它的输出添加一个步长的增量值,增量的巨细随频率操控字Kf的不同而改动。当用这个增量的数据进行寻址查表时,正弦查表就把存储在累加器中的抽样数字值转换成近似正弦波起伏的数字量函数,D/A转换器就把数字量转化成模仿量,低通滤波器进一步滑润近似正弦波的锯齿阶梯函数。

DDS技能与大多数的数字信号处理技能相同,根底仍然是奈奎斯特采样定理。该定理指出当抽样频率大于或许等于模仿信号最高频率的两倍时,能够由抽样得到的离散序列无失真地恢复出原始模仿信号。DDS技能不是对模仿信号进行抽样,而是一个假定抽样进程现已发生且抽样值现已量化完结,怎么把现已量化的数值重建原始信号的问题,理论上最大输出频率不会超越体系时钟频率fr的1/2,但在实践使用中因为DDS体系中的低通滤波器非抱负特性,由通带到阻带之间存在着一个过渡带,工程中DDS最高输出频率只取fr的40%左右。

因为遭到操控字长N的约束,累加器累加到必定值后,就会发生一次累加溢出,溢出频率即为组成信号的频率。可见,频率操控字Kf越大,累加器发生溢出的速度越快,输出频率也就越高。故在参阅频率fr不变的条件下,改动频率字就能够改动输出信号的频率。输出信号的频率分辨率及输出信号频率核算如下:

![]()

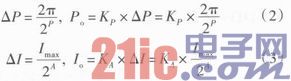

同理,依据以上查表和累加溢出的原理,对相位和起伏(电流)也有相同的核算,可得出相位分辨率及输出信号相位操控字核算如式(2)所示,输出信号起伏(电流)分辨率及输出信号起伏(电流)操控字核算如式(3)所示。

式中:KP为相位操控字;P为相位累加器位数长度;KA为起伏(电流)操控字;A为起伏累加器位数长度,Imax为输出最大电流。

2 依据AD9958的波形规划

2.1 体系原理框图

DDS这种相似与查表直接输出信号的组成办法,使其更适用于波形捷变的调制要求。在进行波形规划时,应依据需求选用功用齐备的芯片,不只要求具有操控起伏、相位、频率的才能,还要从整个体系的视点动身进行挑选。

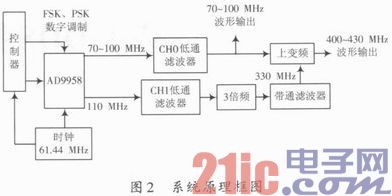

为完结某一带宽信号的PSK调制、FSK调制或线性扫频,以ADI公司的DDS芯片AD9958使用为例,规划一款双通道波形生成器,体系的原理框图如图2所示。

AD9958是ADI公司的一款高度集成的双通道直接数字频率组成器,其功用特色如下:

(1)具有2路可同步、可独立操控的信号通道,2路10位的DAC,通道隔离度大于72 dB;

(2)集成了32位频率累加器,14位相位累加器,10位的起伏操控字。可编程的通道操控对因为模仿处理(例如滤波、扩大)或许PCB布线的失配而发生的不均衡进行校对;

(3)具有三种可编程的作业形式:单频形式、调制形式和扫描形式;

(4)具有线性频率、相位、起伏的扫描功用;

(5)支撑最高16进制的ASK,FSK和PSK直接调制功用和相应操控电路;

(6)串行操控接口速度高达800 Mb/s;

(7)具有正余弦波形表,可编程4~20倍的REFCLK倍增器电路,最高500 MHz的体系时钟。

2.2 DDS硬件电路规划

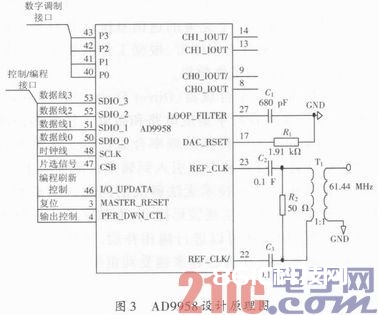

体系选用61.44 MHz的晶振,作为操控器和DDS的输入时钟。在DDS内部启用REFCLKP倍增器电路,选用7倍的倍增系数,因而DDS体系时钟f=430.08 MHz。

在规划中该芯片的编程接口选用多线制串行操控,别离为时钟线SCLK和数据线SDIO_0~SDIO_3,其间SCLK最高速度可达200 Mb/s,当SDIO_0~SDIO_3悉数用作数据线时,操控数据速率最高可到达800 Mb/s。以2线制操控接口为例,设置操控参数CSR2:1>=00,则SCLK作为时钟信号,SDIO_0作为数据信号。

2.3 各类波形规划

2.3.1 单频点形式

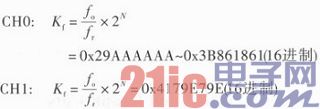

AD9958具有两路输出,别离为CH0:70~100 MHz,CH1:110 MHz,频率操控字长度N=32,相位操控字长度P=14,起伏操控字长度A=10。别离核算出各自通道的频率操控字,写入32位频率操控字CTW0。由式(1)得到频率操控字核算如下:

同理可依据信号相位和起伏的输出要求,依据式(2)和式(3)核算得出相位操控字Po和起伏操控字Io,别离写入相位操控字CPW0的低14位和起伏操控字ACR的低10位,即可完结2路独立单频信号的输出。

2.3.2 调制形式

AD9958支撑2/4/8/16进制的ASK,FSK和PSK直接调制功用和相应操控电路,设置调制形式寄存器CFR23:22:14>和调制阶数寄存器FR19:8>。调制参数写入32位操控寄存器CTW0~CTW15,接口P0~P3在调制形式下输入数字调制的数据。

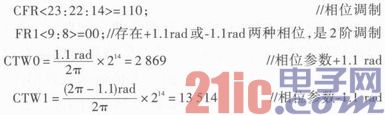

以BPSK调制形式为例,调制相位+1.1 rad或-1.1rad,调制速率800 b/s,设置参数:

当CH0通道发生调制信号时,P2操控口作为调制数据输入操控,二进制数据“1”对应+1.1 rad相位,数据“0”对应-1.1 rad相位,当P2口的二进制数据进行改动时,输出的模仿信号相应的发生相位改动。严格操控P2口的二进制数的速率,让每一位二进制数据的坚持时刻为1/(800 Hz)。

以4FSK调制形式为例,调频频率为4个,别离为F0~F3,调制速率800 b/s,设置参数:

CFR23:22:14>=100: //频率调制

FR19:8>=01; 在4种调制频率,是4阶调制

CTW0=F0; //调频参数1

CTW1=F1; //调频参数2

CTW2=F2; //调频参数3

CTW3=F3; //调频参数4

当CH0通道发生调制波形时,P0和P1操控口作为4进制调制数据操控口,P1:P0>=00时,输出信号频率为F0;P1:P0>=01时,输出信号频率为F2,P1:P0>=10时,输出信号频率为F3,P1:P0>=11时,输出信号频率为F4,依据P0和P1的数据改动完结4进制FSK调制。严格操控P0和P1口的二进制数的速率,让每一位二进制数据的坚持时刻为1/(800 Hz)。

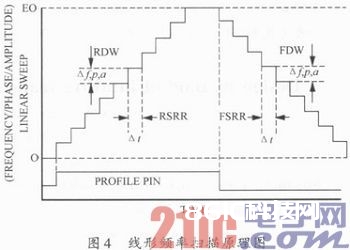

2.3.3 线性扫描形式

AD9958对起伏、频率和相位都具有线性扫描功用,当线性扫频形式时,其原理图如图4所示。

设置线性扫频形式CFR23:22:14>=101,其扫频上升和下降捷变时刻参数别离为RSRR和FSRR,都是8位寄存器,因而最小捷变频时刻△t=16.276 ns,最大捷变频时刻△t=4.167 μs,可依据需求将操控字写入RSRR和FSRR。

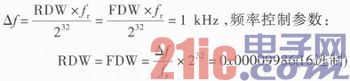

扫频频率步进△f=1 kHz,其扫频上升阶段和下降阶段频率操控参数别离为RDW和FDW,图4中

用操控接口P2作为CH0通道的线性扫频操控接口,当P2=1时完结上升线性扫频阶段,P2=0时完结下降线性扫频阶段。

3 结语

DDS全数字结构操控功用使它具有多种数字调制才能,如相位调制、频率调制、起伏调制以及I/Q正交调制等,组成信号时具有超宽的相对带宽、超高的捷变速度、超细的分辨率、接连的相位特性、能够输出宽带的正交信号等许多优胜功用,因而该技能在现代数字通讯范畴中有宽广的使用远景,是很多使用电子体系完结高功用的要害。该体系具有可重复编程和动态重构的长处,使其易于修正,灵敏可控,可广泛适用通讯工程实践中。