摘要:本规划选用Hittite公司出产的频率合成器芯片HMC703LP4E为中心,经过上位机经FPGA输入操控信息来发生雷达体系运用的步进频率信号。该频率源具有输出信号频带宽、变频时刻短、信号安稳的特色,在雷达体系规划中现已有所运用。本文给出了规划办法和试验成果。

0 前语

在雷达体系中,频率源扮演着重要的人物,其功用直接影响着整个雷达体系。跟着无线电技能的开展,频率源的规划方案也千变万化,人们规划了各式各样的频率源,其间选用锁相环 规划的频率源具有输出频率高、频率安稳度高、频率纯、低相噪、杂散按捺好等长处。本文以HMC703LP4E频率合成器芯片为中心,外加压控振荡器,规划了一种用FP GA来操控的锁相环

规划的频率源具有输出频率高、频率安稳度高、频率纯、低相噪、杂散按捺好等长处。本文以HMC703LP4E频率合成器芯片为中心,外加压控振荡器,规划了一种用FP GA来操控的锁相环 电路,该电路体积较小,调试便利。与其它锁相环

电路,该电路体积较小,调试便利。与其它锁相环 电路比较,选用HMC703LP4E完结的锁相环

电路比较,选用HMC703LP4E完结的锁相环 电路体积小,输出信号质量好,带宽宽、变频时刻快。

电路体积小,输出信号质量好,带宽宽、变频时刻快。

1 HMC703LP4E功用特色介绍

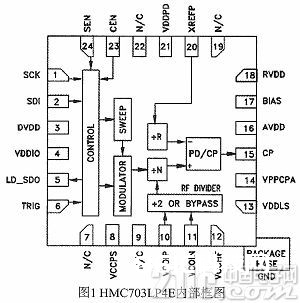

HMC703LP4E内部框图如图1所示,它是一款宽带频率合成器,输入信号的频率规模为DC-8GHz。它自身不带压控振荡器(VCO),需求外加压控振荡器才干输出所需的信号,其相噪和杂散目标好,功用强大,可进行相位调制,除了能用于完结点频和步进频信号外,还能用于完结线性调频信号。

2 步进频率源参数规划

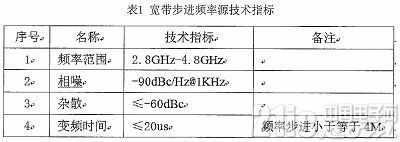

依据HMC703LP4E的宽带步进频率源规划首要包括输出信号频率、参阅频率、鉴相频率、滤波器的环路带宽、相位噪声、变频时刻和杂散按捺等参数的规划。依据所规划的雷达体系频率改换需求,本文规划的步进频率源目标如表1所示。

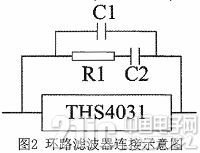

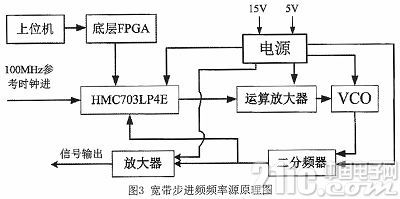

规划时,依据雷达体系所能供给的基准频率挑选参阅频率为1 00MHz,压控振荡器芯片挑选Hittite公司的HMC587LC4B,它是一款宽带压控振荡器芯片,其输出频率规模为5-10GHz,规划中选用二分频器将其频率规模降到2.5GHz-5GHz,满意雷达运用需求,二分频器挑选Hittite公司的HMC361S8G。规划时选用有源滤波的办法进行环路滤波,运算扩大器挑选THS4031。挑选扩大器SBB3089对输出信号进行扩大,该扩大器的增益在其作业带宽内比较平整。依据变频时刻和相位噪声两个目标归纳考虑,本文规划的环路滤波带宽为

200KHz,有源滤波器的电阻和电容衔接如图2所示,依据仿真核算和调试经历,得到有源滤波器上的电阻和%&&&&&%参数为R1=520Ω, C1=2nF,C2=10nF。

3 步进频率源完结

3.1 步进频率源硬件完结

电路规划时,射频电路和电源电路分隔规划,放置在屏蔽盒的正反面,射频电路规划时需考虑到阻抗匹配,选用电源芯片H MC976LP3、HMC860LP3和LT1965别离对锁相环 、VCO和运算扩大器供电。

、VCO和运算扩大器供电。

依据HMC703LP4E的宽带步进频率源规划原理框图如图3所示。

3.2 步进频率源软件完结

体系硬件规划完结后,需求软件对HMC703LP4E进行操控,因而设定操控办法为:上位机下发操控指令给主控FPGA,FPGA依照上位机的指令经过输出不同的操控指令码给芯片完结频率操控。依据体系的作业办法,设定频率输出形式为点频形式和步进频形式。点频形式安稳输出某一固定频率信号,步进频形式则是依据设置好的开始频率、步进频率和停止频率输出各频率信号。

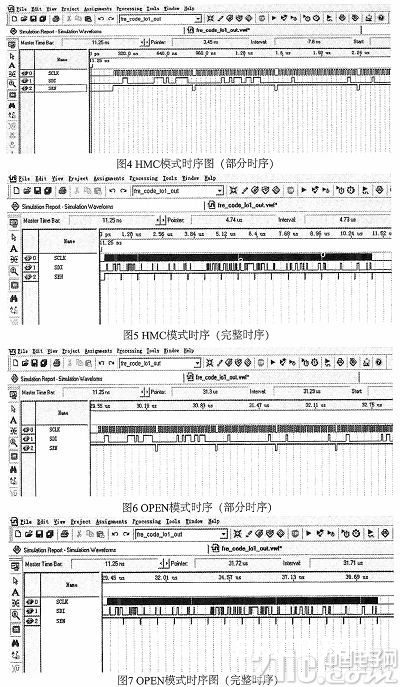

HMC703LP4E有两种装备形式,HMC形式和OPEN形式,在芯片上电时确认其作业形式,之后依照该形式对其进行装备。HMC装备形式的仿真时序如图4和图5所示,OPEN装备形式的仿真时序如图6和图7所示。

HMC703LP4E具有多种作业形式,包括Integer Mode,Fractional Mode,Exact Frequency Mode,FM Mode,PM Mode和Frequency Sweep Mode共7种形式。依据体系需求和操控的杂乱程度,终究挑选Fractional Mode作为步进频形式的作业形式。在这种形式下,上位机别离下发频率码整数部分和分数部分操控码,底层FPGA对其进行解码后,依照相应的时序操控HMC703LP4E输出所需求的频率。

4 功用测验

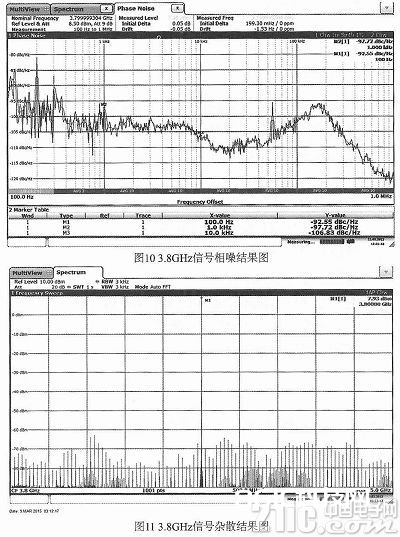

选用罗德与施瓦茨公司的信号与频谱分析仪在试验室对输出信号的功用进行测验,测验衔接图如图8所示。测验相噪和杂散功用时挑选了中心频率3.8GHz,其他频点测验成果与其相差不大。图9为频率源变频时刻测验成果,因为仪器自身的约束,每次测验最多只能选取160MHz带宽的信号。在测验时设置频率步进为1MHz,重复频率为25KHz,即每隔40us进行一次数据更新,图9中Dwell Time加上Switching Time为重复频率,Switching Time为变频时刻,此刻刻表明HMC703LP4E芯片中所有寄存器更新结束后信号安稳需求的时刻,FPGA操控宽带步进频率源时选用10MHz时钟,总共需求更新64位数据,即写寄存器的时刻为6.4us,从图9中能够看出完结一次变频所需求的总时刻小于10us。图10为3.8GHz相噪测验成果,从图10中能够看出3.8GHz信号在1KHz处的相噪为-97.72dBc/Hz@1KHz。图11为3.8GHz信号的杂散,从图11中能够看出其杂散小于-60dBc。以上测验成果都能契合目标要求。

5 定论

本文介绍了利用以HMC703LP4E频率合成器芯片为中心,外加环路滤波器和压控振荡器的电路规划,选用FPGA进行操控完结2.8GHz-4.8GHz宽带步进频率源的规划进程和规划办法,给出了电路规划中的要害器材以及环路滤波器规划的要害参数,经过对硬件电路的调试和功用优化,完结了雷达体系所需的体积小,功用好的宽带步进频率源。