摘要:提出了一种根据嵌入式技能的嵌入式数字示波器规划办法,硬件规划以STM32为主控中心,选用高功能低噪声的AD8066电压反应性扩大器、压控增益扩大器AD603和双路D/A转化器TLV5618A组成程控扩大电路,并选用高速带宽A/D转化器和IDT7204高速缓存器组成数字收集电路,以TFT彩屏输出信号波形。软件规划移植开源的实时操作体系μC/OS-II体系,确保了体系的实时性和安稳性。试验结果表明规划思路正确,功能参数到达规划要求。

0 导言

嵌入式数字示波器是近年来发展起来的一种集显现、丈量、运算、剖析、记载等多种功用于一体的智能化丈量终端设备。凭仗其强壮的功能优势,己逐渐替代传统模仿示波器。当时国内通用的数字示波器大都选用51单片机、FPGA、DSP等结构。可是51单片机处理才能有限,无法完成数字示波器的根本目标,FPGA尽管能深化开发数字示波器,但是,其本钱偏高,即便参加SOPC软核,其软件压力也很大。

本规划选用ARM处理器中根据Cortex-M3内核的32位STM32F103VCT6作为主控芯片。该芯片内部集成了16通道的12位高精度A/D转化器,转化时刻仅为1μs,并且STM32芯片具省电形式,功耗低,与传统MCU比较,其在功能和处理才能上都比较契合本规划要求。

1 体系规划方案

1.1 体系作业原理

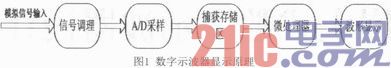

数字示波器的作业原理能够用图1来描绘,当输入被测信号从无源探头进入到数字示波器,首要通过的是示波器的信号调度模块,由于后续的A/D转化器对其丈量电压有一个规则的量程规模,所以,示波器的信号调度模块便是担任对输入信号的预先处理,通过扩大器扩大或许通过衰减网络衰减到必定适宜的起伏,然后才进入A/D转化器。在这一阶段,微操控器可设置扩大和衰减的倍数来让用户挑选调整信号的起伏和方位规模。

在A/D采样模块阶段,信号实时在离散点采样,采样方位的信号电压转化为数字值,而这些数字值成为采样点。该处理进程称为信号数字化。A/D采为采样速率,表明为样值每秒(S/s)。A/D转化器最终将输入信号转化为二进制数据,传送给捕获存储区。被测的模仿信号在显现之前要通过微处理器的处理,微处理器处理信号,包含获取信号的电压峰峰值、有效值、周期、频率、上升时刻、相位、推迟、占空比、均方值等信息,然后调整显现运转。最终,信号通过显现器的显存显现在屏幕上。

1.2 体系规划框图

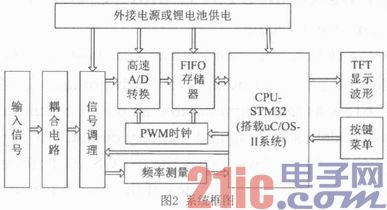

微处理器选意图法半导体的32位处理器STM32F103VET6,其内部是ARM公司的Conex—M3内核,作业主频最高可达72MHz,再在其上面移植开源的实时操作体系C/OS—II,确保体系的实时性和安稳性。由于高速A/D转化器的速度太快,STM32处理数据的速度跟不上,所以在中心参加FIFO高速缓存器。使用STM32内部自带的FSMC(灵敏的静态存储器操控器)来操控TFT液晶屏改写波形,可完成更高频率的信号的波形改写和显现。此为,使用STM32的高档定时器可输出高达12MHz的时钟,能够作为高速A/D转化器的采样时钟和FIFO存储器的操控时钟,然后防止了一大堆由有源晶振和数字芯片组成的时钟电路,体系框图如图2所示。

1.3 程控扩大电路规划

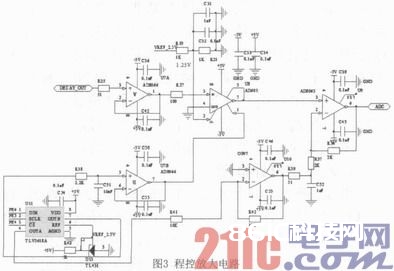

本规划的程控扩大电路如图3所示,衰减后的信号先通过的是由高功能、低噪声的电压反应型扩大器AD8066组成的电压跟从器,然后通过限流电阻R进入到压控增益扩大器AD603。AD603是ADI公司出产的低噪声、90MHz带宽的可变增益扩大器,增益以dB为线性,通过精细校准,并且不随温度和电源电压而改动。增益由高阻抗(50M Ω)、低偏置(200nA)差分输入操控;份额因子为25mV/dB,因而仅需求1V的增益操控电压就能掩盖增益规模的中心40 dB。所以改动AD603的操控电压即可改动该器材的扩大倍数。1号引脚安稳输入1.25V电压,2号引脚的电压由一片D/A转化器TLV5618A来输出。

由于后级A/D转化器ADS830的输入模仿电压规模是1.5~3.5V,基线输入电压是2.5V,为了尽量使用A/D转化器的量程,所以需求给前端输入的模仿信号加上2.5V的偏置电压。双路D/A转化器TLN5618A的别的一路输出OUTB便是为了给输入信号参加2.5V的偏置电压而规划的。相同的,为了确保这2.5V电压的安稳,中心参加反相电压跟从器。

1.4 数字收集电路规划

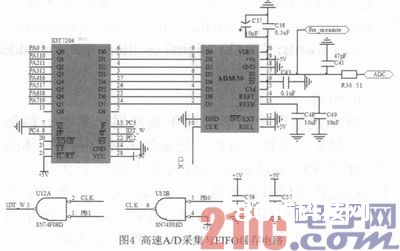

本规划的数字收集电路如图4所示,从程控扩大电路输出的信号在进入A/D前先进入的是截止频率为66MHz的低通滤波器,由于所用A/D转化器ADS830的最大采样频率是60MHz,所以它理论上能收集到的最大信号便是60MHz,为了防止更高频率的噪声影响A/D转化器作业,所以要规划这样一个低通滤波器。A/D转化器ADS830是德州仪器公司的一个8位分辨率高速A/D转化器,其采样频率规模是10kSa/s~60MSa/s。它的参阅电压源可挑选为内部参阅和外部参阅,这儿为了简化规划,选用它的内部参阅电压源。

尽管STM32主频最高高达72MHz,可是在程序里对A/D转化器收集回来的数据的处理速度实际上是比不上ADS830的60MHz采样频率的,所以为了缓冲高速数据,中心参加高速缓存器IDT7204。IDT7204是双口的SRAM,FIFO存储器,作业方式是不依托地址线,跟着写入或读取信号来对数据指针进行递加或递减,来完成对数据的寻址。IDT7204的存储深度是4K字节,有三个存储标志,这儿用到了它的“数据满标志FF”,当微处理器STM32读取FF标志,假如为低电平,证明FIFO存储器现已读取了4096个ADS830的数据,然后暂停对A/D转化器数据的读取。微处理器STM32处理当时存储区的数据;等候出来结束,再次让IDT7204读取ADS830的数据,如此循环即可得到当时示波器输入信号的完好波形数据。