在电子学中,加法器是一种数位电路,其可进行数字的加法核算。加法器是发生数的和的设备。加数和被加数为输入,和数与进位为输出的设备为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

关于加法器为什么我们都选用反相加法器,而不必同相加法器呢?

根本原因是:

同相加法器输入阻抗高,输出阻抗低 反相加法器输入阻抗低,输出阻抗高

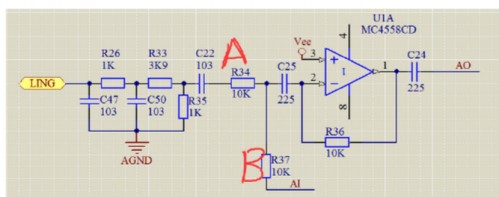

当选用同相加法器时,如A输入信号时,由于是同相加法器,输入阻抗高,这样信号不太简单流入加法器,反而更简单流入B端,而影响到B端的正常运用;相同,如B输入信号时,简单流入A端,而影响到A端的正常运用。

当选用反相加法器时,由于加法器输入阻抗低,不管是A端,仍是B端信号,更简单流入加法器,而不会影响其它路的正常运用。

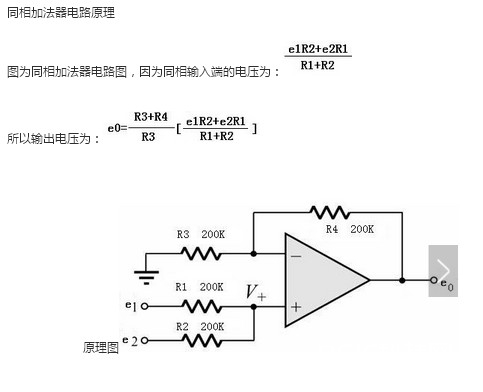

同相加法器电路原理

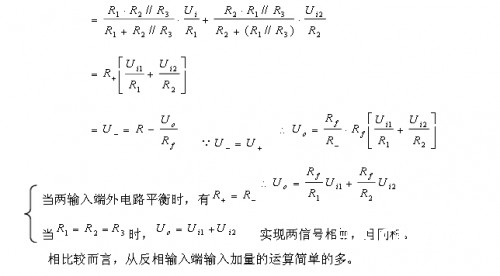

同相加法器核算