I2S(Inter-IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而拟定的一种总线标准。在飞利浦公司的I2S标准中,既规则了硬件接口标准,也规则了数字音频数据的格局。

I2S有3个首要信号:1.串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数 2. 帧时钟LRCK,用于切换左右声道的数据。LRCK为“1”表明正在传输的是左声道的数据,为“0”则表明正在传输的是右声道的数据。LRCK的频率等于采样频率。3.串行数据SDATA,便是用二进制补码表明的音频数据。

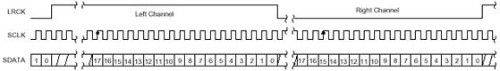

有时为了使体系间能够更好地同步,还需要别的传输一个信号MCLK,称为主时钟,也叫体系时钟(Sys Clock),是采样频率的256倍或384倍。一个典型的I2S信号见图1。

(图1 I2S信号)图1

I2S格局的信号不管有多少位有用数据,数据的最高位总是呈现在LRCK改变(也便是一帧开端)后的第2个SCLK脉冲处。这就使得接纳端与发送端的有用位数能够不同。假如接纳端能处理的有用位数少于发送端,能够抛弃数据帧中剩下的低位数据;假如接纳端能处理的有用位数多于发送端,能够自行补足剩下的位。这种同步机制使得数字音频设备的互连愈加便利,并且不会形成数据错位。

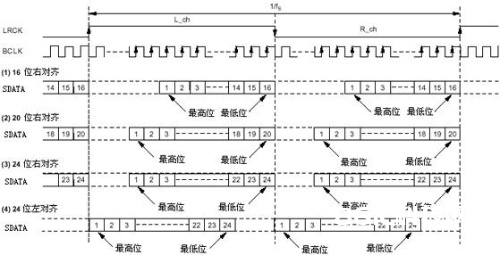

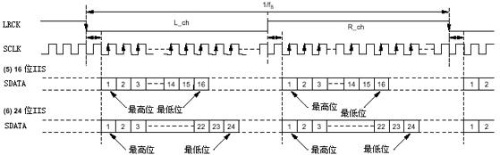

跟着技能的开展,在一致的 I2S接口下,呈现了多种不同的数据格局。依据SDATA数据相对于LRCK和SCLK的方位不同,分为左对齐(较少运用)、I2S格局(即飞利浦规则的格局)和右对齐(也叫日本格局、一般格局)。这些不同的格局见图2和图3。 (图2 几种非I2S格局,图3 几种I2S格局)

(图2 几种非I2S格局)图2

(图3 几种I2S格局)图3

为了确保数字音频信号的正确传输,发送端和接纳端应该选用相同的数据格局和长度。当然,对I2S格局来说数据长度能够不同。

I2S总线

I2S有3个首要信号:1.串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数 2. 帧时钟LRCK,用于切换左右声道的数据。LRCK为“1”表明正在传输的是左声道的数据,为“0”则表明正在传输的是右声道的数据。LRCK的频率等于采样频率。3.串行数据SDATA,便是用二进制补码表明的音频数据。I2S(Inter-IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而拟定的一种总线标准。在飞利浦公司的I2S标准中,既规则了硬件接口标准,也规则了数字音频数据的格局。I2S有3个首要信号:1.串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数 2. 帧时钟LRCK,用于切换左右声道的数据。LRCK为“1”表明正在传输的是左声道的数据,为“0”则表明正在传输的是右声道的数据。LRCK的频率等于采样频率。3.串行数据SDATA,便是用二进制补码表明的音频数据。

有时为了使体系间能够更好地同步,还需要别的传输一个信号MCLK,称为主时钟,也叫体系时钟(Sys Clock),是采样频率的256倍或384倍。一个典型的I2S信号见图3。(图3 I2S信号)图3

I2S格局的信号不管有多少位有用数据,数据的最高位总是呈现在LRCK改变(也便是一帧开端)后的第2个SCLK脉冲处。这就使得接纳端与发送端的有用位数能够不同。假如接纳端能处理的有用位数少于发送端,能够抛弃数据帧中剩下的低位数据;假如接纳端能处理的有用位数多于发送端,能够自行补足剩下的位。这种同步机制使得数字音频设备的互连愈加便利,并且不会形成数据错位。

跟着技能的开展,在一致的 I2S接口下,呈现了多种不同的数据格局。依据SDATA数据相对于LRCK和SCLK的方位不同,分为左对齐(较少运用)、I2S格局(即飞利浦规则的格局)和右对齐(也叫日本格局、一般格局)。这些不同的格局见图4和图5。(图4 几种非I2S格局)图4(图5 几种I2S格局)图5

500)this.width=500" border="0">

500)this.width=500" border="0">

为了确保数字音频信号的正确传输,发送端和接纳端应该选用相同的数据格局和长度。当然,对I2S格局来说数据长度能够不同。