导言

柔性直流输电技能是依据电压源换流器(VSC)的新一代直流输电技能,经过操控IGBT的通断来完结子模块投切状况的转化。阀控体系的桥臂操控器依据接收到的子模块16位电容电压和32位状况信息,生成子模块操控指令,并下发到每个子模块。因为子模块的数量比较多(一个桥臂为576个子模块),需求传输的数据量比较大(一共27.6 Kb),并且阀控体系对操控周期有严厉的要求(操控进程严厉操控在100μs内)。

现在的桥臂操控器遍及选用DSP+FPGA的规划架构,FPGA将接收到的数据处理后传送给DSP,DSP对数据进行毛病判别生成操控指令,FPGA读取操控指令并经过光纤发送到子模块。两者之间选用32位数据总线进行数据交互,数据传输速率低于1Gb/s,传输子模块数据大约需求30μs,占用了操控周期较长的时刻,降低了阀控体系的操控实时性。

Xilinx的Zynq-7000系列芯片将FPGA和ARM集成到一个芯片上,两者之间能够经过64位的内存映射型AXI接口进行双向数据传输,理论带宽为9.6 Gb/s。ARM和FPGA直接经过AXI4数据总线进行通讯,理论数据线宽度到达1 024位,关于突发长度,最多支撑256位,能够极大地进步FPGA和ARM的数据通讯传输率,确保体系实时运转。

本文规划的桥臂操控器选用Zynq-xc7z020芯片,运用AXI4总线替代了DSP+FPGA的数据总线,一起运用ARM双核Cortex—A9处理子体系和丰厚的外设资源,进一步提升了桥臂操控器的功用。

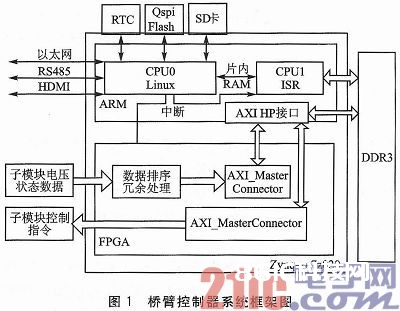

1 体系全体结构规划

本文所规划的桥臂操控器由集成在Zynq—xc7z020内的双核ARM Cortex—A9 MPCore处理器(CPU0+CPU1)所操控,这两个处理器能够一起运转各自独立的操作体系和软件程序,并且能够经过片内RAM进行通讯。

为了确保ARM对FPGA中止的实时呼应,将CPU1装备为运转裸机程序,履行中止服务函数,首要完结毛病检测和操控指令生成。而CPU0运转Linux操作体系,供给用户操控图形界面和网络通讯等功用。CPU0和CPU1经过片内256K的RAM进行数据通讯,这种双核架构称为不对称的多处理机体系(Asymmetric MultiProcessing,AMP)形式。

Zynq-xc7z020芯片的FPGA接收到子模块的电容电压数据后,进行排序及冗余处理,然后运用AXI_Master Connector的AXI总线IP核将数据转化为AXI4总线数据格式,经过ARM与FPGA的64位AXI HP(High Performance)高速接口传输到外部的DDR3中,数据传输结束后,FPGA向ARM的CPU1发送一个中止请求。

ARM的CPU1接收到中止后,从DDR3内存读取数据并进行毛病判别处理,一起告诉CPU0的Linux操作体系,在图形界面实时显现数据改变并经过网口向后台发送事情信息。

CPU1数据处理结束后,生成子模块操控指令并写入DDR3指定内存区,FPGA经过AXI_Master_Connector总线IP核从DDR3读取数据,并经过光纤发送到每个子模块。

运转Linux的CPU0作为主节点,供给HDMI图形界面,并担任体系上电硬件初始化、发动CPU1、将位装备文件烧写到FPGA中和晋级体系软件等作业。计划的全体结构如图1所示。

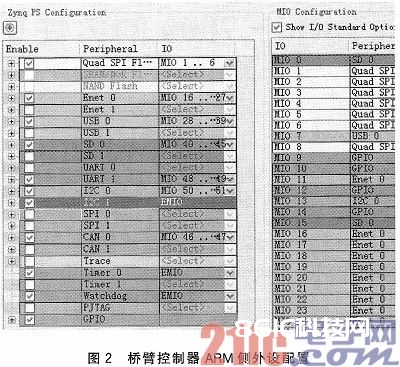

2 硬件渠道规划

桥臂操控器的硬件渠道首要分为ARM和FPGA两部分。运用Xilinx XPS硬件规划软件,装备Zynq处理器中ARM部分的外设,如图2所示。

程序代码和FPGA的装备文件固化在外部Quad—SPI Flash中,Enet0用来与后台进行网络通讯,SD0能够挂接SD卡,I2C0用来挂接RTC8564JE芯片,I2C1操控器装备HDMI输出芯片Sil9134,体系运用UART1输出调试信息。

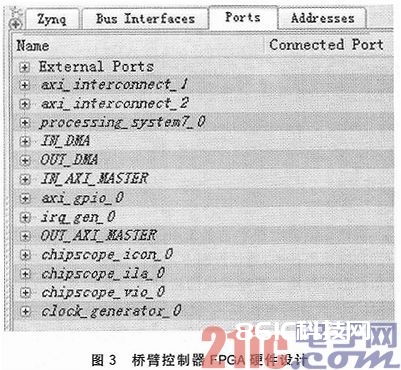

FPGA部分的硬件渠道包含数据预处理的IP核、AXI总线操控IP核(IN_AXI_MASTER和OUT_AXI_MASTER),以及发生中止的irq_gen_0 IP核,构建了FPGA、ARM和DDR3的数据流通道,如图3所示。

增加AXI总线操控IP核时,需指定AXI协议为AXI4,数据带宽为64位(最高1 024位),并将ARM与FPGA的64位AXI HP接口映射到DDR3内存的高端1 MB地址(0x3FF0 0000~0x3FFF FFFF),用来存储接收到的子模块数据以及生成的操控指令。

3 嵌入式软件规划

Zynq-xc7z020芯片是以ARM作为中心的,上电后的运转流程如下:

①进入FSBL(First Stage Boot Loader),对电路板进行装备初始化;

②将位文件烧入FPGA,FPGA依照位中的方法运转;

③进入SSBL(Second Stage Boot Loader),u-boot初始化操作体系的运转环境,引导Linux内核,随后将操控权交给双核ARM中的CPU0,CPU0担任发动呼应FPGA中止的CPU1。

3.1 FSBL软件规划

FSBL首要完结Zynq—xc7z020芯片的发动、内存的初始化、I/O的中止初始化,以及HDMI的装备。其间,HDMI接口芯片Sil9134经过I%&&&&&%1来装备。

FSBL中I2C的首要C程序如下:

//初始化I2C操控器

XIicPs_LookupConfig(…);

XIicPs_CfgInitialize(…);

//设置I2C时钟频率

XIicPs_SetSClk(…);

//发送数据

iic_writex(…);

经过装备Sil9134的0x72基址和0x7A基址两个寄存器,初始化芯片硬件,进入正常作业形式。

3.2 发动AMP作业形式

Zynq—xc7z020芯片的ARM双核同享1G的DDR3内存、512K的L2 Cache和中止操控器,为了防止双核一起拜访这些资源导致抵触,体系选用了以下办法:

①在CPU0上运转的Linux运用DDR3内存的低端768 MB空间,CPU1运用随后的255 MB内存空间,高端的1 MB空间用来存储FPGA读写的数据。

②CPU1禁用L2 Cache,CPU0上的Linux彻底占用L2 Cache。

③FPGA发送给CPU1的中止运用私有中止操控器,发送给CPU0的中止运用同享中止操控器,两者互不搅扰。