片上体系(SoC)中的电路集成推进了当今的嵌入式体系规划,人们期望将杂乱而灵敏(可编程且可装备的)的模仿、数字和处理引擎整合到一个芯片上。这个趋势使得SOC和MCU集成了各种杂乱和高档的模仿功用。这些灵敏的模仿电路不只能让咱们在规划时装备各个模块,并且还能在体系运行时动态地重新装备模块功用自身。此类多用处模仿功用可经过运用通用开关电容(SC)网络和现代SoC及MCU内置的一些模仿逻辑完成。本文将论述咱们怎么运用SC网络完成各种模仿功用,以及它们在实践运用中的实践用处。除此之外,本文还将论述SC模仿模块的原理和运用它的功用包含△Σ调-制、混频器、滤波器、积分器、加法器、减法器、DAC、可编程增益放大器、比较器、采样坚持器等等。

智能模仿

模仿电路生态体系需求电阻器、电容以及运算放大器、缓冲器、比较器、根本模仿逻辑等其它模仿模块。因为在集成电路上制作电容愈加简洁合算,然后衍生了运用开关电容模仿电阻器的技能。这些开关电容以开关的准确守时操控电容之间的电荷转移(参见图1)。内置时钟/守时操控使得模仿功用发生实时改动。这些模块有时被称为通用模仿模块(UAB)。

图1: 通用模仿模块(UAB)

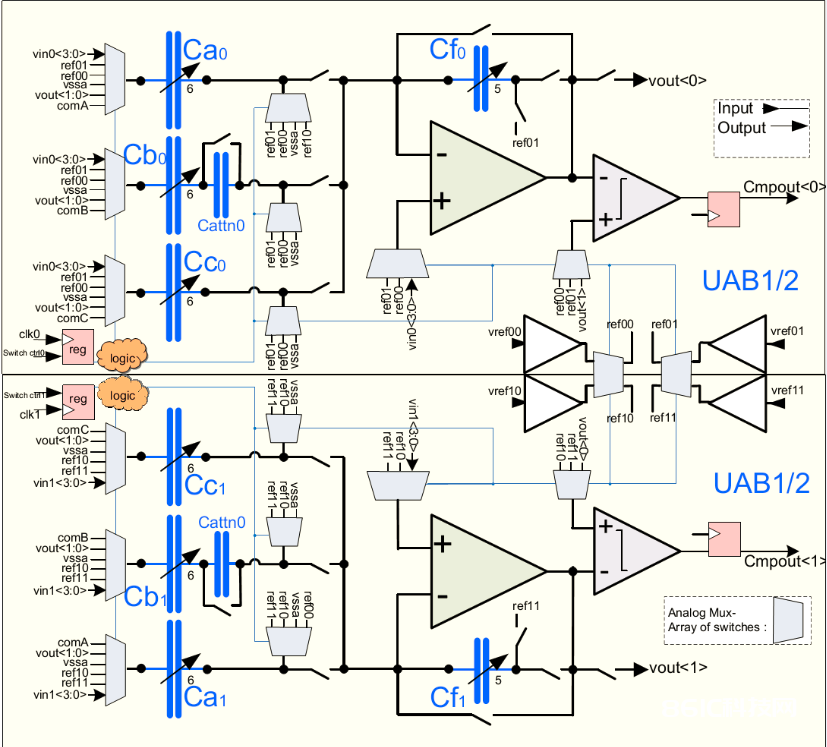

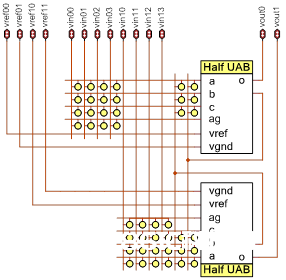

UAB由两个彻底对称的半电路构成,可装备为一个伪差分或两个单端功用。 每个半电路配有用于自主操作的操控逻辑。 图2显现了简化的UAB图。 UAB具有高度灵敏的转化和接连路由架构,能够完成模仿滤波器等杂乱的模仿功用。

图2:简化的UAB

电荷转移原理

电荷转移指的是电压节点之间的电荷受控移动。图3 显现了电阻器和开关电容中的电荷转移。

图3:简化的UAB

在电阻器中,电流(i)由电阻(R)两头的电位差构成。电流从一个电压电位(V) 经过电阻R流向地电位。遵照以下等式:

i = V / R

在开关电容中,电流 (i)是由高电位节点对电容(C)充电并向低电位节点放电构成的。当Φ1开封闭合且Φ2 s开关翻开时,电容C满电。所存储的电荷为:q=CV

当Φ1开关翻开且Φ2开封闭合时,所存储的一切电荷移动到接地节点,每个开关周期内移动一定量的电荷。假如开关的操控频率为fs,则电荷量也以该频率移动。电荷的重复移动发生电流,遵照以下等式:

i = q/t = fsq = fsCV

与电阻器不同,开关电容中的电流不是接连移动的。经过比照以上两个电流等式,咱们会发现,假如它们有相同的压降电流比,其就等效于电阻器。因而,咱们能够运用并联开关电容串联电阻器。

V/i = R = 1/fsC

等效电阻与开关频率和电容成反比。经过改动开关频率能够容易地改动电阻器的相对值。较高的C值意味着较大的电流和较小的等效电阻。与此相似,较高的开关频率 (fs) 意味着较大的电流和较小的等效电阻。 Φ1和 Φ2开关必需满意时序要求才干发生上述成果,其间包含:

1) 不要一同封闭两个开关;

2) 在封闭某个开关之前,先翻开另一个开关;

3) 挑选最大的开关频率,以便让C在周期内得到彻底充放电。

这种开关电容与运算放大器和比较器一同构成UAB。 这样开发者就能够整合多种模仿功用。 本文就解说了一个这样的模仿特性-VDAC。

VDAC Implementation VDAC的完成:

VDAC是数模转化器电路,它将数字输入转化为一个等效模仿电压。VDAC坐落许多操控体系的中心,决议了体系的功用和精度。VDAC输出电压的精度终究取决于其参阅电压。VDAC有许多运用,例如可编程电压发生器,供给传感器偏置和补偿电压、比较器参阅电压或动态输出波形。

VDAC电路的UAB开关电容拓扑如图3所示。因为开关电容模块的离散时刻特点,开关电容会对数据进行采样和缓冲以取得接连输出。 该模块支撑在MCU的作业和睡觉形式下作业。

这个拓扑结构为VDAC功用带来了灵敏性。动态Vout规模由一端的Vref值和另一端的Vagnd值决议。这能够让用户经过外部电路供给Vref和Vagnd来设置动态Vout规模。此外,增益设置可将输出规模选为Vagnd+ Vref、Vagnd+ 2Vref或Vagnd+ 4Vref,然后确保Vssa和Vdda之间的全规模可行。此VDAC带有一个13位的输入端,其输入规模由- 4096到+4095。 这些值能够直接写入相应的寄存器以收效。

图3:根据开关%&&&&&%拓扑结构的VDAC

模仿协处理器中的VDAC还支撑乘法形式,在该形式下, VDAC输出电压乘以模仿输入信号,构成一个乘积输出。乘法DAC(MDAC)是固定参阅运用的抱负模块,在此类运用中,用户期望从固定直流电压生成波形。此外,这些MDAC还合适那些用户期望数字化转化AC或恣意参阅电压的各类参阅运用。

VDAC IDE 装备:

虽然MCU供给极高的灵敏性和可编程性,开发人员仍是忧虑为了习惯他们的运用规划,还需求许多的装备寄存器和调整模块作业。PSoC Creator东西支撑模仿协处理器,可让用户方便地装备这些功用。PSoC Creator是一个免费的根据Windows的集成开发环境(IDE),能够完成并行硬件和固件规划体系。该东西的规划环境相似于乐高积木,用户能够经过双击组件将它们放置在电路图上,并装备它们的功用。图4显现了PSoC Creator中的VDAC组件装备东西,这些东西能够缩短规划周期。

图四:PSoC Creator中的VDAC组件装备东西