摘要 嵌入式DSP体系上电后发动作业,断电后中止,数据丢掉。而在许多场合,如体系毛病时,期望体系能对其作业进程中发生的状况和数据信息进行记载,以便于过后剖析。为处理该问题,文中从硬件和软件两方面具体叙说了在DSP体系中使用电可擦除存储器AT28C010进行数据记载与提取剖析的规划方案。为体系实验的过后剖析与毛病定位供给了数据支撑,且该记载办法灵敏简洁、电路规划小,具有较好的工程使用价值。

嵌入式DSP体系因其高速、灵敏、低功耗的特色,而被广泛用于信号处理及丈量技能等范畴。其的特性是加电(复位)后发动作业,而断电后中止作业,断电后其作业进程中发生的各种状况和数据信息会丢掉。这为体系实验的过后剖析和毛病定位带来了困难。为处理这一问题,选用Atmel公司的高性能电可擦除存储器AT28C010,规划了一种具有实时记载体系作业状况和数据信息功用的嵌入式DSP体系,一起使用该体系串行口完结所记载数据的下载与剖析。

1 AT28C010的功用与作业时序

芯片AT28C010是一款由Atmel公司出产的高性能电可擦除存储器,与同类产品比较,其速度快、功耗低,具有较宽的温度规模,契合军用质量等级。有望在工业、军用范畴得到广泛使用。

1.1 AT28C010的首要性能指标

容量为128×8 kbit;可重复读写次数为100 000次;数据存储时刻为10年;可在120 ns内完结数据的读取;快速的写周期为支撑页写操作,可在10 ms内完结1~128 bit的写操作;低功耗作业电流为80 mA;数据维护能有用避免误写操作。

AT28C010的电路原理框图如图1所示。

1.2 AT28C010的读写时序

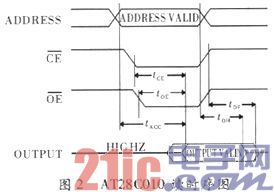

芯片AT28C010的读写操作与静态RAM相同,无需外加任何%&&&&&%,其读时序图如图2所示。

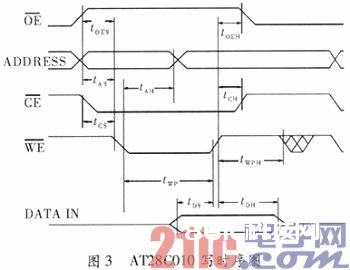

芯片AT28C010的一个字写周期可由

信号或

信号操控。由

信号操控的字写进程时序如图3所示。

一起该芯片具有页写功用,答应在一个写周期内向芯片写入1~128 bit,页写进程与字写进程相似,但在一个页写周期,字节间的写入操作时刻距离需150μs,且确保地址总线A7~A16的值不变。

2 体系组成原理

2.1 硬件完结

图4以TMS320F2407为例,芯片AT28C010在DSP体系中的使用框图。因为TMS320F2407为16位DSP使用体系,所以选用两片AT28C010构成16位存储器。

为避免DSP拜访抵触,将DSP的地址总线A15与操控总线经过逻辑操控电路与AT28C010的片选信号、写使能或输出使能相连,操控AT28C010的读写,以确保AT28C010选中时,DSP的地址总线A15为高电平。

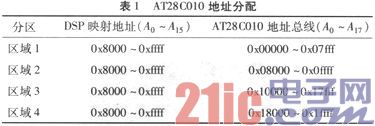

AT28C010的地址总线共17位,存储空间为128 kB,一般将其低地址线A0~A14与DSP低地址线A0~A14对应相连,高地址线A16、A15可与DSP的操控信号相连,经过对其的不同赋值,将AT8C010的存储空间分为4个区,每个区32 kB。如在实践运用中所需的记载空间较小,则可将AT28C010的地址线A16、A15接地或接+5 V,并设为固定地址。

以图4为例,AT28C010的具体地址分配如表1所示。

2.2 软件完结

在进行软件编写前需具体界说该体系在使命履行进程中所需记载数据的类型、特性、记载周期、所需存储量的巨细以及具体的地址分配等。一起,依据需求规划数据存储格局。

例如,要求以DSP上电为一次记载的开端,AT28C010需至少坚持3次完好的记载数据,每次数据记载空间要求>30 kB,需每隔20 ms记载DSP的PA、PB口状况值和1路A/D采样值。

需求剖析:为满意上述要求,将记载空间分为4个区域,每个区32 kB,具体区分如表1所示。剖析要求记载的数据,DSP的PA、PB口状况值共16位,可组合为一个字,A/D收集值为10位,独自记载为一个字,因而周期性记载的数据2个字即可满意。一起,需记载当时数据块的区域号,用于分辩当时记载区域,此为一次性记载数据。因而可设定区域1用于记载一次性数据,区域2、区域3、区域4用于记载周期性数据,并存储最新的3次数据。

完结进程:在每次DSP上电时读取区域1中存储的当时记载数据块区域号,其为前次记载的数据,当计算出数据后,存入该地址,依据该值设置AT28C010高地址线A16、A15,将地址映射到当时记载区域,并对其清0。翻开20 ms定时器中止,在定时器中止服务程序中将表明DSP的PA、PB口状况值,A/D收集值的两个字写入相应地址,20 ms的时刻距离满意AT28C010页写操作距离10 ms的要求。

3 存储数据的提取与剖析

数据的提取与剖析是树立在对要记载数据在软件需求阐明中进行具体界说基础上的。数据的提取有两种办法:经过体系串口或存储器的通用编程器。