跟着智能手机和平板电脑等移动设备的使用,电源办理技能遭到更多重视。其间,升压型DC—DC转换器以其低供电电压、低功耗、高效率、高输出电压和大输出电流等特色得到广泛使用。

但关于升压型DC—DC转换器而言,体系自身存在右半平面零点,且其会跟着负载电流的添加而逐步向低频接近。为保证体系的稳定性,一般会将体系带宽约束在右半平面零点频率的1/4~1/10处,因而体系带宽比降压型DC—DC转换器小,故芯片环路瞬态呼应也相对较慢。体系较慢的瞬态呼应会严重影响升压型DC—DC转换器的芯片功能,此外也会因在负载跳变时输出电压的较大过冲和下降而损坏输出相连器。因而,规划具有快速瞬态呼应的升压型DC—DC转换器成为重要的研究课题。

本文规划了一种增强同步升压型DC—DC转换器的差错扩大器电路,该电路可在输出负载变化时,调整差错扩大器电路的跨导和补偿,然后进步环路的带宽及环路的呼应速度,以进步同步升压型DC—DC的瞬态呼应。

1 DC-DC转换器的环路剖析

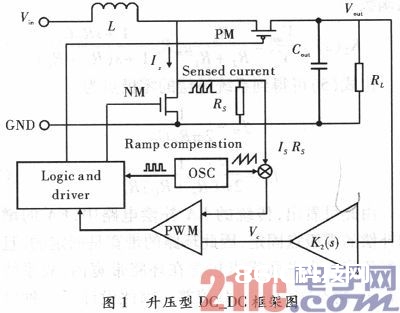

传统方法的同步升压型DC—DC转换器根本架构如图1所示,该同步升压型DC—DC转换器选用电流形式操控方法,并选用PM为同步整流管,NM为功率管。输出电压经过FB反应进入差错扩大器(EA)并与基准电压做比较,将差错信号扩大后和功率管采样信号与斜坡补偿信号之和

进行PWM比较,发生占空比信号经过逻辑和驱动电路操控功率管和调整管的开关。

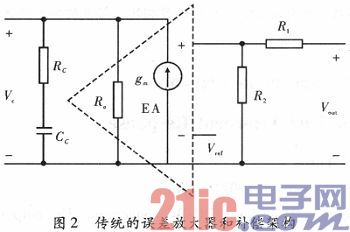

K2(s)为EA的传输函数;Is为功率管的采样电流;Rs为采样电阻;L为储能电感;Cout为输出电容;RL为负载电阻。经过跨导运算扩大电路和滞后补偿电路构成根本的差错扩大器电路如图2所示。

剖析该电流模同步升压型DC—DC的环路小信号,可得出体系环路传输函数的表达式为

由此可看出,传统的EA补偿电路中,EA的增益和补偿的零级点固定,因而环路的带宽是固定的,且为了避免将右半平面零点包含在环路带宽内,故体系带宽较小,瞬态呼应也相对较差。因而规划了一种可在负载跳变时,动态调整EA的增益及其补偿零点来进步体系的单位增益带宽,然后到达进步体系瞬态呼应速度的意图。

2 差错扩大器的电路规划

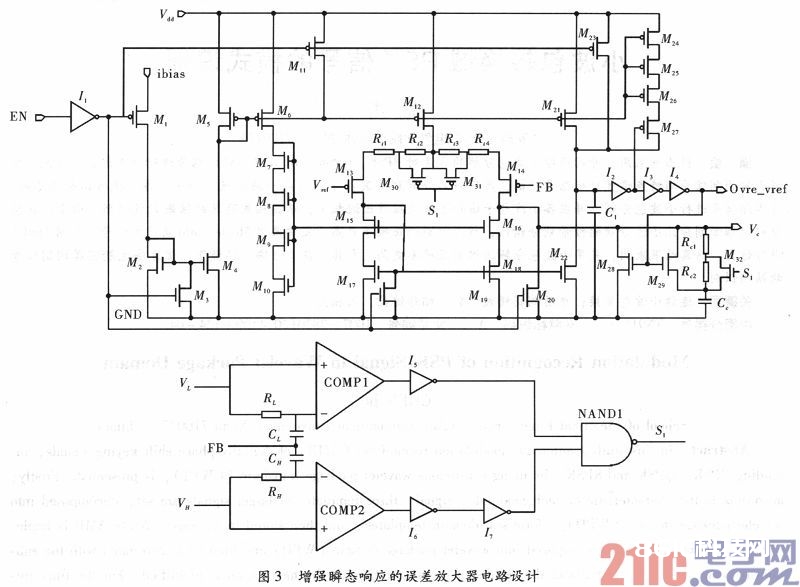

提出的增强体系瞬态呼应的差错扩大器电路如图3所示,电路中Vdd为电源电压,EN为使能操控信号,FB为输出电压的反应信号,Vref为基准电压,VL为98%的Vref电压,而VH为102%的Vref电压;Rt1和Rt22为EA的输出补偿电阻,Cc为补偿电容;Rt1~Rt4为差错扩大器输入级的源极反应电阻,且Rt1=Rt3,Rt2=Rt4;COMP1和COMP2均为一般比较器,I1~I8为反向器电路,NAND1为与非门,而RH、CH和RL、CL别离组成低通滤波电路。电路在正常状况下,FB电压根本与基准电压Vref持平,EA的输出电压Vc操控电感电流巨细。且此刻FB的电压>VL,因而比较器COMP1的输出电压为低,一起VH电压>FB,故COMP2输出低电平,此刻S1为高电平而S2为低电平,因而开关管M30~M31以及M32关,EA正常作业。而在负载跳变时,若由轻载跳变到重载,则FB瞬间变低使得比较器COMP1翻转,S1跳低而S2为高,则差错扩大器的源级随电阻变小,且输出补偿电阻变大,使得体系的带宽变大;而当负载从重载跳变到轻载时,输出电压会瞬间过冲,FB也随之升高,若FB使得COMP2翻转,则S1也将相同调低,增大体系带宽,进步体系的瞬态呼应。若FB电压过高,则信号Over_vref也将跳高,使得Vc电压被M28拉低,补偿电阻被M29短路,然后加快Vc康复正常。%&&&&&%C1为保证正常状况下Over_vref为低,而当FB过高时,M27地点支路关断,可快速将C1电压拉低,使Over_vref跳高,然后避免输出电压过冲较大。

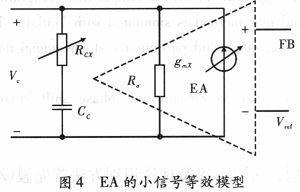

该差错扩大器的等效电路如图4所示,其间补偿电阻RCX等效为可变电阻,而EA的跨导等效为可变电流。

可得出在负载跳变和正常状况下的传输函数别离为

其间,RO为EA的输出电阻,gmX为EA的跨导,RCX为补偿电阻。正常状况下,gmX=1/(Rt1+Rt2),RCX=RC1;而在负载进行跳变的状况下,gmX=1/Rt1,则RCCX=RC1+RC2。由此可看出,比较正常状况,负载跳变时体系的增益进步,一起零点方位提早而极点方位后移,体系的带宽展宽。

3 仿真成果

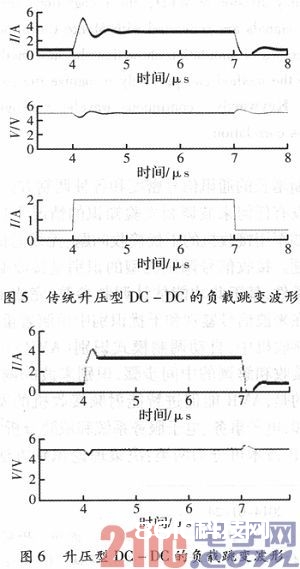

关于该同步升压型DC—DC转换器,在0. 25 μm CMOS工艺条件下,使用Cadence仿真东西进行仿真验证,其仿真环境为:电源电压Vin= 3.6 V,输出电压Vout=5 V,负载的跳变规模为500 mA~2 A。图5为传统升压型DC—DC的负载跳变波形,图中IL为电感电流,Vout为输出电压,而Io为负载电流。可看出其康复时间为55μs,负载跳变时的输出电压过冲和下降为600 mV。图6为本文提出的具有增强瞬态呼应EA的升压型DC—DC转换器,其康复时间为30μs,而输出电压的过冲和下降为380 mV。从图中可看到,体系的瞬态跳变康复时间比传统的同步升压型DC—DC转换器减少了45%,且输出电压的上冲和下降值也减少了35%。