规划尺度的添加趋势势不可挡,这也一向是EDA验证东西的一个沉重负担。动态功率预算东西便是其一。

总有一些影响要素诱使着客户频频晋级他们的移动设备。其间包含更多功用和改善的用户体会,更具吸引力的用户界面,更轻的分量、更耐久的电池寿数等等,不乏其人。从各方面考虑,好像耐久的电池寿数位居第一,而更长的电池寿数直接关系到更低的功耗。

自从五十年前Noyce和Kilby创造平面集成电路以来,微电子产品的功耗阅历了一段安稳下降期。平面技能使得缩放(缩小)固态器材成为可能。晶体管尺度越小,同一区域内包容的晶体管数量就越多,切换速度就越快,所耗费的能量就会越少,而芯片运转时的温度也会越低(相较于相同数量的晶体管而言)。

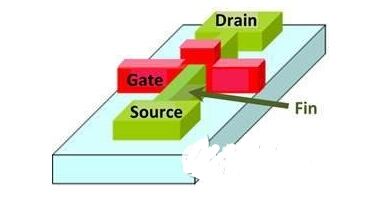

“Doublegate FinFET”,作者:Irene Ringworm,发布在英语维基百科上。经过维基共享资源根据CC BY-SA 3.0协议取得授权。

在历史上,微电子产品开展的衡量标准一向着眼于场效应晶体管中源极和漏极之间硅通道的长度(被称为工艺技能节点)。上世纪60年代初,该节点为50微米。十年后,这一数字下降到了1微米以下,而到了2003年,则到达100纳米以下,敞开了纳米技能年代。

在前二十年,因为漏电问题,晶体管未切换且空闲时的静态功耗远小于晶体管切换状态下的动态功耗,小到能够忽略不计。到了180纳米时,静态功耗开端飞速上升,到了2005年,因为节点降到了65纳米以下,静态功耗超过了动态功耗。

不用忧虑。FinFET或3D晶体管的创造及时地拉住了滑向消失深渊的平面晶体管。

FinFET估量可削减多达90%的静态走漏电流,而且仅运用等效平面晶体管50%的动态功率。与平面等效晶体管比较,FinFET晶体管在平等功耗下运转速度更快,或在平等功用下功耗更低。有了FinFET,规划团队能够更好地平衡产值、功用和功率,满意各个应用程序的需求。

功率预算应战

如前所述,更低的工艺节点带来了更高的晶体管密度,这使规划团队有机会在其间参加越来越多的功用。现在,在最大型的规划中,晶体管数量超过了100 亿。惋惜的是,规划尺度的添加趋势势不可挡,这也一向都是 EDA验证东西的一个沉重负担。动态功率预算东西便是其一。咱们能够假定,电路的动态功耗与电路在运转时产生的逻辑转化次数成份额。因而,要精确地估量和优化数字电路的功率,咱们需求记载每个时钟周期内每个规划元素的切换活动,并将该活动馈入东西履行功率相关的使命中。

在不盯梢相应周期的情况下记载切换活动可取得运转时段内的均匀功耗。经过添加按周期记载的信息能够盯梢峰值功耗。

咱们直觉上会假定记载切换活动的精确性会跟着规划阐明从高层次笼统下降到门级,进而又下降到晶体管级而添加,原因是可用的规划详细信息越来越多。

现在的窘境是,在电子体系级(ESL),规划人员在对比多个架构、多种场景或软件算法并完结最佳功率优化计划上具有了史无前例的灵活性。糟糕的是,在阐明等级,功率预算却不行精确。在门级,能够取得的详细信息很少,灵活性也十分有限,仅可支撑完结边际优化,在晶体管级更是如此。而在寄存器传输级 (RTL),好像能够完结最佳折中。既能够取得满足的详细信息来完结功率的恰当预算,又有满足的灵活性来完结较大的功率优化。

动态功耗在很大程度上取决于应用于其首要输入设备的鼓励或在嵌入式SoC规划年代由嵌入式处理器履行的嵌入式软件所触发的规划内的活动。也就是说,经过发动操作体系或履行驱动程序、应用程序或确诊。

比如模拟器和仿真器等验证引擎是用于盯梢切换活动的完美东西。要提示的是,模拟器的履行速度首要取决于规划等级阐明、规划巨细和应用于规划的鼓励类型。为了减轻并消除此类依靠,一起为了处理嵌入式软件,只要仿真器能够在合理的时刻段内履行这一应战性使命。

到现在,预算功耗一向选用两步法:第一步,模拟器或仿真器会在一个交流格局 (SAIF) 文件中盯梢并累积整个运转过程中的切换活动,或在快速信号数据库(FSDB)文件中按周期记载每个信号的切换活动。第二步,运用一个馈入SAIF文件的功率预算东西核算整个电路的均匀功耗,或运用馈入FSDB文件的功率预算东西核算规划时刻和空间内的峰值功率。

上述机制关于SoC规划而言有两个问题。SAIF和FSDB文件巨大且简直无法办理,且需求长时间保护。在十亿门规划年代,这两个问题结合在一起使上述办法没有了用武之地。