摘要:文章介绍了一种可编程的频率电压改换电路(F/V),将频率信号经过杂乱可编程逻辑器材(CPLD)改换为与频率成正比的脉宽信号,脉宽信号操控模仿开关对基准电压信号进行斩波,斩波信号经低通滤波后输出直流电压信号。

0 前语

电气自动化和进程自动化及自动检测范畴常常用到频率电压改换器F/V,需求将频率信号转化为电压信号。F/V改换器的完成办法一般有3种:一是依据专用F/V转化芯片(如LM331),二是依据模仿电路,三是依据微处理器和D/A转化器。前两种F/V改换器的一起缺陷是量程单一,频率改换规模不能在线改动或不能方便地改动。第三种F/V改换器需求较高速度的微处理器和高分辨率D/A转化器,本钱较高。本文介绍一种依据CPLD的可编程F/V改换电路,该电路简略、频率改换规模可任意接连设置、精度高,具有较好的实用价值。

1 电路的根本原理

F/V改换电路的根本结构,频率信号经K分频电路转化为占空比为50%的方波信号;方波信号经频率/脉宽改换电路转化为脉宽与频率成正比的脉冲调宽信号;脉冲调宽信号的高电平操控模仿开关与电压基准接通,低电平操控模仿开关与信号地接通,模仿开关的输出经低通滤波器将脉冲宽度信号转化为直流电压信号。

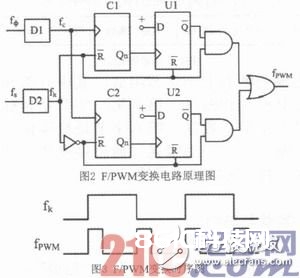

图2为F/PWM改换电路的原理图,fs为被改换频率信号,f0为参阅时钟信号,D1为M分频器,D2为K分频器,C1、C2为n位二进制计数器,U1、U2为上升沿触发的D触发器。当K分频器输出fk为0时,计数C1器清零,U1触发器的输出置1,当fk为1时,计数器C1在M分频器的输出fc的效果下增量计数。当计数器C1计数由N-1变为N时,其计数器C1的Qn脚输出由0变为1,触发D触发器1的输出为逻辑0。当K分频器输出fk为1时,计数C2器清零,U2触发器的

输出置1,当fk为0时,计数器C2在M分频器的输出fc的效果下增量计数。当计数器C2输出由N-1变为N时,其计数器C2的Q脚输出由0变为1,触发D触发器U2的

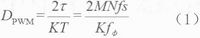

输出为逻辑0。两组计数一触发电路逻辑相反,经过逻辑组合输出得到脉宽与频率fk成正比的输出波形fPWM。频率脉宽改换时序图如图3所示。

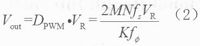

设被改换频率信号fs的周期为T,则K分频信号fk的周期为KT,脉宽调制信号的宽度为τ,设计数器对fc的计数为N,则τ=MN/f0,脉宽调制信号fPWM的占空比DPWM与fs成正比。

因为DPWM≤1,所以被改换信号的频率上限fsmax为Kf0/2MN,明显,经过改动分频数M或K或计数值N,均可改动被改换的频率上限。

图4为将PWM信号改换为直流电压信号的原理图。PWM信号的高电平操控模仿开关与电压基准VR接通,低电平操控模仿开关与信号地接通,模仿开关的输出经低通滤波器将脉冲宽度信号转化为直流电压信号Vout。

2 试验成果

选用Xilinx公司的CPLD芯片XC9572来完成图2描绘的逻辑功用,将频率信号改换成脉冲宽度信号。CPLD输出的与频率信号成正比的脉冲宽度信号连到模仿开关ADG408芯片的1脚,作为通道挑选信号。基准电压信号VR为5V且连到ADG408的5脚,ADG408的8脚输出的电压信号经低通滤波电路滤波,输出与频率信号成正比的直流电压信号Vout。参阅时钟f0的频率为80MHz,CPLD内部D1和D2为2分频器,C1、C2为12位二进制计数器,基准电压信号VR为5V,依据公式fsmax=Kf0/2MN,可改换的最大频率为19.531kHz。不同参阅时钟分频数M对应的频率信号改换规模如表1所示。不同计数器计数值N对应的频率改换信号规模如表2所示。

3 定论

本文介绍了一种依据CPLD的可编程频率电压改换电路,该电路先将频率信号转化成PWM信号,再将PWM信号转化成对应的直流电压信号。因为使用了可编程的逻辑器材,本电路简略、频率改换规模可任意接连设置、精度高,具有较好的实用价值。