现在,天基电子体系开发人员面对的压力越来越大,在项目日程安排越来越严重且预算再三削减的状况下,他们却需求供给更高的体系功用。但是,天基体系具有一套共同而严厉的尺度、分量和功耗(SWAl?)约束,这关于规划人员来说无疑是一个扎手的问题。

为到达事半功倍的作用,各大公司纷繁选用FPGA等商用制品(COTS)器材。从SWAP约束、本钱与作业效率方面来说,可重构的FPGA所固有的灵敏性为天基体系的开发人员供给了巨大的协助。

充分运用现有工程规划与预算资源的一种办法是创立能布置到多个太空使命中的灵敏的有用负载。SEAKR工程公司选用可重构的赛灵思Virtex FPGA创立了灵敏的高功用核算渠道作为各种天基体系的中心。运用该可重构的汁算(RCC)办法,可在多个太空使命的SWAP、本钱与时刻约束范围内完结高要求的功用方针。最有目共睹的比方包含:SEAKR为美国雷神公司(Raytheon)的先进反响战术效能军用成像光谱仪(Artemis)开发的板载处理器、可编程太空收发器以及现在尚在开发过程中的可编程太空IP调制解调器和猎户座视觉处理器。

运用独立处理器的架构

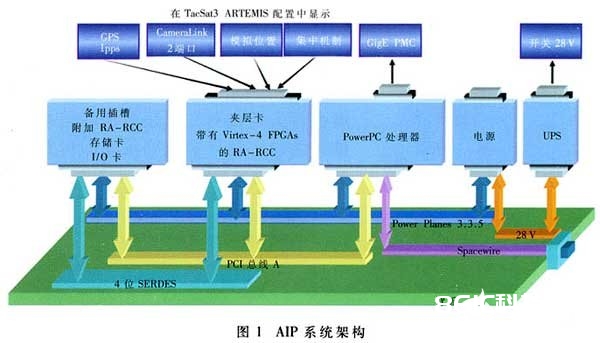

这款全新渠道称为运用独立处理器(AIP),在灵敏、可扩展的架构中集成了一系列标量处理器与RCC,可支撑开放式规范,如图1所示。因为该处理器具有灵敏的I/O架构,可以?昆搭各种板卡以创立最适宜运用要求的不同装备,称之为专门使命功用。AIP运用赛灵思根据SRAM的FPGA的共同功用,答应在轨重构,然后取得更高的灵敏性与SWAP优势。Ail?还支撑各种抗单粒子效应(SEE)辐射技能,保证在不同轨迹中都可以牢靠地进行操作。

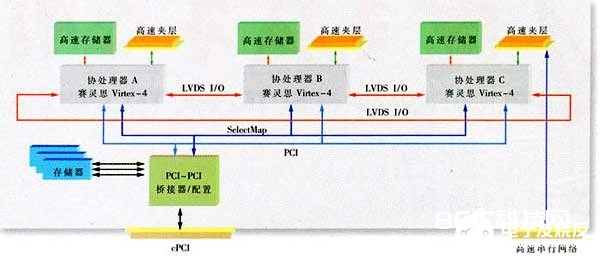

AIP体系架构的中心是一块可重构的核算机板卡,其上包含3个Virtex-4 FPGA,如图2所示。SEAKR对现在可用的组件进行了调研,结果表明Virtex FPGA是专一能到达功用方针并具有航天飞翔特性要求的设备。针对要求最严苛的运用,赛灵思供给了Virtex-4QV太空级设备。这些太空级FPGA 选用了与商用级FPGA相同的架构,但经过特别处理和挑选以到达Q类与V类要求。

ViHex-4 FPGA经过与次序处理器和谐作业,可充任协处理器以加快要害处理密集型使命的发展。三重FPGA板的架构具有高度的灵敏性,可满意不同使命的共同需求。例如,在抗SEE技能中运用3个FPGA,可满意该技能对组件级冗余性的要求;多个设备间同享一个大型协处理器并运用环形总线经过LVDS接口衔接3个 FPGA,可完结设备间的高速通讯。选用扩展的6U外形,板卡大将有2个衔接器用于板卡间通讯:一个用于CompactPCI背板,另一个用于高速串行网络。

每个FPGA都可直接拜访RCC板上的专用高速存储器以及支撑经过高速夹层卡进行扩展与定制的衔接器。运用此架构,可以运用特定I/O、存储器、模仿电路乃至附加逻辑来扩展RCC板的功用。特定运用中的抗SEE辐射架构的组件夹层卡,经过3个衔接器与RCC板衔接起来,每个衔接器可供给170 LVDS I/O。

将特定使命的功用模块移动到夹层卡,可以在多种共同运用中运用相同的根据FPGA的处理卡。该通用架构有助于下降项目风险、削减本钱并缩短时刻。

FPGA中的抗辐射效应

根据SRAM的装备电路在遭到辐射时极易发生翻转,因而在太空中飞翔的根据FPGA的可重构体系需求给予特别考虑,以保证其在高辐射环境中牢靠运转。首先要考虑组件的挑选。除了工业和军事温度级选项外,赛灵思还供给V级Virtex-4与Virtex-5 FPGA,这些FPGA经过特别处理,可以避免因辐射而导致的闭锁现象,保证总剂量辐射效应下的功用。这些器材还能饱尝中子和质子i七束的进一步锻炼,牢靠地预测出特定轨迹上单粒子翻转(SEU)及单粒子功用中止的频率。此数据可辅导工程师挑选适用于运用与轨迹的抗翻转计划。

可重构FPGA的抗翻转功用一般需求组合运用硬件三重冗余与装备存储器铲除。硬件三重冗余包含三重要害电路,即便在某一组件发生辐射引发的翻转后也能保证接连运转。此外,它还增加了一个表决电路,该电路将来自3个逻辑分支的、信号进行比较并回绝因翻转而发生的无效信号。

规划人员可从一系列计划中进行挑选,以满意体系功用与可用性要求。其间一种办法是运用冗余FPGA与一个抗辐射的外部表决电路。另一种办法是设备级抗辐射,即在一个FPGA中装备三重要害使命逻辑并运用相关联的表决电路。传统上,工程师手动完结三模冗余(TMR)规划办法。现在,赛灵思供给了专门的规划东西,可在FPGA内主动完结,FMR。挑选抗辐射计划时,会遭到一些要素的影响,比方方针电路的尺度、选定轨迹中的辐射等级及电路的运转时刻要求等。

存储器铲除的基本概念是比累计翻转次数更频频地重写装备存储器。规划人员可从一系列存储器铲除办法中进行挑选,以习惯不同的翻转频率与运转时刻要求。最简略的办法便是将完好比特流从头加载到装备存储器中。该办法开支低,但要求电路至少在1个装备周期内坚持不作业。关于在运转时刻方面要求更严厉、翻转率更高或一起存在这2种状况的运用,还可选用更高档的办法。例如充分运用VirtexFPGA的部分重构功用,包含检测存储器翻转然后只重构存储器阵列的选定子集的电路。

AIP运用现状

AIP架构已成功运用于4个不同的太空使命。经过组合运用根据FPGA的RCC板与灵敏的夹层卡,工程师可以快速构建各种处理与通讯体系并施行适宜每次太空使命共同要求的抗辐射计划。

第一个选用AlP的实在产品是先进的反响战术效能军用成像光谱仪Artemis,该设备将在计划于2009年第2季度发射的TacSat-3卫星上运转。Artemis旨在供给战场情形认识,它运用卫星搜集的数据履行先进的印象处理,然后经过窄带下行链路将这些印象传送给现场的战士。工程师认识到,需求选用RCC计划才干满意太空船对尺度、分量和功耗的要求:巨细为7.8×11.41×10英寸;分量为18英磅;功耗为40W(硬约束为50W)。

Artemis体系中,2个Virtex-4 FPGA担任履行传感器数据收集与校准等预处理功用,,根据Micro-BlazeTM软处理器内核的嵌入式处理体系可和谐存储器拜访与处理器调整,而 PowerPC单板核算机用于完结印象生成与方针提示。图1显现了Artemis体系架构。

因为印象数据途径不是要害使命型,所以装备存储器铲除为Artemis供给了适宜的抗辐射功用。规划人员无需采纳3个逻辑或冗余设备就可以满意可用性要求。不只如此,还可以运用商用级FPGA来构建闪存;每个比特流都装备FPGA以处理特定波形和频率。这样,体系将可以运用最少的硬件数来支撑多种波形,如表1所示。

高度灵敏的RCC板为初始体系开发前期带来了许多优势。恳求与接纳一系列频隙之间的延迟时刻或许超越一年。运用可重构的硬件,规划人员可以在接纳到这些频隙之前着手开发,然后下降了体系本钱。2个Virtex-4 FPGA同享印象处理作业负荷,而第3个FPGA保存闲暇以最小化功耗。

AIP初次运用后极大地进步了作业效率,明显下降了一次性工程费用,然后使接下来的每个项目都能节约约一年的开发时刻。

RCC协助完结灵敏的收发器

AIP的第二个太空使命运用是可编程卫星收发器。PST体系供给了可在多个无线电波段进步行频率捷变卫星通讯的功用。SEAKR工程师最终得出的结论是,即便是高端的PowerPC处理器也无法在SWAP要求(即3.86×6.85×7英寸、10磅以及10W的接纳功耗与45W发射功耗)的范围内供给必需的重吊才能。

为了满意上述要求,规划人员运用Vinex FPGA的体系内重构功用。该体系在频谱分配中存储多个装备比特流,以完结所需频率。此外,该功用还可使开发人员修正体系以满意后续使命要求。SEAKR 正在为未来的布置开发更多的波形。

PST使命的实质是简化了抗辐射要求。通讯体系坚持对通道的端对端操控,一起还可以容许数据过错:一旦数据呈现损坏,体系将从头传输受影响的数据包。该固有的容错功用意味着装备存储器铲除为操控途径供给了适宜的抗SEU辐射功用。为了维护中心处理结果,在夹层卡上设立了3个存储器。

为了完结体系,需将AIP板与RF模块、电源模块经过扩展的6U形底板衔接起来,该底板可接受轰动及发射时的其他压力。

太空中的因特网

太空中的分组网络有望供给与地上网络相同的灵敏性和稳健性。长期以来,可重构的FPGA一直是干流的有线网络设备,正如在可编程卫星因特网协议调制解调器中所展现的优势相同,它可为天基运用供给杰出的功用、高度的灵敏性并能加快规划进程。PSIM可从规范卫星通讯波形中提取以太网帧,一起还便于太空船上的IP路由。运用分组卫星通讯,可经过虚拟电路来路由与电子束和波形无关的数据。与规范弯管式卫星通讯通道比较,分组网络进步了可扩展性与流量,完结了涣散式多播,且满足灵敏,可以供给超卓的服务质量。

PSIM包含12个贴装在4个RCC卡上的Videx-4V FPGA,以及坐落坚固耐用的底板上的2个次序处理器与1个模仿开关卡。FPGA担任履行波形处理,而次序处理器供给以太网接口和分组交流功用。

该太空使命在可用性方面要求选用比Artemis或PST中运用的抗辐射才能更强的计划。因为过错康复需求很长时刻,并且还会下降可用性,不能到达方针要求。因而,体系有必要可以供给不间断的端对端操控。SEAKR工程师施行了一种既可实时纠正过错又可供给不间断服务的抗辐射计划。

在每个RCC板上的3个设备中设立了三重FPGA逻辑。夹层卡上的抗辐射逻辑设备充任主力表决器。在后台进行存储器铲除操作,这对网络操作而言是彻底通明的。此外,夹层卡还供给到路由器的物理接口。

选用PSIM的太空使命计划于2009年第2季度发动。

载人航天的高功用视频

AIP架构的最新运用是猎户座载人太空船的视觉处理单元(VPU)。VPU可为处理印象算法供给可重构的渠道,有利于位姿估量、光学导航以及紧缩/ 解紧缩。该体系从星象盯梢仪、视觉导航传感器、空间对接照相机以及情形认识摄像机等各种传感器处接纳印象数据。

处理如此巨大的数据需求结合次序处理器与根据FGPA的RCC卡。Virtex-4 FPGA可施行功用辨认、图形掩盖、平铺以及视频紧缩等视频处理算法。此外,它们还集成了MicroBlaze软处理器内核以和谐算法中心和处理器通讯。根据LEON容错处理器的单板核算机旨在和谐体系、处理过错、装备与监控RCC并操控互连。

夹层卡供给传感器接口,施行与一切3个FPGA相连的LVDS链路,最大极限地进步视频流挑选与抗辐射计划的灵敏性。

因为VPU所履行的使命“受监测入片面约束”,SEAKR工程师挑选了Virtex-4QV太空级FPGA,并施行了更强壮的抗辐射计划。经过结合运用TMR办法和装备存储器铲除,可保证通明地纠正操控途径过错。

总归,经过Virtex FPGA,SEAKR工程师不只已为太空运用开发了运用独立的处理器,一起还在屡次太空使命中展现了该处理器的高度灵敏性。RCC在根据卫星的印象处理与通讯、高灵敏性的无线电通讯、天基网络以及人类太空飞翔导航等领域中充任了首要组件。

太空级Virtex FPGA是COTS组件,可为要求严苛的数据处理和通讯体系供给所需功用。运用这些可重构的FPGA,可树立高灵敏性可扩展架构,然后下降开发本钱并缩短规划周期。除了支撑快速开发与灵敏的地上制作外,Virtex FPGA还供给在轨重构功用,然后可取得更多明显的SWAP优势。

新一代的V级可重构FPGA可供给更高的逻辑容量、更高的硬化IP块集成度、更高的功用以及更低的功耗,因而可取得更多尺度、分量和功耗等方面的优势。抗辐射可重构的Virtex FPGA消除了逻辑级或设备级的冗余施行,这不只简化了规划人员的作业,一起还进一步扩展了SWAP优势。

责任编辑:gt