1 布景常识

跟着信息技能的开展,特别是各种数字处理器处理速度的进步,人们对数据收集体系的要求越来越高,特别是在一些需求在极短时间内完结很多数据收集的场合,对数据收集体系的速度提出了十分高的要求。

为了完结高速、接连采样的数据收集体系,本文介绍了一种依据 FPGA +AD7609的数据收集体系的构成及技能完结。选用 FPGA 作为主模块,AD7609为数据收集模块,并规划了硬件完结电路。

试验测验成果标明,体系结构灵敏,性价比高,数据收集能力强,各项目标均达到了规划要求,具有广泛的实用性。

2 数据收集体系的完结

2.1 体系硬件规划

2.1.1 主控模块FPGA

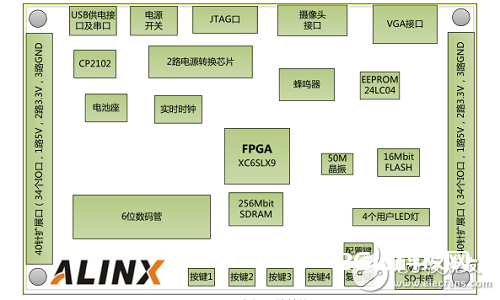

在本规划中,FPGA主控模块运用Xilinx公司的Spartan-6产品,型号为XC6SLX9-2FTG256C。规划中运用了该系列的黑金FPGA开发板,有效地进步了开发规划进展。开发板体系结构图如下图1所示。

图 1 开发板体系结构图

FPGA模块为整个体系的中心操控部分,运用硬件描绘言语Verilog HDL对FPGA进行程序规划,以完结体系的全体功用要求。

2.1.2 数据收集模块AD7609

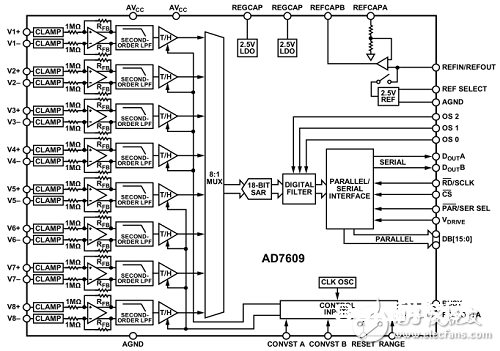

AD7609是一款18位、8通道、真差分、同步采样模数数据收集体系(DAS),该器材内置模仿输入箝位维护、二阶抗混叠滤波器、盯梢坚持放大器、18位电荷再分配逐次迫临型模数转化器(ADC)、灵敏的数字滤波器、2.5 V基准电压源、基准电压缓冲以及高速串行和并行接口。其功用框图如图2所示。

图 2 AD7609功用框图

AD7609选用5 V单电源供电,能够处理±10 V和±5 V真双极性差分输入信号,一起一切通道均能以高达200kSPS的吞吐速率采样。

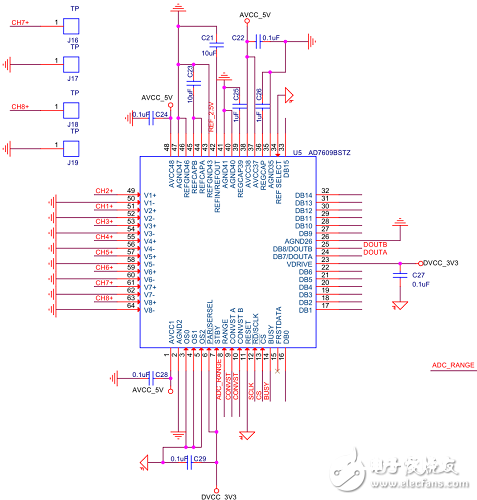

在此次规划中,将AD的作业方式设置为串行数据收集形式,采样率设为最高速率200kSPS,参阅电压为内部基准形式,规划的电路原理图如下图3所示。

图 3 AD7609原理图规划

AD7609的操控端口,衔接到FPGA操控模块,通过Verilog程序进行数据的收集和操控。

2.1.3 硬件电路的完结

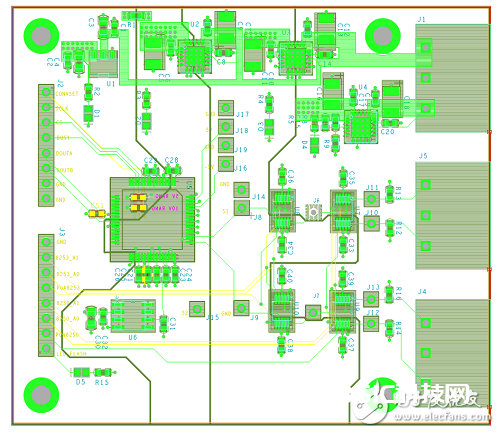

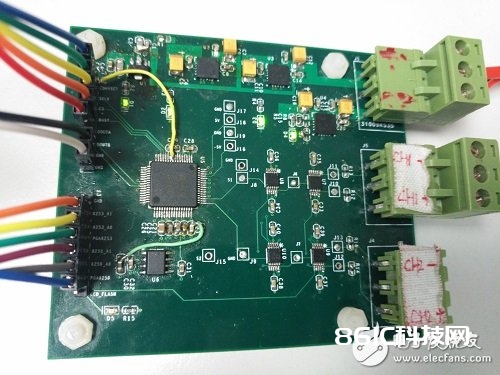

本规划中,运用Cadence软件规划了AD收集电路,进行了什物焊接和验证。其印制板PCB电路图如下图4所示。

图 4 印制板PCB电路图

焊接完结,并调试成功的什物图如下图5所示。

图 5 前端什物电路图

其间AD7609的操控引脚,通过排线与FPGA的IO口衔接,被收集信号,从右边的CH1和2端口输入。

2.2 体系程序规划

2.2.1 程序流程规划

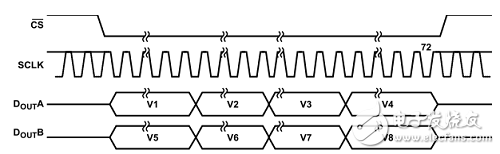

本规划中,将AD7609的作业方式装备为串行形式,采样率200kSPS,对应的串行形式采样时序如下图6所示。

图 6 串行形式的采样时序图

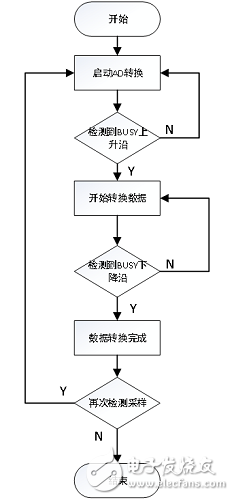

通过FPGA规划AD收集转化程序,依据AD7609采样要求与作业特性,规划了如下图7所示的AD采样流程图。

图 7 AD7609采样流程图

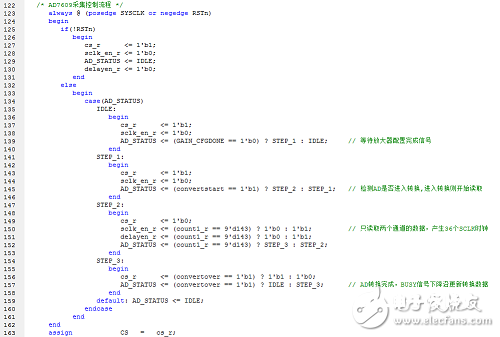

2.2.2 AD7609程序规划

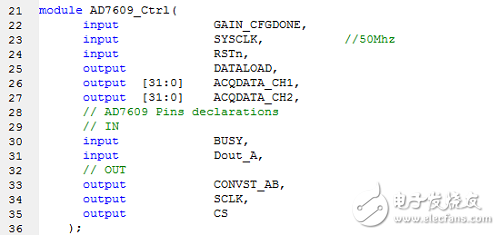

AD7609能一起满意8通道的200kSPS采样,在本规划中,对通道CH1和CH2进行程序操控和规划。模块接口源程序如下图所示。

图 8 AD7609模块接口程序

AD7609收集操控流程源程序如下图9所示。

图 9 AD7609收集操控流程程序

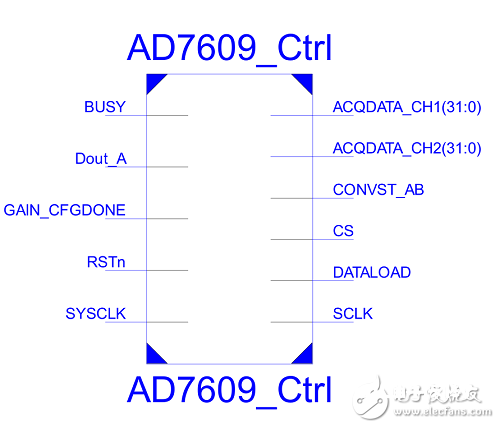

综合该模块后的RTL电路图如下图10所示。

图 10 AD7609模块的RTL图

2.2.3 仿真验证

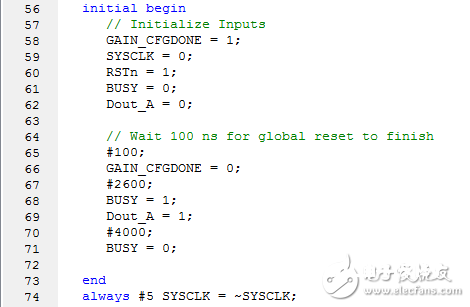

选用ISE14.7内部的仿真软件进行仿真验证,中心测验源程序如下图11所示。

图 11 仿真测验源程序

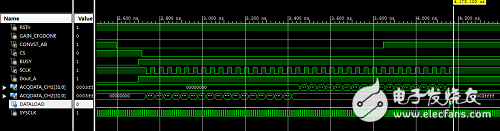

对用的仿真成果如下图12所示,可见完整地完结了对AD7609的功用操控。

图 12 程序仿真验证成果

2.2.4 实测验证

首先在作业区中装备ChipScope在线调试软件,增加需求观测的数据。然后,通过该调试软件,将程序下载到主控模块的FPGA中。

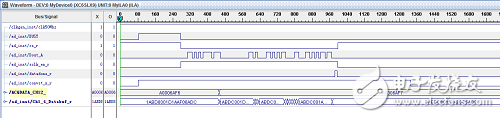

运用ChipScope在线调试软件抓取实时数据,验证硬件模块的正确性,得到如下图13所示的AD7609数据采样成果。

图 13 什物数据采样成果

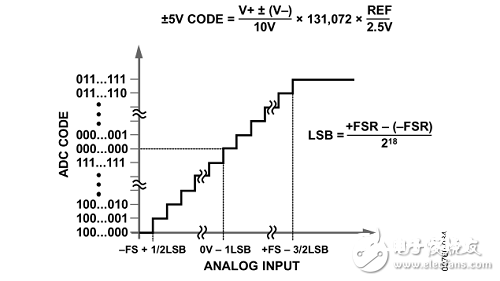

本规划中,AD7609的数值转化的核算公式如下图14所示。

图 14 AD7609数值转化公式

对应图13中的数据核算进程为:(6Af6)H = (27382)D,采样得到的数值V=27382*10/131072 = 2.08908V,与实践输入电压共同。

3 结语

通过试验测验和核算,充沛验证了本体系规划的合理性和有效性。试验数据标明,该数据收集体系运转安稳牢靠,完结了对高速数据的接连采样。