导言

航空电子体系之间以传递状况数据和操控数据为主,由于数据量不非常巨大,对传输速率要求并不高。例如,最盛行的航空总线ARINC 429和1553B总线,速率分别是100kbps和1Mbps。而跟着飞翔练习强度和精度的进步,飞翔实验和练习进程的多通道视频画面需求实时记载下来以便进行过后剖析评价和体系规划改善。与传输状况操控信息比较,这些视频数据是巨量的,对航电体系的海量存储和数据高速传输都提出了更高的要求。本文提出一种航空视频收集记载体系的规划计划,选用速率高达2.5Gbps的PCIe总线构建体系,PCIe总线既有高速的数据传输才干,又有杰出的外设接口,有利于大容量信号的实时传输。有用处理了机载多通道视频数据的实时收集与记载,为航空练习使命体系的过后评价和功用剖析改善供给了快捷的手法。

1 、体系的计划规划

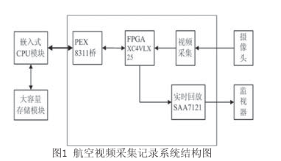

在航空视频收集记载体系中,摄像头把载机使命体系的实时画面视频数据按预订格局组帧,通过LVDS信号总线传输给视频收集模块;通过视频收集模块对LVDS信号电平进行改换处理后,将单端视频数字信号送给可编程逻辑器材(FPGA)进行视频解码处理。解码后的数字视频,一方面通过SAA7121视频编码器直接送给监视器,让飞翔员实时把握练习状况与作用:另一方面通过高速PCIe总线传送给嵌入式CPU模块进行视频数据紧缩存储,供过后剖析。航空视频收集记载体系整体结构如图1所示。

2、 体系的硬件规划

体系的硬件规划首要会集在各个功用模块的电路规划上,是软件规划和体系调试的渠道根底。硬件规划应该确保体系运转的高可靠性,在满意要求的前提下,尽量削减可编程逻辑、体系软件的规划与调试的难度。

2.1 视频数据收集

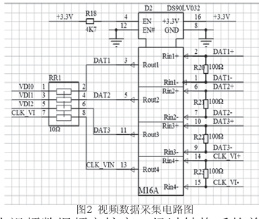

摄像头摄录的视频数据以LVDS差分电平信号进行传输,需求进行电平信号转化才干进行后续视频信号的记载处理。摄像头传输的视频数据包含4对LVDS差分信号,CLK+/CLK-是收集数据的时钟,其他3对差分信号包含着像素灰度。差分信号通过DS90LV032转化,变成4个单端的数字信号,供后边的电路处理。视频收集电路如图2所示。

由于视频数据频率较高,通过转化后的单端信号应该端接10 Ω的电阻以按捺反射,进步信号稳定性。

2.2 视频解码和处理

对前端收集的视频数据,有必要进行处理才干实时显现和紧缩存储。由于视频数据量大,为到达最流通的快速处理,应该由硬件逻辑直接进行数据处理。视频数据的解码和处理首要由FPGA完结,也是可编程逻辑规划的首要使命。

当时端DS90LV032将通过信号转化今后的视频数据传输给FPGA,由FPGA完结视频信号的解码复原、格局转化后同步传输给CPU模块进行实时记载和实时回放视频模块。FPGA视频数据处理的硬件接口规划如图3所示。

2.3 视频数据回放

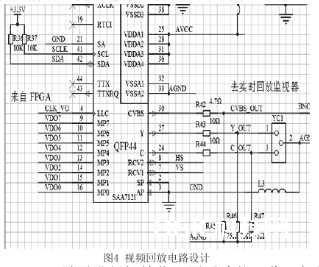

视频回放是便利飞翔员能够实时监控练习和实验的状况。体系选用Philips公司的SAA7121视频编码器,将FPGA处理后的视频数据转化为PAL制的归纳视频,送给飞翔员面前的监视器进行显现。如图4所示。

SAA7121需求进行初始化装备后才干作业,初始化通过设置编码器的寄存器,装备其作业方法。初始化要通过I2C总线完结,体系的I2C总线接口由FPGA完结。同步时钟CLK VO和8-bit并行视频数据都是由FPGA解码处理后传输过来的。编码器的作业频率为27MHz,FPGA解码后的视频数据通过SAA7121编码器的归纳视频信号CVBS送给监视器。一起也规划了一个备用的YC重量视频接口。

2.4 视频传输

收集的视频数据通过FPGA解码处理后需求通过PCIe总线传输给嵌入式CPU以便于实时紧缩存储。完结高速的PCIe总线是海量数据传输的要害。数据传输总线技能是不断更新开展的进程。在数据通讯的起先阶段,串行通讯由于信号简略、完结便利而运用广泛,占有操控位置,例如RS422串行通讯,虽然速率不高,现在依然很有生命力。为处理串行通讯的瓶颈问题,开端选用并行传输总线,并行通讯的速率取决于时钟频率和数据宽度。现在最盛行33MHz/32bit的PCI总线,峰值传输速率可达132Mbps。当持续进步时钟频率时,并行通讯总线的数据宽度却成为持续进步速率的妨碍。由于极高频下的线路串扰和反应,难以确保多路并行总线信号数据同步的一致性,数据通讯的传输技能从并行回归到串行,并行双向的PCI总线开展为串行单向的PCIe总线。速率高达2.5Gbps的PCIe总线有三对差分信号,即同步时钟CLK+/CLK-、接纳信号R+/R-和发送信号T+/T-。PCIe总线规划电路如图5所示。

在PCIe这种高速信号传输总线中,数据不是直接通过信号导线的电压信号,而是通过高频耦合方法传输的。图5中的C1、C2便是发送方的耦合电容,应尽量接近桥片。每一对差分信号都应该有耦合电容,图5中时钟和接纳信号对的耦合电容,隐含在PCIe的主控方。

3 、体系的逻辑规划

在硬件规划的根底上,逻辑规划成为整个体系功用完结的要害。逻辑规划完结整个体系的时序操控、视频数据流的收集与解码、视频回放的编码和PCIe桥接口的规划。

3.1 视频解码

在逻辑规划中,视频解码的功用是将DS90LV032所转化的单端信号解码后写入FIFO缓冲,由后续逻辑读取处理。其逻辑接口的VHDL方法描绘如下:

摄像头作为视频源,在每一个CLK的上升沿输出一个3-bit数据。与之相反,解码逻辑在CLK的下降沿锁存一个3-bit数据,进行流水线锁存,从头复原视频的灰度数据。对一个16-bit的数据,共需发6次。

3.2 视频编码

为支撑SAA7121编码器,视频回放逻辑包含为初始化而供给的I2C接口和PAL制的视频编码。SAA7121的寄存器是8-bit的,则其I2C接口能够描绘如下:

上层逻辑调用此模块,每调用一次,装备一个寄存器。一切128个寄存器的装备数据是预先定制的,寄存在常量数组中。

通过初始化后的SAA7121能够正常作业了。此刻逻辑应该不断运送视频数据。其逻辑接口能够描绘如下:

3.3 PCIe桥接口规划

数据高速传输首要体现在PCIe总线的实践吞吐量,此为解码后的数据传输的瓶颈。逻辑规划要特别考虑到软件的便利和高效。接口逻辑规划会集在中止逻辑和数据传输的burst方法上。

需求传输的视频数据,首要送入一个FIFO,写入端为32k×16bit,读出端为16k×32bit,写入时既合适了视频数据的宽度,读出传输时又发挥了PCI32-bit总线的优势,加快了转化。中止逻辑规划如下:

(1)当写入数据到达FIFO容量的1/4时,即写够4k×32bit时发生中止。这个条件可依据FIFO的可编程空判别,亦即PRG1 Empty=‘0’时发生中止。

(2)当主机呼应中止,开端读FIFO数据时吊销中止。

(3) 当本次burst读完毕后,才答应依据条件从头判别中止条件。

PCIe桥接口的逻辑规划最重要的部分是为它的部分总线(Local bus)供给无缝的粘合逻辑,支撑PCIe的单次拜访和burst拜访。其接口状况机如下:

桥片的部分总线规划了50MHz的时钟,对32-bit数据宽度,理论上能够到达200Mb/s的吞吐率。通过运用软件的实测,能够到达143Mb/s的速率,考虑到软件的许多开支,这个速率现已比较理想了。

4 、体系的软件规划

体系的软件规划渠道选用WindowsXP Embedded,软件分为针对本硬件体系的驱动程序和视频紧缩与处理的运用程序。运用程序把视频存为一般播映器能播映的视频格局,每帧视频为256行×256列共64K像素。在驱动软件中,当翻开设备时,请求一组缓冲,共128个缓冲。这个缓冲对运用程序是通明的,每个缓冲能够寄存一个完好的视频帧,如图6所示。驱动程序中有两个首要线程,中止线程和数据读出线程。

在逻辑设计时,每逢FIFO中写入4kx32bi时发生中止,则驱动程序的中止线程在呼应中止时,每次至少读16kB。在中止呼应读取FIFO数据时,不要用类似于for(;;)的软件循环完结,这种战略在硬件时序上归于单次拜访,功率低下。只要DMA才干触发逻辑规划中的burst周期,最大极限运用硬件功用。在发动DMA时,必定要使能它的burst位操作长度固定为16kB。这样,每次中止呼应就变成了保护DMA当时写入缓冲的指针,填入当时写入缓冲地址,然后发动DMA。

在运用程序中,运用一个守时线程,通过驱动程序读取视频数据,然后通过紧缩,寄存成JPEG2000格局的视频文件。守时读取视频数据的算法需求进行优化,由于假如数据读出线程太慢,中止线程写入时或许掩盖未读走的缓冲,会形成存储视频呈现丢掉数据帧的现象,影响记载视频的连续性。

5 、完毕语

本文选用FPGA与嵌入式CPU大容量数据存储相结合的计划,在体系各个处理环节均充沛考虑到对视频数据收集记载实时性和可靠性的要求,规划了机载多通道实时视频数据收集记载体系。体系硬件规划简略,而且可一起收集多路视频数据。在某型数字化对立练习评价体系中的运用标明,本规划计划满意了预期的目标要求,处理了载机使命体系多路视频数据收集与实时记载的要害问题,在实时视频信息收集和数据记载运用中具有较好的通用性和扩展性。

责任编辑:gt