0 引 言

在现代通讯和雷达领域中,宽带、高增益、实时并行处理是现代接纳机的重要标志。因而,这种具有高速并行处理才能和特有的大带宽功用的声光处理体系具有巨大的潜在优势。以声光器材为根底的接纳机除了具有宽带、高增益、实时并行处理等特色外,还具有容量大,体积小,功耗低一级长处。因而,选用声光信号处理技能处理带宽、高增益和实时并行处理问题具有重要意义,声光信号的收集体系的规划是整个声光体系要害之一。这儿规划了一个依据FPGA和USB 2.0的高速CCD声光信号收集体系,为声光信号收集供给了硬件渠道。

1 体系概述

声光信号收集体系框图如图1所示。体系首要由CCD声光信号收集模块、A/D转化模块、FPGA驱动和操控模块及USB接口传输模块四部分组成。

体系上电后,USB设备依照上位机的指令完结对。FPGA数据收集参数的初始化设置及收集操控。RL2048P在驱动时序的严格操控下作业,收集的模仿信号经专用CCD信号处理芯片AD9822的相关双采样及模/数转化后,缓存在EP2C35内部装备的FIFO中,然后判别当FIFO中的数据抵达2 048 B时,向USB操控器CY7C68013A中异步写数据,因为USB设置主动IN形式,能够直接把FIFO中数据传输到PC上位机硬盘文件中,因而可完结CCD声光信号的收集、传输及存储。

2 体系各模块规划

体系各模块规划为:

FPGA驱动及操控模块 体系选用Altera公司的CycloneⅡ系列。EP2C35F672C6芯片,具有高性价比及丰厚的逻辑资源,可满意体系的要求。有4个PLL,33 216个LE,48 KB存储器资源,能够装备成各种形式的ROM,RAM及。FIFO,35个18×18的专用乘法器。FPGA的首要功用是发生RL2048P驱动时序,操控AD9822采样及对其寄存器完结串行编程,内部装备FIFO缓存数据以及与USB接口通讯,并传输数据到上位机中。

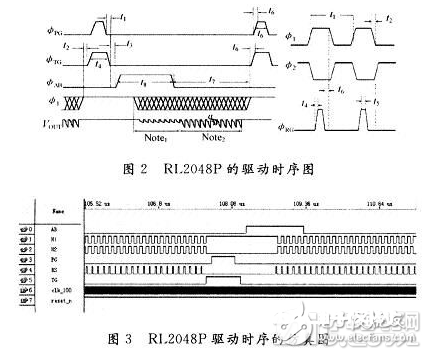

CCD声光信号收集模块 选用PerkinElmer公司的RL2048P线阵CCD。该芯片首要用于高速信号收集,2 048个有用像元,具有高灵敏度、大动态规模、宽光谱规模等特色,最高作业频率为40 MHz,该体系规划为10 MHz。EP2C35的时序驱动输出是3.3 V的LVTTL电平,不能直接驱动RL2048P(多电平要求)。因而,运用DG642和74FCT16244TV芯片完结电平转化,增强驱动才能。图2为RL2048P驱动时序图;图3为运用Verilog HDL编写驱动时序的QuartusⅡ仿真。由比较可见,规划完全能满意时序的严格要求。

A/D转化模块 AD9822是ADI公司的专用CCD信号处理芯片,内部集成CDS,PGA,14位ADC、暗电平主动校准、偏置电压操控以及串行接口等功用,采样速度高达15 MHz。ADCCLK的下降沿输出数据的高8位,ADCCLK的上升沿输出数据的低6位。AD9822采样操控时序及寄存器编程都是由EP2C35完结,与RL2048P输出信号同步,确保收集数据的正确性。选用相关双采样形式能够按捺CCD的复位噪声,本体系设置其寄存器分别为0x0058,0x10C0,0x2000,0x50FF。

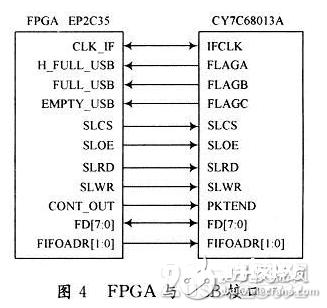

USB接口传输模块 USB 2.0协议的传输速度高达480 Mb/s,且具有接口简略及误码率低一级长处,能够满意该体系高速传输的需求。选用Cypress公司的新一代低功耗CY7C68013A芯片,与之相应的开发包和开发文档较完全,缩短了开发周期,降低了开发难度。为了确保数据传输的速度,CY7C68013A作业于SlaveFIFO形式,不需求EZ-USB FX2LP的CPU干涉,即可完结与FPGA的数据传输。EP2C35与CY7C68013A的通讯选用了Slave FIFO形式下的异步方法,向大端点EP6写数据,装备其为512 B四重缓冲区,批量AUTO IN传输形式,每次主动提交512 B数据。图4为EP2C35与CY7C68013A的接口衔接。

3 体系软件规划

体系软件规划包含:

固件程序(Firmware)规划 设备固件的首要功用是操控CY7C68013A接纳并处理USB驱动程序的恳求。如恳求设备描绘符,恳求或设置设备状况,恳求或设置设备接口等USB 2.0规范恳求;辅佐硬件完结设备的从头枚举、端点装备、操控和监测USB的活动,依据PC主机的指令与外围电路进行数据交换等。Cy-press公司为用户供给了一个固件程序结构,是通用性强的模块化程序。在结构的根底上,用户只需求编写Function.c文件即可完结USB功用开发。首要包含:Slave FIFO形式的初始化和用户自定义恳求。

驱动程序开发 体系包含两个USB驱动程序:一个驱动专用于下载芯片的固件程序CCDloader.sys,另一个通用驱动程序ccdusb.sys用来完结USB设备与应用程序的通讯和操控。芯片固件程序在主机上,当体系上电时,前者将其下载到芯片的RAM中,并由增强型8051微处理器履行。当固件下载完结后,模仿一次断开从头衔接,此刻下载的固件呼应USB枚举,并加载USB设备通用驱动程序。USB的驱动程序是WDM类型,能够运用Windows DDK,WinDriver,DriverStudio开发。

应用程序开发 它的首要任务是与USB驱动程序通讯,操控声光信号收集进程。在此用Visual C++6.0进行程序规划。CyAPI操控函数类为FX2LP系列USB接口芯片供给了非常精密的操控接口,只需在应用程序中加头文件CyAPI.h和库文件CyAPI.lib即可调用相应的操控函数,翻开USB设备读取数据并存储到主机硬盘中的CcdData.txt文件。

4 试验数据剖析

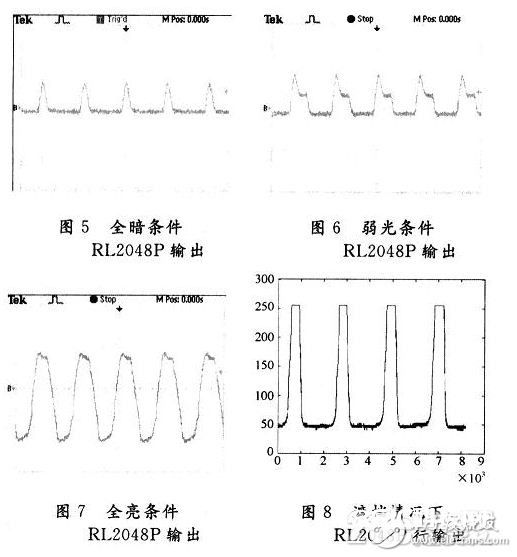

运用TEKTRONIX公司的示波器,对经过隔直处理后的RL2048P输出信号在各种试验条件下进行了测验和剖析。如图2所示,VOUT为像元输出信号,每一个像元输出信号的开端都有一个同步参阅信号,后边部分才为有用信号输出,因为CCD输出信号为负极性信号,所以有用信号值相对于参阅信号为负。

图5为全暗条件RL2048P的输出,因为光敏面上没有光,只要暗电平信号输出,所以像元的输出有用信号简直为零。图6为弱光条件RL2048P的输出,有用信号幅值发生了改变。图7为全亮条件RL2048P的输出,有用信号抵达了饱满值。RL2048P的实践输出和理论剖析共同,作业正常。声光信号经过中心有孔的不透光遮挡板照在CCD上,运用应用软件进行数据收集。从CCD Data.txt数据文件中接连提取8 192个像元点即四帧CCD数据,Matlab软件剖析如图8所示。

有光照耀的方位对应为高,实测数据和理论值符合。在其他条件下也做相关试验,结果与理论根本共同。因为篇幅所限,本文不做具体介绍。试验结果表明,体系功用完好,能够完结声光信号的高速收集、传输及贮存。

5 结 语

体系选用现场FPGA作为硬件规划中心,运用Veritog言语。进行硬件描绘,使体系更灵敏,可在线编程,便于扩展和晋级。这儿的CCD驱动时序选用状况机与分频相结合的新方法,实践测验驱动波形安稳且没有毛刺,CCD输出信号质量高。USB应用于Slave FIFO高速传输形式,满意了高速CCD声光信号收集的要求,具有实时性、高速、安稳、牢靠等特色。