在未来的节点上总有一些意想不到的行为,咱们对怎么处理它们还不是十分清楚。

例如在最先进的节点上变得越来越显着的是量子效应,导致电子器材和信号行为反常和意想不到的改动。

关于大多数芯片职业来说,量子效应通常是发生在暗地,由代工厂依据数据开宣布一套或许大多数公司从未见过的一套规划规矩,这就说明晰为什么代工厂和设备制作公司是迄今为止仅有遭到量子效应直接影响的公司,由于他们一向在调整他们的工艺和产品来把这些影响降到最低。可是跟着规划收缩到7/5nm或更先进的节点,量子效应正在成为一个越来越遍及和重要的问题,最终会影响到在这些节点作业的每一个人。

“由于缩放和相关的要求,一旦某些器材尺度变得十分小,器材中就会发生量子效应,”IMEC的技能解决方案和支撑总监Anda Mocuta说,“例如,作为栅极介电缩放和器材内电场增大的成果,回转层中的载流子不再坐落二氧化硅-硅界面,而是在下面某处,然后添加了有用介电层厚度。这种效应在CMOS技能中现已存在一段时间了,它是一种量子效应。展望未来,由于晶体管尺度减小,估计会有更多的量子效应发生,这对坚持静电并削减栅极长度是需求的。”

量子效应已被调查、研讨和提出多年了,它不仅仅是在半导体职业界。例如,量子隧穿在α粒子衰变研讨中现已被记录了近一个世纪。可是在芯片国际中,这些量子效应会出现在各种古怪的行为中,这些行为导致了各种问题横生。

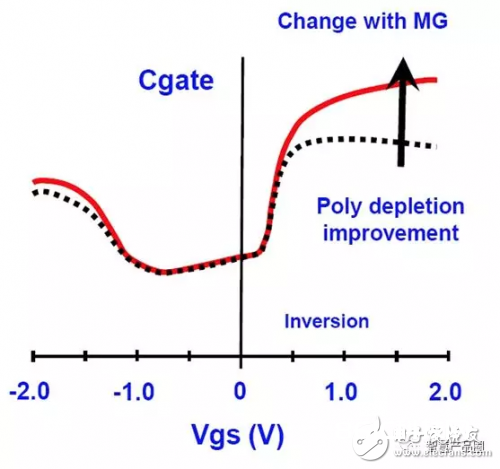

“量子效应一向存在,” 设在科文特的Lam Research部分核算产品副总裁David Fried说。“在不了解周期晶格和量子效应的情况下,不能真实求解晶体管方程。问题是它多少影响了你对器材的物理和电学行为的了解。假如回到10至15年,在咱们具有高k和金属栅极之前,咱们在栅极的一侧具有多晶硅耗尽效应,以及量子约束效应,其间载流子沟道不是坐落晶体管的界面处。由于晶体管沟道中的阶跃函数密度,它会稍远一点。离界面远一点的是量子效应,在130/90/65 nm时,它成为回转电容行为的可丈量δ。咱们进行了研讨和学习,并把它建成咱们的器材猜测模型。但是咱们都喜爱高K金属栅,金属栅消除了多晶硅的耗尽。咱们在沟道得到了更好的场耦合,并在技能上开端选用一些办法来削减这些量子效应。”

图1:多晶硅耗尽层上的金属栅改善和相关的电容及驱动电流改善

在7 / 5nm以及更先进节点的范围内,在与量子效应相关的列表中又增添了一组新的令人担忧的数据。

“你能够看到导线边际粗糙度的添加和改动,这给咱们带来了咱们不希望看到的开路或短路现象,”格芯的首席技能馆Gary Patton说。“这意味着你要尽或许地优化接地规矩,以使EUV的量产能够做到最大化。”

关于内存和其方向

闪存是芯片制作商开端体会量子效应的第一个当地。从几年前开端,NAND存储公司就报告了数据在内存中移动和流出有意外的违规行为。

“这便是闪存移动到笔直NAND的主要原因之一。”VLSI研讨的首席执行官G. Dan Hutcheson说。“问题是你不一定会得到你想要得到的东西。体系被规划成在一个随机的国际中作业,但当你进入量子国际,却不是依照你应该以为的那样办法作业,并且没有满足的电子数量来丈量究竟出了什么问题。”

有一些正在进行中的研讨,企图尽量削减经过薄层资料的电子隧穿。一种这样的办法叫自旋晶格,它能够部分化或“包括”杂散电子。自旋搬运扭矩(STT)MRAM运用的是电流而不是磁性来改动电子的自旋。

“多年来地道的问题在于它太慢,又太难施行。” Hutcheson说。“量子效应研讨的另一个方向是怎么使资料坚持满足的一致性,这样就不会发生这些问题。这也是一些大型设备公司一向在专心的。”

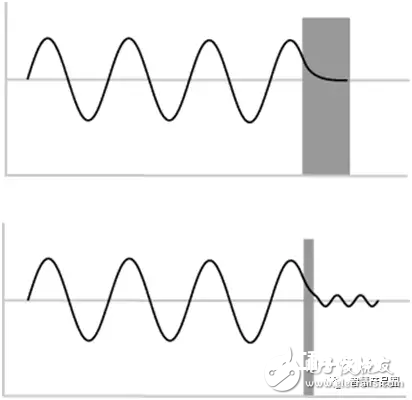

图2: 超薄势垒隧穿的电子波函数示意图

栅隧穿是引进高介电常数栅资料的一个要害原因。关于希望的等效氧化物厚度,它们添加的物理厚度削减了隧穿。但在高档节点是不或许的,由于栅极氧化层会与其他特征尺度一同缩放。