AD9267相关信息来自ADI官网,详细参数以官网发布为准,AD9267供给信息可在查IC网查找相关供给商。

产品概况

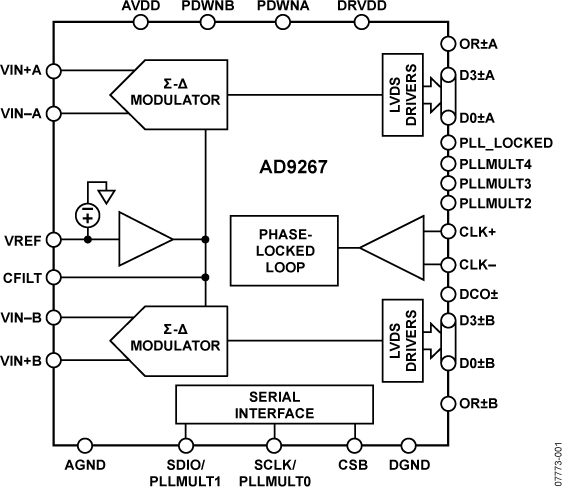

AD9267是一款双通道接连时刻(CT) Σ-Δ型调制器,在10 MHz实数或20 MHz复数带宽内可完成-88 dBc的动态规模。高动态规模、宽带宽和接连时刻Σ-Δ调制器架构所独有的特性使得AD9267成为无线通信体系的抱负解决方案。

AD9267具有阻性输入阻抗,可明显下降对驱动器放大器的要求。此外,32倍过采样五阶接连时刻环路滤波器可衰减带外信号和混叠,因此输入端无需外部滤波器。噪声系数低至15 dB,对前端信号链器材的线性要求得以下降。它还具有高动态规模,因此无需自动增益操控(AGC)环路。

选用一个差分输入时钟来操控一切内部转化周期。外部时钟输入或集成的整数N分频锁相环(PLL)供给过采样接连时刻Σ-Δ调制器所需的640 MHz内部时钟。数字输出数据以二进制补码格局经过4位LVDS以640 MSPS速率供给。一个数据时钟输出(DCO)用来保证接纳逻辑具有正确的锁存时序。为了消除带外噪声、下降采样速率,4位调制器输出端或许需求附加数字信号处理设备。

AD9267选用1.8 V电源供电,功耗为416 mW。AD9267选用64引脚LFCSP封装,额外温度规模为−40°C至+85°C工业温度规模。

产品聚集

- 接连时刻Σ-Δ架构可有用完成高动态规模和宽带宽。

- 无源输入结构可下降对驱动器放大器的要求,或许省去驱动器放大器。

- 32倍过采样比和高阶环路滤波器可供给超卓的混叠按捺功用,下降对立混叠滤波器的要求,或许省去抗混叠滤波器。

- 选用1.8 V单电源供电。

- 规范串行端口接口(SPI)支撑各种产品特性和功用。

- 引脚数少,配有高速LVDS接口和数据输出时钟。

使用

- 基带正交接纳机:CDMA2000、W-CDMA、多载波GSM/EDGE、802.16x、LTE

- 正交采样外表

优势和特色

|

|

AD9267电路图

AD9267中文PDF下载地址

AD9267下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/AD9267.pdf