LTC2273相关信息来自ADI官网,详细参数以官网发布为准,LTC2273供给信息可在查IC网查找相关供给商。

产品概况

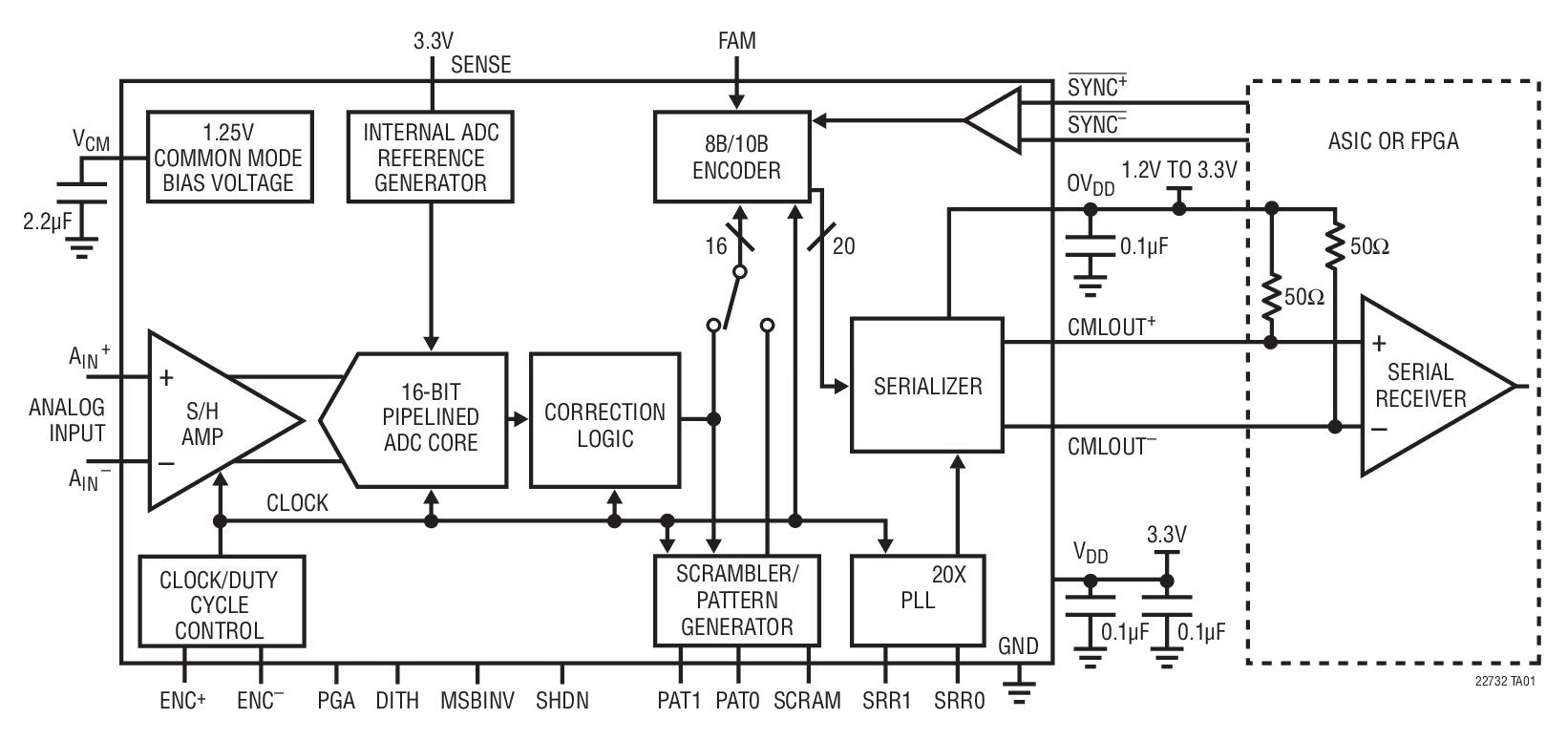

LTC®2273/LTC2272 是 80Msps/65Msps、16 位 A/D 转换器,具有一个高速串行接口。它们专为对具有一个 700MHz 输入带宽的高频、宽动态规模信号进行数字化处理而规划。该 ADC 的输入规模能够选用 PGA 前端进行优化。依据用于数据转换器的 JEDEC 串行接口标准 (JESD204) 对输出数据进行串行化处理。

LTC2273/LTC2272 十分适合于那些期望把灵敏的模仿电路与噪声数字逻辑电路阻隔开来的严苛使用。其 AC 功能包含 77.7dB 噪声层和 100dB 无寄生动态规模 (SFDR)。80fs RMS 的超低内部颤抖完成了高输入频率的欠采样和杰出的噪声功能。最大 DC 标准包含在整个温度规模内的 ±4.5LSB INL 和 ±1LSB DNL (无漏失码)。

能够使用一个正弦波、PECL、LVDS、TTL 或 CMOS 输入对编码时钟输入、ENC+ 和 ENC– 进行差分或单端驱动。一个时钟占空比稳定器在全速和各种时钟占空比条件下完成了高功能。

使用

- 电信

- 接收机

- 蜂窝基站

- 频谱剖析

- 成像体系

- ATE

优势和特色

- 高速串行接口 (JESD204)

- 采样速率:80Msps/65Msps

- 77.7dBFS 噪声层

- 100dB SFDR

- 在 140MHz 频率条件下的 SFDR > 90dB (1.5VP-P 输入规模)

- PGA 前端 (2.25VP-P 或 1.5VP-P 输入规模)

- 700MHz 满功率带宽 S/H (采样及坚持)

- 任选的内部高频颤抖

- 单 3.3V 电源

- 功耗:1100mW/990mW

- 时钟占空比稳定器

- 引脚兼容系列

- 105Msps:LTC2274

- 80Msps:LTC2273

- 65Msps:LTC2272

- 40 引脚 6mm x 6mm QFN 封装

LTC2273电路图

LTC2273中文PDF下载地址

LTC2273下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/22732fa.pdf