AD9550相关信息来自ADI官网,详细参数以官网发布为准,AD9550供给信息可在查IC网查找相关供给商。

产品概况

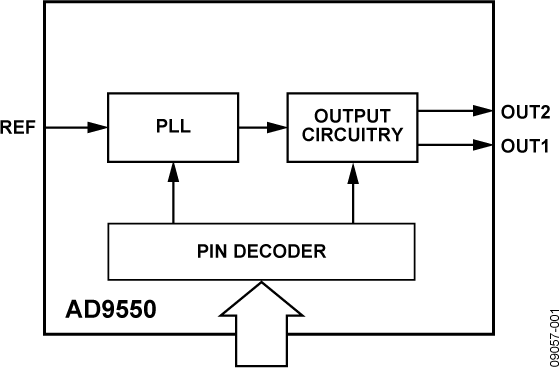

AD9550是一款根据锁相环(PLL)的时钟转化器,针对有线通讯和基站使用的需求而规划。它选用整数N分频PLL来满意相关的频率转化要求。REF输入端支撑单端输入参阅信号。

AD9550的引脚可编程,供给从15个或许的输入频率转化到51个或许的输出频率对(OUT1和OUT2)的规范输入/输出频率转化矩阵。

尽管AD9550严厉依照CMOS工艺制作,但其输出与LVPECL、LVDS或单端CMOS逻辑电平兼容。

AD9550的工作温度规模为−40°C至+85°C工业温度规模。

使用

- 高频VCXO、OCXO和SAW谐振器的高性价比代替产品

- 灵敏的频率转化支撑以太网、T1/E1、SONET/SDH、GPON、xDSL等有线使用

- 无线基础设施

- 测验与丈量(包含手持式设备)

优势和特色

- 将预设规范输入频率转化为规范输出频率

- 输入频率规模:8 kHz至200 MHz

- 输出频率最高可达810 MHz LVPECL和LVDS (200 MHz CMOS)

- 预设引脚可编程频率转化比

- 片内VCO

AD9550电路图

AD9550中文PDF下载地址

AD9550下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/AD9550.pdf

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/qianrushi/yingjian/42587.html