有许多同志在规划电路和制造PCB的过程中,对去耦电容的挑选仍是缺少知道乃至是存在很大的盲目性。这儿就触及的问题谈谈一二。

运用去耦电容滤除电路板上电源的高频噪声是工程中常用的办法。好的高频去耦电容电路可去除高达1GHz的高频成分。规划印制电路板的时,每个集成电路的电源和地之间都要加一个去耦电容。一般,瓷介电容和多层瓷介电容的高频特性较好。

去耦电容一般作如下作用:

1)、旁路掉器材的高频噪声(在电源和地之间为高频噪声供应低阻抗通路)。一般来说,作业频率越高,电容值越大,则电容的阻抗越小。

2)、作IC的储能电容,运用电容充放电原理供应和吸收该IC开门关门瞬间的充放电能。

在实践运用中,数字电路中典型的0.1uF去耦电容有5nH的散布电感,并行共振频率约为7MHz(只对此频率一下的噪声有较好的去耦作用)。而1uF、10uF的电容,平行共振频在20MHz以上,去除高频噪声的作用要好些。在电源进入印制板的当地放置一个1uF或10uF的高频去耦电容往往是有利的,即使是电池供电的体系也需求这种电容。

每10片左右的IC要加一片充放电电容(蓄放电容),巨细一般可选10uF。最好不必电解电容,由于电解电容是两层薄膜卷起来的,这种结构在高频是表明为电感,最好选用钽电容或聚碳酸酯电容。

去耦电容值的取法不严厉,一般可按公式C=1/f核算。关于微控制体系选0.1uF~0.01uF即可。一起在高频电路中要尽量运用贴片式的。趁便提一下,在实践运用傍边,并不是电容越大,对高速电路就越有利的,相反,小电容才干被运用于高频电路。原因触及到电容的寄生参数(如等效串联电阻、等效串联电感、走漏电阻、介质吸收电容、介质吸收电阻等)对滤波作用的影响问题。这儿作简略阐明一下:电容的谐振频率由其等效串联电感和容值C一起决议,这两者的改变都会影响电容的谐振频率。电容在谐振点邻近的阻抗是最低的,故规划时尽量挑选谐振频率和实践作业频率附近的电容为佳。若作业的频率改变规模很大,则可挑选一些谐振频率较低的大电容和谐振频率较高的小电容并用。

此外,在规划过程中挑选电容还得考虑电容的介电常数、绝缘性、温度特性、耐压等影响。在高速PCB板中对电容的处理可总结如下几点:

A.削减电容的引线或引脚的长度

B.尽量运用宽的连线

C.优先并尽量选用贴装的电容

D.电容要尽量接近器材的电源引脚并与之直接相连

E.电容之间别共用过孔

F.电容的过孔要尽量接近其焊盘(能打在焊盘上最佳)

简略而言便是要下降电感。

电源纹波发生的原因及去耦电容的选取

1.电源纹波发生的原因

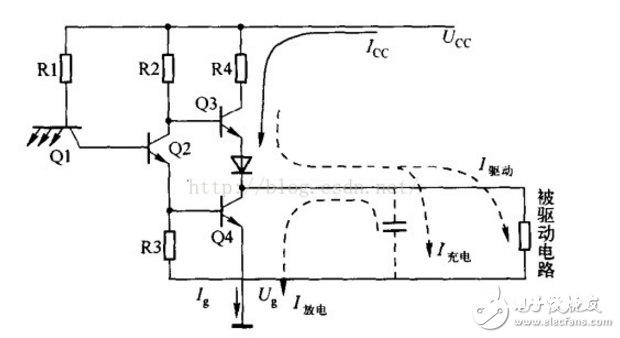

首要阐明一下芯片电源引脚发生纹波的原因。如下是一个典型的门电路输出级,当输出为高时,Q3导通,Q4截止;相反,当输出为低时,Q3截止,Q4导通,

这两种状况都在电源和地之间构成了高阻态,约束了电源的电流。

图1 典型门电路输出级

可是,当状况发生改变时,会有一段时间Q3 Q4一起导通,这时在电源与地之间构成时间短的低阻抗,发生30- 100mA的尖峰电流。当门输出有低变高时,电源不只

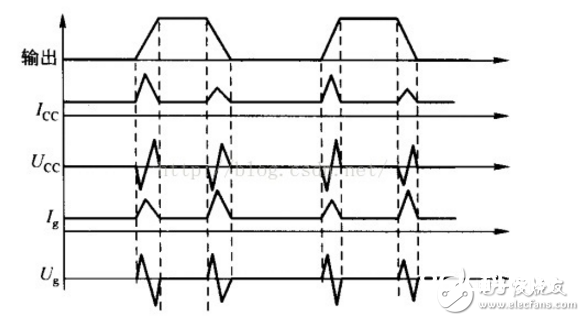

供应短路的电流,还要给寄生电容充电,使这个电流的峰值更大。由于电源线和地线总是有不同程度的电感,当电流骤变时,会在电源线和地线上发生压降,这便是电源线和地线上的噪声;特别关于周期信号,这样的噪声更显着,如下图。

图2 电源线和地线上的噪声

去耦电源是去除噪声的一种办法。当一切的信号脚作业于最大容量负载下一起开关时,去耦电容还供应给元件在时钟和数据改变期间正常作业所需的动态电压和电流。

去耦是经过在信号和电源平面之间供应一个低阻抗的电源来完成的。

2.电容的阻抗与谐振频率与去耦

1)电容去耦原理:电容在频率升高到谐振点之前,跟着频率升高,阻抗下降,这就给高频噪声供应了一个低阻抗的泄放途径,剩余的低频能量就不足以发射出去了。

2)常用电容: 0.1uF和0.01uF电容是当今高速电路中最常用的去耦电容。一般来说SMT的电容的自谐振点不会超越500MhZ,而0.01uF电容的自谐振点在50-150MhZ之间;并且在实践运用中引线电感及过孔的存在会进一步下降谐振点,这使得再小的电容,实践的去耦频率也不会超越300MhZ。

3)电容并联:相同容值的电容并联,引线电感和寄生电感会由于并联而减小,使得全体阻抗减小,这样有利于进步去耦频率,一起,电容并联也能供应更多的能量。

4)电源层与地层构成电容:在多层PCB中,依靠电源层和地层构成的板间电容,有着较低的ESL,这也是高频去耦的重要手法。

5)去耦电容的挑选:去耦电容不要什么都用0.1uF,要考虑去耦器材的作业频率和谐波。作业主频20Mhz以下的,用0.1uF,20M hz以上的用0.01uF,乃至更小的,并与0.1uF并联运用。(若增加磁珠,电容接近IC,磁珠远离IC)