p型mos管导通条件

靠在G极上加一个触发电压,使N极与D极导通。对N沟道G极电压为+极性。对P沟道的G极电压为-极性。场效应管的导通与截止由栅源电压来操控,关于增强型场效应管来说,N沟道的管子加正向电压即导通,P沟道的管子则加反向电压。一般2V~4V就可以了。

P沟道mos管作为开关,栅源的阀值为-0.4V,当栅源的电压差为-0.4V就会使DS导通,假设S为2.8V,G为1.8V,那么GS=-1V,mos管导通,D为2.8V。

假设S为2.8V,G为2.8V,VGSw,那么mos管不导通,D为0V,所以,假设2.8V连接到S,要mos管导通为体系供电,体系连接到D,运用G操控。和G相连的GPIO高电平要2.8-0.4=2.4V以上,才能使mos管关断,低电平使mos管导通。

假设操控G的GPIO的电压区域为1.8V,那么GPIO高电平的时分为1.8V,GS为1.8-2.8=-1V,mos管导通,不可以关断。

GPIO为低电平的时分,假设0.1V,那么GS为0.1-2.8=-2.7V,mos管导通。这种状况下GPIO就不可以操控mos管的导通和封闭。

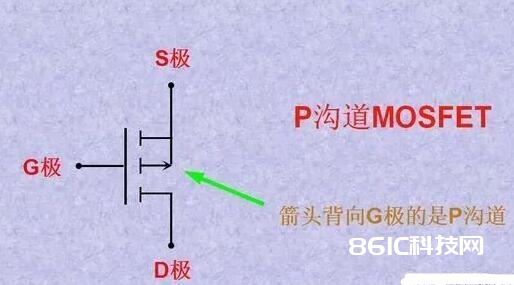

mos管的p沟道

p沟道mos管是指n型衬管底、p沟道,靠空穴的活动运送电流的MOS管。

P沟道MOS晶体管的空穴迁移率低,因而在MOS晶体管的几许尺度和作业电压绝对值持平的状况下,PMOS晶体管的跨导小于N沟道MOS晶体管。此外,P沟道MOS晶体管阈值电压的绝对值一般偏高,要求有较高的作业电压。它的供电电源的电压巨细和极性,与双极型晶体管——晶体管逻辑电路不兼容。PMOS因逻辑摆幅大,充电放电进程长,加之器材跨导小,所以作业速度更低,在NMOS电路(见N沟道金属—氧化物—半导体集成电路)出现之后,大都已为NMOS电路所替代。仅仅,因PMOS电路工艺简略,价格便宜,有些中规划和小规划数字操控电路仍选用PMOS电路技能。

p沟道mos管作业原理

正常作业时,P沟道增强型MOS管的衬底必需与源极相连,而漏心极的电压Vds应为负值,以确保两个P区与衬底之间的PN结均为反偏,一起为了在衬底顶外表左近构成导电沟道,栅极对源极的电压Vgs也应为负。

1、Vds≠O的状况导电沟道构成后,DS间加负向电压时,那么在源极与漏极之间将有漏极电流Id流转,并且Id随Vds而添加。

Id沿沟道发生的压降使沟道上各点与栅极间的电压不再持平,该电压削弱了栅极中负电荷电场的效果,使沟道从漏极到源极逐突变窄。当Vds增大到使Vgd=Vgs(TH),沟道在漏极左近出现预夹断。

2、Vds=0时,在栅源之间加负电压Vgs,由于绝缘层的存在,故没有电流,可是金属栅极被补充电而集合负电荷,N型半导体中的多子电子被负电荷排挤向体内运动,外表留下带正电的离子,构成耗尽层,跟着G、S间负电压的添加,耗尽层加宽。

当Vgs增大到必定值时,衬底中的空穴(少子)被栅极中的负电荷吸收到外表,在耗尽层和绝缘层之间构成一个P型薄层,称反型层。

这个反型层就构成漏源之间的导电沟道,这时的Vgs称为敞开电压Vgs(th),Vgs到Vgs(th)后再添加,衬底外表感应的空穴越多,反型层加宽,而耗尽层的宽度却不再改变,这样可以用Vgs的巨细操控导电沟道的宽度。

PMOS的Vgs小于必定的值就会导通,合适用于源极接VCC时的状况(高端驱动)。需求留意的是,Vgs指的是栅极G与源极S的电压,即栅极低于电源必定电压就导通,并非相关于地的电压。

可是由于PMOS导通内阻比较大,所以只适用低功率的状况。不过,大功率依然运用N沟道MOS管。

引荐阅览:

mos管怎样并联运用?

mos管小电流发热严峻怎样处理

n沟mos管导通条件