1 导言

GPS卫星导航接纳机有多种多样的类别,依据不同的分类办法,能够分为: C/A码与 P码,单频与双频,导航与定位,授时与丈量,手持、车载、机载、弹载与星载等。依据 GPS接纳机硬件架构完结的不同,又能够分为硬件接纳机和软件接纳机。GPS接纳机在设计时会依据不同的运用方针挑选不同的规划方案,GPS软件接纳机的处理方案具有可装备性,依据不同的使用环境装备不同的处理算法。本文对依据FPGA–DSP渠道的C/A码单频GPS软件接纳机的算法规划进行研究。

2 GPS软件接纳机

传统的GPS接纳机的核心部件一般包含天线与相关的前置扩大器,射频前端(模仿)部分,基带数字(ASIC)处理部分,微处理器及其外围(存储器与接口电路)。ASIC完结基带信号处理(捕获和盯梢的相关运算),微处理器从 ASIC输出的相关输出成果译出的导航数据,然后能够得到卫星星历及伪距,星历可用来得到卫星方位,并终究可由卫星方位及伪距解算出用户方位等信息。

软件 GPS接纳机如图 2.1所示,其构架主要是 GPS天线接纳到的卫星的发射信号,通过射频(RF)前端,输入信号被扩大及下变频到适宜的频率。然后经模数转换器数字化采样。天线、RF前端及 ADC均有硬件完结,信号被数字化后,一切的处理运算使命均由运转于通用数字信号处理渠道的软件来完结。

GPS软件接纳机的优势在于:软件接纳机整个数字部分均选用通用处理芯片,包含了较少的硬件,可编程性及灵活性均强于硬件接纳机,并且无需晋级硬件仅加载不同的算法软件即可完结 GPS接纳机的晋级或改型 3 软件 GPS算法与架构规划

3.1 规划思维

GPS接纳机有必要复现那颗将由接纳机捕获的卫星所发射的 PRN码,然后移动这个复现码的相位,直到与卫星的 PRN码发生相关停止。发射的 PRN码和复现码之间的相关进程与给定的 PRN码数学的自相关进程有着相同的特性。当复现码与接纳卫星码有相匹配时有最大的相关值,这是 GPS接纳机在盯梢或捕获卫星信号时在码相位域内检测卫星信号的方法。信号的捕获算法有多种,主要是依据 FFT算法改善得到,核算量较大。因为多普勒频移的存在,在实践捕获进程中需求多通道一起进行从不同的频移处开端核算相关。对相关成果进行判定,得到当时相关器的偏移,以操控码和载波数控振荡器。

GPS接纳体系中用于数字中频信号来完结盯梢及解调的典型的专用芯片 GP4020,其主要有 12通道的相关器和 ARM7微处理器内核构成,相关器由片上硬件单元组成,可满意快速并行的核算要求,相关成果通过微处理器编程操控,并依据相关成果装备相关器寄存器。

结合 CA码信号的捕获与盯梢的算法特性和 GP4020的特色,完结硬件向软件的转化,规划出契合 FPGA( Xilinx XC2V1000)和 DSP(TI TMS320C6416)的功用特色的,且信号的捕获、盯梢、解调彻底有由软件完结的 GPS软件接纳体系。

3.2 FPGA与DSP的功用区分

多路同步运算是 FPGA的优势,事情中止呼应以及与用户接口的合作更适合于 DSP。 FPGA以中止的方法向 DSP提交相关器运算成果,DSP为 FPGA供给码 NCO差错和载波辅佐。

所以在 FPGA中完结如下功用:

L1采样信号的载波剥离; CA码发生器;L1本地载波发生器( NCO);CA码发生器的 NCO ; CA码相关器;DSP中止信号的发生,向 DSP电路发送相关器相关成果。

在 DSP中完结如下功用:

CA码盯梢差错鉴别器; L1相位差错鉴别器; CA码盯梢环路滤波器;L1相位环路滤

波器;对 FPGA中码 NCO和载波 NCO的操控;宽带功率值和窄带功率值的提取;载波相位的提取;伪距的提取;输出信息的打包以及与用户接口通讯。

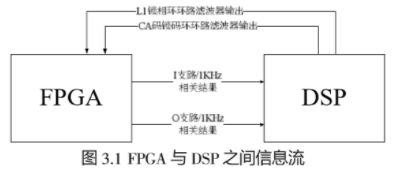

3.3 FPGA与DSP的之间的数据信息流

如图 3.1所示, GPS软件接纳机中内部信息流主要由运转于 FPGA上的可编程逻辑模块与运转于 DSP上的使用软件模块之间的信息流组成,包含:

1)FPGA向 DSP发送的 I/Q支路相关成果,用于完结载波盯梢与码盯梢。

2)DSP向 FPGA发送的环路滤波器输出值,用于操控 FPGA内部的载波 NCO与码 NCO。

图 3.1 FPGA与 DSP之间信息流

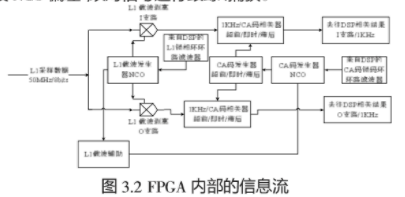

3.4 FPGA内的数据信息流

FPGA内部的信息流框图如图 3.2所示,L1采样数据以 50MHz/Byte的速率送往FPGA,FPGA通过载波剥聚散和码相关器核算,将相关器成果送往DSP,并从 DSP中获取 CA码和载波 NCO差错,以对信号进行盯梢、捕获。

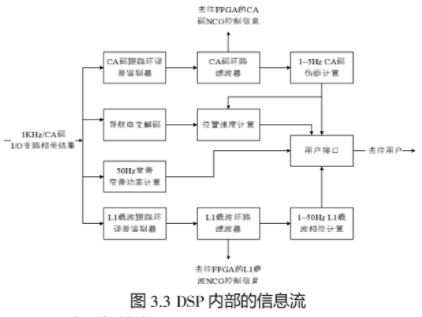

3.5 DSP内部的数据信息流

DSP内部的信息流和处理如图 3.3所示,1KHzCA码 I/Q支路相关成果来自于FPGA,DSP在内部通过 CA码盯梢环差错鉴别器和 L1载波盯梢环差错鉴别器后,去往FPGA,操控 FPGA中码 NCO和载波 NCO。

图3.3 DSP 内部的信息流

4 试验数据

图 4.1为体系在地上仿真时从用户接口输出的导航数据。

5 总结

本文作者立异点在于选用 FPGA-DSP渠道,规划出能够作业于高动态、弱信号的环境下单频 GPS接纳机软件。完结GPS的 C/A码伪距、L1载波相位、方位速度以及窄带功率的输出,为后续的使用供给根底。完结单频 GPS接纳机软件的工程化。尽管单频 GPS接纳机技能在理论上现已十分老练,但依据 FPGA-DSP渠道的功用优秀且满意工程化要求的 GPS接纳软件并不多见。

责任编辑:gt