一、 导言

在高速数据收集体系中,信号源作为一种校验设备,需求及时、有效地向收集设备供给高频信号,用于查验数据收集器的作业情况;一起信号源还应该可以供给一些必要的操控信号,用于对数据收集体系的操控。从这个意义上来说,信号源自身的作业应该更安稳、牢靠;另一方面,小型化、通用化信号源的规划和完结是信号收集体系的必定要求。因而,有必要选用先进的规划办法和大规模可编程逻辑器材加以完结才干习惯这种开展趋势,CPLD/FPGA等大规模可编程逻辑器材的开展和EDA技能的老练为此奠定了杰出的软硬件根底。

因为脉冲信号中既包括了丰厚的高频信号,又含有低频的成分,所以脉冲信号源可以用来检测收集设备在高频及低频下的作业状况。本文就侧重介绍了一种依据FPGA,选用VHDL硬件描绘言语规划完结的高速脉冲信号源,充沛体现了ASIC芯片在现代数字电路规划中的优越性。

二、信号源的方案规划

1. 功用介绍

该高速脉冲信号源电路首要是用于某类型数据收集体系的自检与测验,它可以模仿发生6路严厉同步的高速脉冲信号和3路操控信号,并为后续收集体系供给60MHz的时钟信号及备用电源。

2. 信号源原理框图

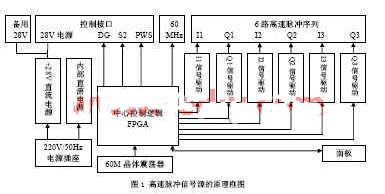

该体系由中心操控逻辑、电源模块、高速脉冲信号驱动模块及输出接口等部分组成。其间,中心操控逻辑担任操控信号以及高速脉冲的发生,从FPGA生成的高速脉冲经过信号驱动模块进行处理后输出;电源模块为信号源供电的一起,也为后续的收集体系供给备用电源。信号源的原理框图如图1所示。

高速脉冲信号源输入信号有60MHz晶振,以及来自面板上的操控信号,输出信号为3路操控信号,1路时钟信号,6路高速脉冲信号以及为后续高速数据收集体系供给的+28V直流电源。

面板上有三个操控开关,别离为复位开关RST, 方式挑选开关MODE1和MODE2。RST信号为外部的手动复位,当拨至低电平时,对体系一切的计数器清零;而两路方式挑选信号则担任输出的高速序列信号频率的切换,当MODE1为高且MODE2为低时,体系输出频率为1M的高速序列,当MODE1为低且MODE2高时,输出频率为10M的高速序列,当MODE1和MODE2同为高或同为低时,对体系进行复位。

三:FPGA内部逻辑的完结

VHDL言语是一种硬件描绘言语,首要用于描绘数字体系的结构、行为、功用和接口。除了含有许多具有硬件特征的句子外,VHDL的言语方式、描绘风格和句法与一般的计算机高档言语十分相似。运用VHDL言语规划硬件电路时,可以使规划者革除编写逻辑表达式或真值表的作业。这样使硬件电路规划的难度有了大幅度的下降,然后可以进步作业效率,缩短硬件电路的规划周期。

1、可编程器件的内部原理图

运用VHDL言语完结的信号源FPGA内部原理图如图2所示。

从图4中可以看出,FPGA在体系时钟(FOSC)和操控信号的驱动下,发生了6路高速序列及后续电路需求的导引头操控信号。别的,输入和输出的信号经过指示灯指示其作业状况,方便了设备作业状况的判别及调试。

2、高速脉冲的发生

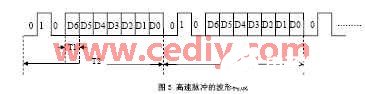

依据体系要求,要为后续的数据收集体系供给将6路不同特征但严厉同步的高频信号。在本规划中,高速脉冲的波形构成如图3所示。

在图3中,T1=100nS、T2=1000nS,数据次序输出,10个数为一组,每组的前3位为通道标志,即用来指示输出的波形是哪一通道,每通道的通道标识是仅有的。D6-D0组成7位二进制数,取值规模0-119,每2mS递加1,每2.4S循环一次。

详细的完结办法如下所示:

p1:process(RST,fosc)

begin

if (mode1=‘0’ and mode2=‘0’) or (mode1=‘1’ and mode2= ‘1’) or (RST = ‘0’) then j 《= “000000”;

elsif fosc ‘ event and fosc = ’1‘ then

case count1 is

when “0000” =》 j(0)《=’0‘;

when “0001” =》 j(0) 《=’1‘;

when “0010” =》 j(0) 《=’0‘;

when “0011” =》 j(0) 《= count(6);

…………………………

when “1001” =》 j(0) 《= count(0);

when others =》 j(0) 《= ’1‘;

end case;

end if;

end process p1;

I1 《= j(0);

在详细完结时,为了使6路高速脉冲信号差异开来,将别离担任计6路信号D0~D6部分的计数器初始值赋为:0,20,40,60,80,100。6路高速脉冲的输出波形图如图4所示。

由图4可以看出,经过改动向量j的值,并将它的每一位赋给高速序列的输出端口,可以发生6路严厉同步的高频序列。且因为各路在输出的过程中,有或许呈现多个周期的高电平或低电平,使得输出信号中不只包括了高频信号(信号的上升和下降沿),也包括了低频信号,可以全面检测数据收集器的高频和低频特性。

三、典型单元电路规划

1、 FPGA上电复位电路

为了完结FPGA的牢靠复位,在信号源规划中,咱们运用专用的芯片MAX708来发生复位信号。EPM10K10的装备引脚中,INIT-DONE状况引脚归于漏极开路输出类型,该引脚的功用为:用来指示该器材现已初始化完结而且处于用户状况。在装备期间,INIT-DONE输出为低,在装备完结后,该管脚变为高。当INIT-DONE管脚的电平发生跳变,即芯片MAX708的 输入端有上升沿到来时, 端输出持续时刻为200ms的复位脉冲。复位模块的原理图如图5所示:

相对于别离芯片,MAX708构成的复位电路大大地改进了体系的牢靠性和精确度。

2.高速脉冲信号输出驱动模块规划

从中心操控逻辑单元中输出的高速脉冲要经过差动滤波扩大电路后才干得到所需求的波形。在该差动滤波扩大电路中选用集成芯片AD9631作为扩大电路中的扩大器。高速运放AD9631小信号模型作业频率320MHz, 大信号模型175MHz;超低失真,低噪声;高速视频模仿信号的驱动电路的原理如图6所示。

差动扩大电路是高速信号源信号输出的首要电路部分。在规划中运用外部频率补偿法,可以下降环路增益,进步电路安稳性[3]。如图3所示,运算扩大器的两个输入端之间跨接一个电阻R14=100Ώ,此电路既可以是反相扩大器,也可以是同相扩大器,这取决于输入源接在正相输入端仍是反相输入端。R14的存在并不影响Aideal的巨细,仅仅增大了支流噪声增益发生直流输出差错。别的,在差动扩大电路中,与反应电阻并联接一个10PF的电容,该电容的作用是保持运算扩大器杰出的安稳性。在高速脉冲的输出接口上,本体系选用SMA连接器后接同轴电缆的办法来完结杰出的传输作用。

五:定论

用可编程逻辑器材规划完结的信号源不只具有电路简略、体积小等杰出长处,还便于规划的修正和优化,大大缩短了产品的开发规划周期;一起经过相应的EDA东西进行充沛的功用仿真和时序仿真,可以将规划的缺点尽量消除在规划的前期,进一步进步产品的牢靠性。经上述规划的高速脉冲信号源已成功应用于某类型高速数据收集体系的自检与调试,可以输出安稳、牢靠的高速脉冲信号、时钟信号及收集体系所需的操控信号。

文章立异点:本文规划的依据FPGA的高速脉冲信号源能发生6路严厉同步的、包括时刻及通道编码信息的高速脉冲,可用于检测数据收集体系的高频及低频特性。

责任编辑:gt