1、导言

传统的测控网是将具有各种功用的仪器经过比如VXI、CAN等专用总线衔接起来构成一套完好的测控体系。现在看来,传统的测控网首要具有四个方面的缺乏:一、数据传输速率有限;二、传输间隔有限;三、设备数量有限;四、本钱昂扬。传统的测控网现已很难满意人们对大数据量,远间隔和低本钱的要求。跟着Internet技能的开展和遍及,经过将仪器接入Internet,仪器将丈量的数据封装成IP包的方法进行传输,不只可以处理传统测控网的缺乏,并且可以同享网络技能开展带来的便当,跨过地域的约束,完成丈量数据的同享。本文首要评论多路千兆以太网信号中IP数据收发的规划与完成,具体介绍了MAC接纳操控器的规划,为仪器接入网络,组成高速的网络化测控体系供给了一种经济高效的测验数据传输手法。

2、体系功用及介绍

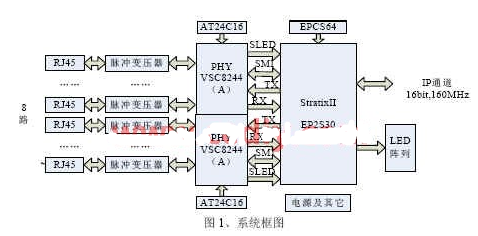

体系框图如图1所示:

本体系首要选用Altera公司的StratixII系列FPGA芯片EP2S30为主处理芯片,经过Vitesse公司的PHY芯片VSC8224及相关的外围电路组成,完成了8路千兆以太网电信号中IP数据收发的功用。VSC8224首要完成物理层上的比特流和链路层上的数据彼此转化。IP数据接纳和输出部分由EP2S30经过VHDL程序来完成。EP2S30在整个体系中起着核心作用,它将2片VSC8224送来的数据进行重组,将MAC帧中的IP数据提取出来,保存在缓冲存储器中,最终将8路数据顺次从IP通道输出给别的的设备,一起EP2S30也接纳其它设备送来的IP数据,然后封装成MAC帧经过VSC8224发送到以太网上。EP2S30也操控LED阵列来指示当时各个网口的衔接情况及体系作业情况。

3、体系硬件规划

EP2S30是Altera公司推出的StraTIxII系列FPGA中的一款,它具有十分丰富的I/O资源,支撑多种电平标准,它内部资源丰富,可以完成杂乱的运用,特别是它内部集成了M512/M4K/MRAM三种片上RAM,并且数量很多,可以将它们装备成单口/双口/FIFO等多种存储器,特别合适大数据量的存储转发。

VSC8224是Vitesse公司推出的具有4个口的低功耗、支撑10/100/1000BASE-T和1000BASE-X的高性能以太网PHY芯片。VSC8224支撑最新的RGMII V2.0标准,这为PCB板规划供给了极大的便当,无须考虑十分严厉的延时要求。图1中2片VSC8224与FPGA之间的衔接便是选用的RGMII接口的方法。VSC8224有3种装备方法可供挑选,这儿运用EEPROM(AT24C16)对它进行装备,先将装备内容经过编程器固化到EEPROM中,VSC8224在上电或许复位之后主动从EEPROM中读取出装备数据来自己进行装备。FPGA经过2线的SMI串行办理接口对VSC8224内部的情况寄存器进行拜访,读出VSC8224的作业情况,以确认进一步的操作。FPGA经过VSC8244的2线的串行LED情况输出口来读出4个端口的情况,然后经过驱动器驱动发光二极管发光,这为规划供给了极大的灵活性,可以操控发光二极管显现多种情况。

4、 MAC操控器的VHDL完成

本体系选用VHDL完成MAC操控器和IP数据的接纳与输出。MAC帧的格局如图2所示:

从MAC帧格局,可以看出,在接纳的进程中只需咱们找到了先导码和分界符后就可以依据MAC帧格局得到整个MAC帧,然后依据长度/类型来判别此MAC帧的内容,然后取得MAC帧中的IP数据。发送IP数据的进程是接纳IP数据的逆进程,只需依照MAC帧的格局将IP数据封装在一个MAC帧中,再经过PHY芯片顺次发送出去就能完成IP数据的传输。

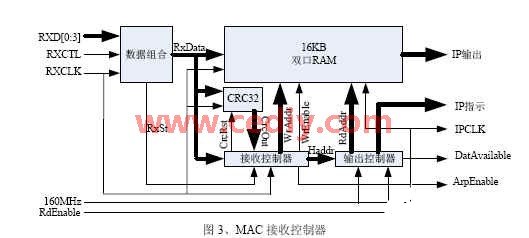

FPGA首要完成MAC帧的收发、MAC帧的拼装和分化、IP数据的收发功用,使用VHDL模块化规划的长处,只需完成1路的功用,别的7路就能很简单完成了。本文首要介绍MAC接纳操控器的规划,这儿使用VHDL规划如图3所示的MAC接纳操控器。

如图3所示,依据RGMII接口标准,RXCLK为VSC8224从接纳数据中提取的125MHz接纳时钟,RXD[3:0]和RXCTL在RXCLK的上下沿都有用,RxSt为RXCTL在RXCLK上下沿的与,RXD数据相当于一个4bit×125MHz的DDR信号,为了便于后期处理,将数据组组成一个8bit×125MHz的信号。这一部分由图3中的数据组合模块组成。

为了完成MAC巨帧的处理,充分使用FPGA资源,完成异步数据的同步输出,为每一路千兆以太网都生成了一个16K字节的双口RAM作为缓冲器,双口RAM的输入是8比特,输出为16比特的数据,一起输入时钟是各路提取的125MHz的时钟,输出为同源时钟产生的160MHz时钟,这样可以完成了异步信号的同步输出。

IP数据的提取和存储由接纳操控器来完成,IP数据的输出由输出操控器来完成。下面就别离介绍这两种操控器。

4.1 接纳操控器

接纳操控器首要是由一个写地址操控器和一个有限情况机组成。

写地址操控器首要操控3个信号,一个是14bit的写地址寄存器WrAddr,一个是14bit的写开端地址寄存器Haddr和一个写使能WrEnable信号。在每次写一帧数据之前都将写开端地址寄存器的值赋给写地址寄存器。在每帧数据CRC校验正确之后,修正Haddr的值为当时WrAddr的值加1,假如CRC校验有误则不修正Haddr的值,则下一帧从本来的地址开端,覆盖上一帧接纳过错的数据。由于双口RAM的输入是8bit,输出为16bit,并且IP数据总长度或许为奇数也或许为偶数,为了便于后边的数据输出,Haddr的值一向应该为偶数,当CRC校验无误后,假如IP数据包的长度为奇数,应将Haddr主动加上1变为偶数,作为下一次写地址的开端地址。WrAddr在到达0x3FFF之后主动回到0x0000持续递加。

依据MAC帧格局,接纳情况机别离设置了9个情况:idle, preamble, sfd, destaddr, souaddr, typ_len, payload, padding, fcs。当RxSt为0时,接纳情况机一向处于idle情况。当RxSt为1时,接纳情况机开端监督RxData上的数据,假如为0x55,则由idle态进入preamble态,假如满意7个接连的0x55,则进入sfd情况,不然回来idle情况。在sfd情况下,假如此刻RxData上的数据为0xD5,则进入下一个情况,不然回来到idle情况。在destaddr和souaddr情况下,接纳操控器可以取得意图MAC地址和源MAC地址。在typ_len情况下,接纳操控器可以取得该MAC帧的类型或长度,由于该体系首要是处理IP数据,所以只关怀类型为0x0800的IP数据和类型为0x0806的Arp恳求帧。假如接纳的类型不是0x0800或0x0806则抛弃这次接纳,回来到idle情况。假如为Arp恳求帧,在接纳完后帧校验无误则使能ArpEnable信号,使能Arp应对模块发送Arp应对帧。假如为IP数据包帧,在payload情况下,假如destaddr情况取得的意图MAC地址与本身的MAC地址共同则持续进行接纳,不然抛弃这次接纳。在数据接纳完之后,假如总长度大于46字节,则进入fcs情况,以取得帧校验成果;假如长度小于46字节,则还要进入padding情况,之后才干进入fcs情况。在fcs情况之后,将取得的帧校验成果和CRC32模块核算取得的成果进行比较,以确保传输的正确性。

4.2 输出操控器

与接纳操控器相同,输出操控器也是由一个读地址操控器和一个有限情况机组成。

读地址操控器有一个13bit的读地址信号RdAddr,这个读地址信号与写操控器输出的写开端地址信号Haddr的高13bit进行比较,假如持平则标明当时双口RAM中无新的IP数据,假如不持平则标明RAM中至少有一帧新的数据。此刻输出一个DatAvailable信号给顶层模块,顶层模块依据各路情况,输出一个RdEnable信号给基层模块,基层模块将RdAddr信号递加以读出RAM中的数据,当到达0x1FFF时主动回到0x0000进行递加。

由于保存在RAM中的数据包含MAC帧的意图地址、源地址、类型/长度和数据部分,所以输出情况机设置了5个情况:Ridle,Rdestaddr,Rsouaddr,Rtyp_len,Rdat。在RdEnable信号无效时,情况机一向处于Ridle情况,当RdEnable信号有用时,由Ridle情况顺次进入Rdestaddr、Rsouaddr和Rtyp_len情况。IPvalid用于指示IP数据有用,IPhead指示IP包的榜首个字节,IPtail指示IP包的最终一个字节,HalfB用于指示在IP数据包为奇数时,IP包输出的最终一个16bit数据的高8bit为有用的IP数据。IPCLK为160MHz的时钟,是由外部输入的50MHz时钟经过FPGA内部的锁相环得到。

4.3 顶层模块规划

顶层模块首要是和谐与操控8路模块的作业。顶层模块顺次对每一路进行轮询,由于基层模块的RAM中一旦有新的IP数据就会输出一个DatAvailable信号,从榜首路到第8路顺次查询各路的DatAvailable信号,假如有用则输出一个RdEnable信号给该模块,读出一帧IP数据包。当一帧IP数据包输出后持续进行下一路的查询,而不论这一路是否还有新的IP数据没有读出,假如还有数据没有读出,在下次轮询的时分再读出,这样将减小由于某一路一向占用IP数据输出通道而其他路无法输出IP数据而产生双口RAM溢出的或许。

5 、定论

本文所规划的千兆以太网IP数据传输设备经过在现场的调试,运转杰出,情况安稳,误码率低,并且支撑IP数据包长达8K字节的巨帧,提高了网络使用率,到达了高速测控数据传输的要求。该体系的研制为仪器接入网络,使用网络来收发测验数据成为或许,为网络化仪器和网络化测控体系的开展供给了经济可行的高速数据传输手法。

本文作者立异点:使用FPGA片上RAM为每一路千兆以太网规划了一个数据缓冲器及一个MAC接纳操控器,处理了多路IP数据收发和异步数据同步输出的问题。

责任编辑:gt