跟着集成电路设计师将更杂乱的功用嵌入更狭小的空间,异构集成包含器材的3D堆叠已成为混合与衔接各种功用技能的一种更为有用且经济的办法。作为异构集成渠道之一,高密度扇出型晶圆级封装技能正取得越来越多的认可。此种封装处理方案的首要优势在于其封装的基片更少,热阻更低,电气功能也更优异。这是一个表现“逾越摩尔定律”的比如,即运用 “摩尔定律”以外的技能也能完结更高的集成度和经济效益。

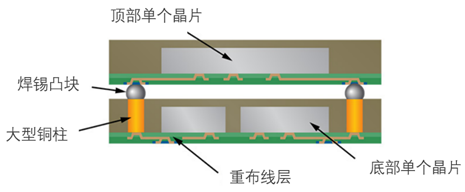

图1. 2.5D封装中的中介层结构

异构集成技能

高密度扇出型封装技能满意了移动手机封装的外形尺度与功能要求,因而取得了技能界的广泛重视。构成此技能的要害元素包含重布线层(RDL)金属与大型铜柱镀层。重布线层连通了硅芯片上的高密度衔接和印制电路板的低密度衔接。一般需求运用多层重布线层,才能够让信号路由至电路板。

如图1所示,大型铜柱是笔直衔接不同层级的金属支柱。顶部单个晶片的焊锡凸块被放置于大型铜柱之上,并经过回流焊完结衔接。

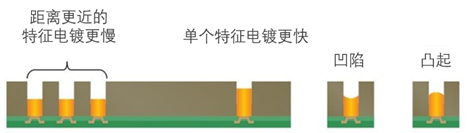

图2. 电镀大型铜柱的常见差异包含电流负载问题、洼陷和凸起

大型铜柱的工艺应战

大型铜柱的差异在于其尺度巨细:它的高度和宽度是规范铜柱的5倍之多。构建大型铜柱的传统办法是选用惯例电镀,这个进程绵长且缓慢。而最大的问题在于,此进程一般会发生不行承受的不一致成果。电镀铜柱的高度会随部分电流负载密度的不同而改变,并或许在支柱顶部发生必定程度的拱起或洼陷,而不是所需的平坦外表(图2)。这种高度与特征形状的不一致,或许会需求额定的后续平面化过程(如CMP),并会导致衔接不稳定,下降设备功能,增加整体工艺时刻和本钱。

影响以上电镀成果的单个晶片布局差异包含特征形状、宽度、深宽比以及周围光阻的厚度和给定区域的特征密度。这些差异或许会演化成为晶圆、单个晶片或各个特征之间的差异。

处理这个问题的办法之一就是在方针厚度上电镀剩余的金属,然后反转电镀极化与电流方向。这将回蚀所增加金属,以缩小铜柱的高度散布,或使大型铜柱的顶部更平坦。但这种办法或许无法有用提高不同长度铜柱尺度的一致性,并且一般会导致不良变形,使得大型铜柱的外表粗糙洼陷,边际腐蚀。

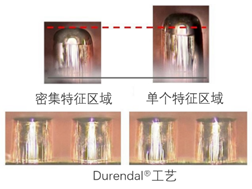

图3. 经过SABRE® 3D运用Durendal®工艺,产出尺度均匀、高质量的大型铜柱。下方的图片比较了晶圆边际(左边)与晶圆中心(右侧)大型铜柱的高度差异

泛林集团的处理方案

泛林集团经过其独有的Durendal®工艺处理这一问题。该工艺能够产出优质、润滑的大型铜柱顶部外表,整个晶圆上的大型铜柱高度也十分均匀。整套Durendal®工艺能够在SABRE® 3D设备上施行完结。

Durendal®工艺供给了一种经济高效的办法进行单个晶片堆叠,并能产出高良率以及安定牢靠的衔接。在未来,咱们等待Durendal®工艺能促进扇出型晶圆级封装在单个晶片堆叠中得到更广泛的使用。