工业以太网是指运用根据以太网的协议完结工业主动化和产品机械操控中实时牢靠的通讯,在车间底层操控器之间、车间之间,以及车间和办公室之间经过互联网完结通用渠道。因为这些协议在以太网物理层,即第1层上完结根据相同的IEEE 802.3规范,因而可以运用一个根据FPGA的渠道来支撑不同的工业以太网协议,不管这些协议有怎样的实时特点和完结办法。

关于速度和实时功用要求十分高的协议,在硬件中以专用协议MAC的办法完结实时功用。而协议的其他功用由运转在嵌入式处理器中的软件仓库来完结,这些处理器可以是在 Cyclone III FPGA中完结的Nios II软核处理器。

工业以太网开展情况

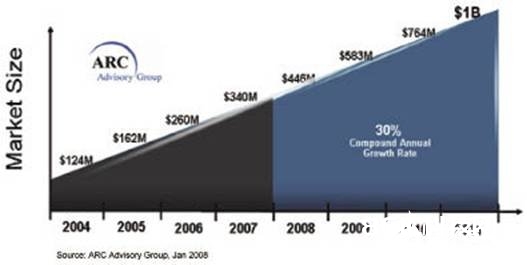

图1是来自ARC咨询集团的商场数据。ARC猜测在往后几年内,工业以太网商场会呈现微弱添加。其间,在2011年之前工业以太网器材和交换机出售添加年度复合添加率将到达30%。

图1 ARC咨询集团猜测:往后5年中以太网现场器材和交换机年度复合添加将到达30%

现在的工业通讯环境还不共同,有较多的竞赛工业以太网规范和传统的现场总线规范,许多解决方案选用了ASIC、ASSP和MCU来完结。这类硬件不是很灵敏,需求针对用户支撑的每一种协议改动硬件和相应的软件仓库。

现在,有几种敞开规范工业以太网协议,包含EtherCAT、Ethernet IP、Modbus/TCP、PROFINET、Ethernet POWERLINK和SERCOS III。这些协议都可以运用单一硬件规划在FPGA中完结,使工程师可以在一个支撑多种协议规范的硬件渠道上进行规范化处理。

跟着时刻的推移,越来越多的规范选用了根据FPGA的渠道。推进工业以太网在工厂主动化以及进程体系中运用的首要因素包含渠道的通用性和功用、办公室和工厂信息集成以同享实时信息、下降总本钱等。

工业以太网解决方案支撑通用渠道,然后推进了办公室和工厂集成,在底层操控器和车间办理之间树立链接,同享实时信息,完结敏捷呼应。一起还可以经过内联网衔接车间内部、车间之间以及车间和办公室之间的实时和非实时体系,与对应的现场总线协议后向兼容,支撑新体系和老体系之间的渠道操作。

敞开协议规范简化了设备施行和网络通讯,有助于工厂从多层现场总线过渡到单一的以太网,支撑各种商用设备和电缆,即便工业以太网协议呈现了改动,也可以重复运用这些设备和电缆。

经过定制网络,支撑多种拓扑,可以在网络中添加或许去掉器材,供给更多的操控功用,并且不会影响体系其他部分的作业,然后缩短了开发时刻。

工业以太网根据安稳、老练、牢靠的以太网技能,下降了施行、保护和总的体系本钱,然后完结了产品更敏捷地面市,不需求ASIC、ASSP和MCU规划贵重的专用解决方案,防止了硬件和软件改动导致的高本钱。

工业以太网体系结构

工业以太网协议可以分红三类体系结构(图2):A类、B类和C类协议规范。

A类运用规范以太网 TCP/IP,首要用于非实时信息层面的运用,例如工厂主动化、低速传感器和HMI显现等PLC运用。其典型的呼应时刻大约为100ms左右,或许更长。 EtherNet/IP、Modbus/TCP和PROFINET CBA是这一类中常见的以太网协议。

B类在规范以太网硬件之上运用定制软件仓库,供给恰当的实时功用,呼应时刻小于10ms。B类合适低精度电机操控和长途I/O通讯等运用,涉及到Ethernet Powerlink和PROFINET RT等协议。

C类在MAC层运用改善后的硬件,一起运用定制软件来完结确认的快速实时功用,一般小于1ms,适用于器材级的准确运动操控等运用。EtherCAT、PROFINET IRT和SERCOS III都是C类工业以太网协议的比如。C类体系结构的规范网络流量带宽小于A类体系结构。

为支撑悉数三类工业以太网体系结构,需求具有全面的可装备渠道才能,可以一起改动硬件和软件。

根据FPGA的以太网完结

传统上,微操控器、ASIC或许ASSP一向用于完结现场总线和工业以太网解决方案。这些产品具有很高的性价比,当功用、协议规范和I/O固定不变,或许没有硬件改动时,作业情况杰出。可是因为工业网络规范在不断改动,而工业运用要求产品生命周期十分长,通常在10年以上,此刻,这些产品便具有必定的局限性。每一个新的解决方案都需求对电路板进行重制,许多的软件编程人员将代码移植到新处理器和新渠道上,这是十分耗时的进程。

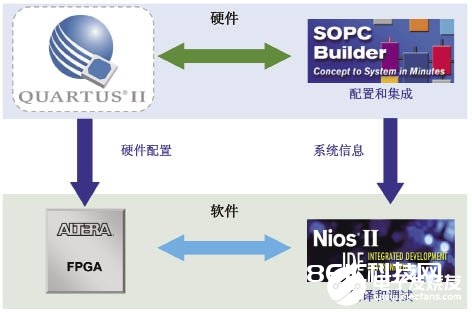

Altera Cyclone III系列等FPGA可以在同一渠道大将处理器功用和工业以太网协议与其他定制IP或许接口进行更新和集成。当工程师了解了Altera供给的 Quartus II和SOPC Builder等FPGA开发东西后,作业就会变得十分简略。

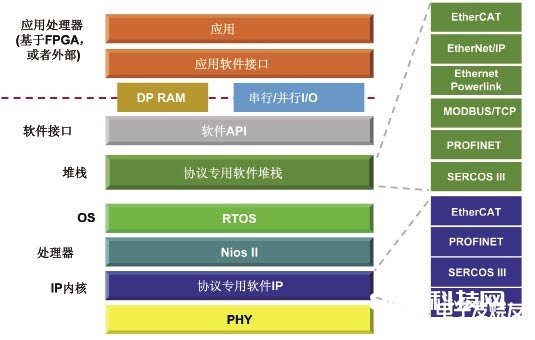

图3是支撑工业以太网的典型运用的体系结构。悉数工业以太网规范都根据IEEE 802.3以太网物理层。所以,在图3的下部,PHY和总是相同的。在规范以太网运用中,可以在PHY之上选用规范介质拜访操控器或许MAC,关于非实时工业协议,这便是其典型的完结办法。

图2 工业以太网分类

图3 支撑工业以太网的典型运用的体系结构

Ethernet IP、Modbus/TCP和Ethernet POWERLINK等协议运用了规范MAC,因而,可以只修正运转在Nios II处理器上的软件仓库,运用相同的以太网MAC IP来支撑这些协议。

关于EtherCAT、PROFINET IRT和SERCOS III等有实时要求的协议,规范MAC就不能满意要求了。在这种情况下,有必要运用专用协议MAC。关于选用了Cyclone III等FPGA的规划,可以运用支撑专用协议的MAC来代替规范MAC。某些协议还或许需求支撑IEEE 1588功用,或参加集线器或许交换机以进步功用,添加环形保护等其他功用。

正确的运用这些硬件就可以接纳任何工业以太网规范数据包。此刻,用户需求一个处理器来处理数据包、办理通讯功用。在FPGA中选用Nios II处理器内核等软核处理器很简略完结这些功用,在这类处理器上可以运转实时操作体系。

这种完结办法针对不同的仓库,为工程师供给了共同的软件渠道,在完结单芯片多规范解决方案时很简略对软件进行支撑和保护。现在,用户可以经过任何工业以太网协议来发送和接纳数据。

经过软件API笼统出以太网链接接口是完结运用程序数据流的最佳办法,这样,当改动工业以太网规范时,只需求很少的改动乃至不用改动就可以运转运用程序。在支撑多规范时,节省了许多的时刻和投入。软件API经过双端口RAM、串行I/O或许并行I/O进行通讯。运用软件可以运转在外部处理器或许FPGA内部的另一Nios处理器上。

FPGA硬件供给灵敏的渠道,任何时候都可以从头装备,支撑对产品特性进行当即更新。这意味着可以在同一 Cyclone III FPGA上完结规范或许定制工业以太网MAC、DSP模块以及其他定制逻辑和I/O接口,进步工业网络产品的功用和接口才能。

根据Altera FPGA的解决方案和硬件/软件规划东西可以规划并集成工程师所需求的悉数功用。嵌入在FPGA中的Nios II软核处理器可以用于运转以太网仓库驱动软件和其他功用。乃至还可以参加第二个处理器,以支撑运用层软件。并且,Ethernet IP和SERCOS III等工业以太网协议仅以IP的办法发布,答应运用FPGA来支撑这些协议规范。这一办法供给了单一渠道,很简略满意需求的改动。不用花费许多时刻针对每一以太网协议导入软件仓库,在处理器上运转,而是运用现成的东西和软件仓库,支撑悉数的以太网规范。并且,在FPGA渠道上改动设计时,不需求针对每一新协议来规划新电路板。一块电路板可以支撑多种工业以太网协议,然后减小了NIE的费用,下降了长时刻具有本钱。FPGA中完结的工业以太网协议可以在不同的规划和FPGA器材系列之间进行移植,因而,下一代产品可以从头运用相同的IP。Altera及其合作伙伴所供给的工业以太网快速开发解决方案保证了较短的产品面市周期。灵敏的FPGA支撑在终究产品中运用前期工程作业,规划人员可以在最终一刻更改规划,防止PCB重制。

SOPC Builder软件东西

SOPC Builder是规划用于主动交给、装备和集成IP模块的东西,它选用了窗口类型的图形开发环境,用户可以在其间树立悉数的CPU体系,乃至不需求写入 HDL代码。这样,去掉了耗时的手动编码进程,规划人员可以将精力会集在优化解决方案上。

经过图4,可以看到SOPC Builder窗口以及集成到规划中的Altera IP、第三方IP和硬件模块列表。当用户点击这些IP模块时,右侧会打开一个装备窗口,从这儿可以挑选需求的装备选项,参加到用户的体系中。参加所需的 IP后,会看到所选的组件列在主窗口中,窗口左边是现已主动衔接在一起的模块。用户可以随时经过鼠标修正它,从头装备IP组件或许链接,为其运用树立抱负的体系。完结体系后,只需求简略的点击底部的“Generate”按钮,告知SOPC Builder生成一个集成硬件模块,它含有规划人员所挑选的悉数IP以及从GUI中挑选的装备和链接。SOPC Builder生成完好的规划,将其交给Quartus II规划环境,并对体系进行编译,树立HDL仿真模型或许FPGA装备文件。

嵌入式软件开发流程

图5是嵌入式软件的开发流程图。假如是硬件规划人员,那么不需求很大的投入就可以不断修正规划,完结最佳体系。可是,假如是软件工程师,在典型的硬件/软件集成进程中所面对的应战是有必要跟上不断改动的处理器渠道。与修正FPGA和Nios II处理器装备比较,软件更新需求做许多作业,要花较长的时刻来进行更新。因为SOPC Builder还生成含有悉数硬件装备信息的文件,这样,Nios II软件开发环境就可以完结定制软件,树立专用硬件支撑库。这种库含有体系需求的悉数器材驱动以及硬件笼统层,即HAW,提取出拜访硬件的悉数运用程序。假如改动硬件,软件环境会探测到这些改动,在软件工程中主动更新悉数硬件设置和器材驱动。这种主动东西解决方案可以协助硬件和软件工程师更敏捷、简略地修正规划,不会犯错。

图4 SOPC builder窗口截图

图5 嵌入式软件开发流程

责任修正:gt