这次要阐明的一个问题是我在做一个480*320液晶驱动的过程中遇到的,先看一个简略的比照,然后再评论不迟。

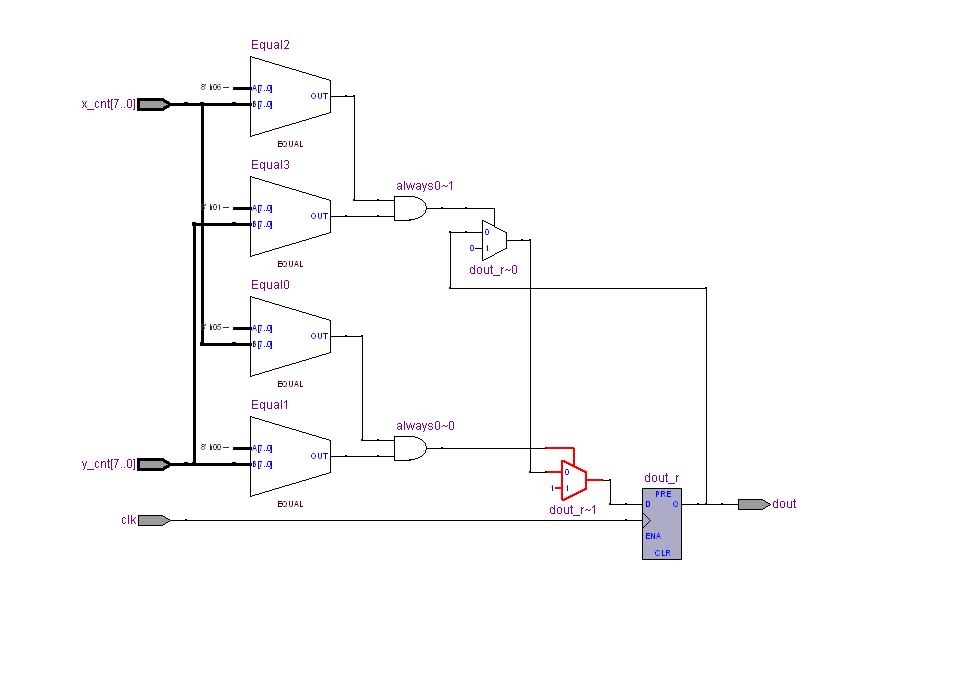

这个程序是在我的液晶驱动规划中提取出来的。假设是x_cnt不断的添加,8bit的x_cnt加一个周期回到0后,y_cnt加1,如此循环,原意是要让下面的dout信号只要在x_cnt>=5 & y_cnt=0或许x_cnt<= 4,y_cnt=1这个区间内为1,其它时间内为0。一般来说会有如下两种描绘,前者是时序逻辑,后者是组合逻辑。当然除了下面两种编码风分外,还能够有很多种不同的编码。这儿仅仅罗列其一阐明一下问题。

Ex2:

input clk;

input[7:0] x_cnt,y_cnt;

output dout;

reg dout_r;

always @ (posedge clk)

if(x_cnt == 8’d5 && y_cnt == 8’d0) dout_r <= 1’b1;

else if(x_cnt == 8’d6 && y_cnt == 8’d1 ) dout_r <= 1’b0;

assign dout = dout_r;

归纳后运用了<1个macrocells。首要运用的是4个等于比较器。然后每个时钟的上升沿做一次判别,细心看上面的RTL视图,其实你还能够发现优先级的问题,这个后边再说。

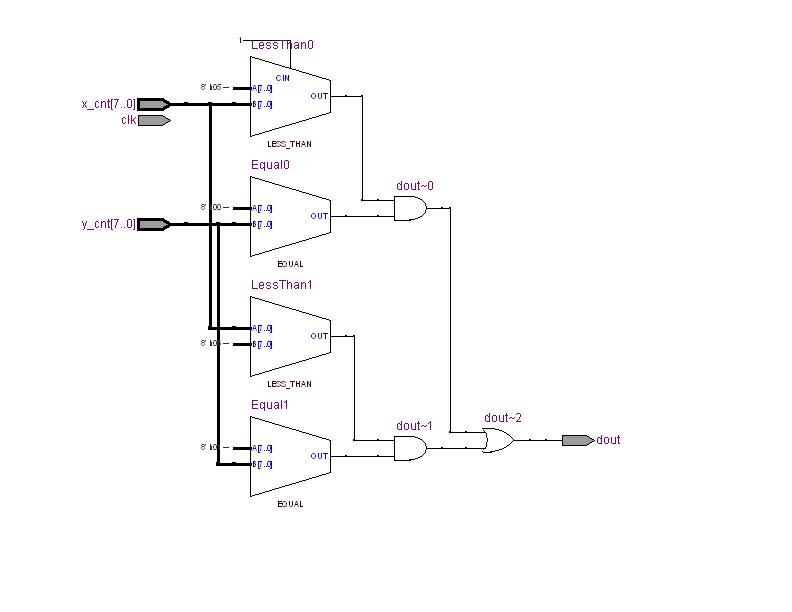

组合逻辑的代码:

input clk;

input[7:0] x_cnt,y_cnt;

output dout;

assign dout = ((x_cnt >= 8’d5 && y_cnt == 8’d0) ||

(x_cnt < 8’d6 && y_cnt == 8’d1 ));

归纳后运用了2个macrocells。用了2个等于比较器,还有2个小于(等于)比较器。可是占用的资源却比前者多出了一倍多,这个好像阐明晰一些问题。其实在这个很简略的规划里,这种资源占用状况还不是很明显,我在做整个项目中用了这两种不同的规划风格后发现:两种不同的coding style得到的macrocells占用个数不同到达10几个(这个可能是比较极点的状况)。当然了,这其间更多的要素可能是布局布线后走线等在不同风格代码下的消耗是不一样的。总归,前者更值得引荐,就是说能用等于比较器直接赋值(哪怕是用成心生成的锁存器来坚持赋值),也不必小于(大于)比较器。