湛 伟(成都华微电子科技有限公司,成都 610041)

摘 要:本文回忆了Serdes的开展进程,提出了Serdes技能分代及其特色,叙述当时国内外Serdes的技能现状,以及Serdes技能的开展趋势,对Serdes架构和各模块技能演化、关键技能应战进行了剖析,并从协议、电路规划、信号完好性、开展趋势几个维度加以具体评论。

关键词:Serdes;PAM4;数据时钟;康复

0 导言

Serdes;PAM4;数据时钟;康复Serdes是英文单词串行器(Serializer)宽和串行器(De-Serializer)的合成词,能够称之为串行解串器。依据其功用来讲,Serdes就是在发送端将并行数据转化为串行数据,在接纳端将串行数据康复为并行数据的电路。

现在,Serdes技能在有线通讯方面现已得到了广泛运用。依照运用衔接的类型,首要分为芯片与光模块的互联;芯片与芯片的互联;以及以太网互连。

以太网接口首要有10BASE-T、10BASE-F、100BASE-T、10BASE-FX、1000BASE-X、1000BASE-T接口,在跨城市互联中将首要用到GE及以上的接口。GE物理接口有1000BASE-X(802.3z规范)和1000BASE-T(802.3ab规范)两种。未来的高速率接口(100G或以上)均为GE类型,为了与100GE兼容,OTU4规范的制定为100GE,高端路由器厂家现在均可供给100GE,并大部分方案开发100GE OTN接口 [1-2] 。能够预见的是未来的高速端口将是以太网和OTN这两种类型。

在以并行通讯主导的内存颗粒的拜访接口范畴,也有分别是海力士和AMD主导的HBM(High BandwidthMemory,高带宽存储器) [3-4] 以及Intel支撑、美光主导的HMC(Hybrid Memory Cube) [5] 等串行接口,作为与DDR5不同的一种演进方向。

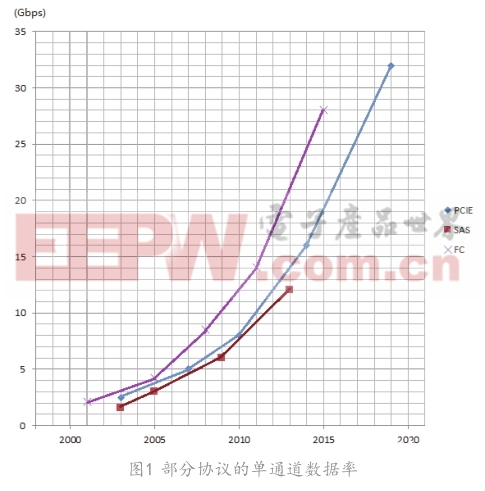

由此咱们能够看到,Serdes现已跟从通讯协议,广泛运用在电信、IT和个人消费电子范畴。而且跟着通讯容量的快速进步,各种通讯协议的单通道数据率也快速进步,例如图1所示的几种协议演进。

1 技能现状

现在,世界上最先进的Serdes单通道为64~128 Gbit/s之间。在功耗方面,除了单通道最大功耗(mW)外,因为电路功耗跟作业的数据率强相关,所以一般也运用每bit耗费的功耗(pJ/b)来衡量。在ISSCC 2019会议上,IBM宣布的单通道128 Gbit/s 1.3 pJ/b的发送器和100 Gbit/s 1.1 pJ/b的接纳器,根本代表了当时世界Serdes技能的最高水平 [6-7] 。

令人留意的是,华为旗下的海思半导体在Serdes范畴也有适当先进的技能,现已形成了从45 nm~7 nm工艺,10 Gbit/s~64 Gbit/s的多款IP核,并在近百款芯片中商用。在2018年和2019年的ISSCC会议上,华为加拿大研讨所先后宣布了依据台积电16 nm 64 Gbit/s和7 nm 60 Gbit/s的Serdes,而且挨近商用,代表着国产Serdes技能的最高水平 [8-9] 。

其他,清华大学、北京大学、东南大学等院校在Serdes范畴研讨也取得了很大的前进,有多篇32Gbit/s、40Gbit/s、50Gbit/s的学术效果 [10-13] 。

2 开展进程

Serdes技能的开展,依本文作者观念,能够分为以下几个阶段。

第1阶段:单通道数据率低于6 Gbit/s,工艺一般选用45 nm及以上。此刻Serdes数据率相对较低,对Serdes电路规划、锁相环(PLL)的目标、链路信号完好性要求较低,接纳端(Receiver,RX)选用固定CTLE参数等能够满意需求。

第2阶段:单通道数据率从6 Gbit/s~15 Gbit/s,工艺水平一般在28 nm~45 nm。此刻,对PLL规划目标要求进步,而且RX的接连时刻线性均衡器(Continuous time linear equalizer,CTLE)、判定反应均衡器(Decision Feedback Equalizer,DFE)要求选用自适应等算法,使得在不同链路运用场景下取得CTLE最优装备,还能依据高低温改变带来的链路信号完好性改变,动态调整接纳DFE参数,使得误码率在协议规则规模以内。

第3阶段:单通道数据率从15 Gbit/s到30 Gbit/s,工艺水平一般在16 nm到28 nm。工艺参数对电路的影响、功耗等问题变得更为杰出,需求愈加精密的规划电路以及封装、单板、衔接器等。

第4阶段:单通道最高数据率大于30 Gbit/s以上,选用16 nm乃至更先进的工艺水平。一般在30 Gbit/s以下的运用能够选用传统的NRZ编码,30 Gbit/s以上的运用需求考虑选用PAM-4编码,经过献身信号的起伏来交换时序上的宽余。因而,Serdes架构有了很大改变,一般会选用DSP和高速ADC等技能来处理PAM-4编码 [14-19] 。

一个完好的Serdes体系,包含参阅时钟,PLL,上层协议,编解码,发送端(Transmitter,TX),信道,接纳端(RX)等部分组成。其间有源器材首要是芯片自身如Serdes的收发端,外部的ESD防护器材,光模块等;无源器材包含单板、背板及走线,AC耦合电容衔接器,背板,SMA头,线缆等。

下面,咱们进一步从这些方面评论Serdes的开展趋势和应战。

3 协议

Serdes一般作为通讯协议的物理层的物理介质(PMA)子层部分,由此要严厉准从协议规则。Serdes作为一个芯片的底层模块,除了满意单一的通讯协议数据率越来越高的应战,依据本钱等考虑,一般还要求同一个Serdes IP核能够兼容多种协议。

从Serdes规划的视点,常见的通讯协议能够分为几大类别。

第1类:一般的协议。此类协议除了数据率,位宽及其电气参数差异外,没有对Serdes提出其他特别要求。

第2类:PCIE、SAS、SATA等协议。这几种协议,要求依据链路的恶劣状况进行调整速率,即速率可自洽谈,这时Serdes能够被上层操控。而且因为多运用在个人电脑、数据中心等范畴,对EMI辐射有要求,所以要求Serdes有对扩频时钟(SSC)的发生和接纳才干。而且PCIE支撑热插拔,由此要能够检测对端器材是否在位,满意热插拔需求。其他还要支撑功耗办理等功用 [20-21] 。

第3类:PON协议。此类协议要求支撑接连(Continue)收发和突发(Burst)收发方式,而一般CDR会对接连长时刻的1信号或许0信号发生确定反常,因而CDR需求特其他架构才干满意此类协议的要求 [22] 。

4 锁相环

常见的锁相环一般依据LC振动器(LC VCO)或许环形振动器(Ring VCO)结构。

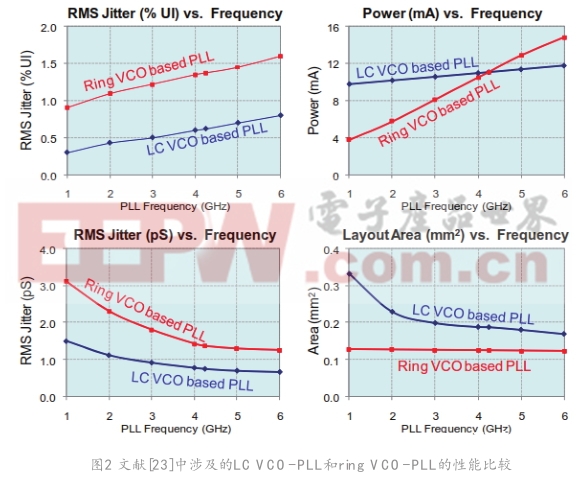

环形振动器易集成、面积小、且简略发生多相位的时钟。LC振动器的电感占用芯片面积较大,规划难度较高,长处是相噪功用更好。可是跟着Serdes数据率的进步,电感越小谐振频率越高,所以电感占用面积大的缺陷有所缓解。反而是环形振动器PLL的功耗、相噪等问题,无法满意更高的要求。可是跟着Serdes对PLL频率、相噪、功耗等提出了越来越高的要求。在10 Gbps以上的Serdes规划中,一般会运用依据LC VCO的PLL,以取得更好的相噪水平。

从LC VCO-PLL和ring VCO-PLL的功用比较咱们能够看出:LC VCO-PLL在颤动方面具有较大优势,在约(4~5)GHz以下的低频运用时,ring VCO-PLL在功耗和面积上有必定优势。但跟着频率的愈加,ringVCO需求更大的电流来进步振动频率,LC VCO占最大面积的电感和电容器材将更小,所以功耗和面积缺陷不再那么杰出了。

一般来说,在5~8 GHz以下的运用中,依据ringVCO的PLL是可行的。假如在更高的频率,依据LCVCO的PLL更为适宜。

5 发送端

发送端首要功用包含如下。

串行器:将并行信号转化为串行信号。

前馈均衡器(FFE):完成预加剧或许去减重,以补偿信道对信号的衰减效果。

驱动器:提过对输出信号摆幅、上升下降沿等可调的驱动才干。

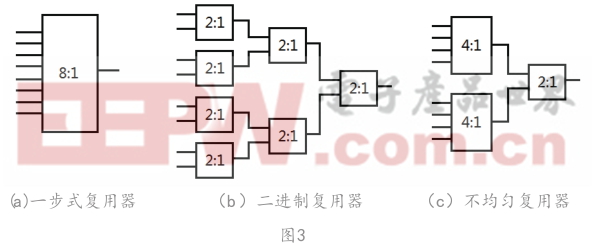

串行器的中心是多路复用器电路,常见的有3类:一步式的多路复用器,二进制的多路复用器,多种复用器组合不均匀串行器,如图3所示。

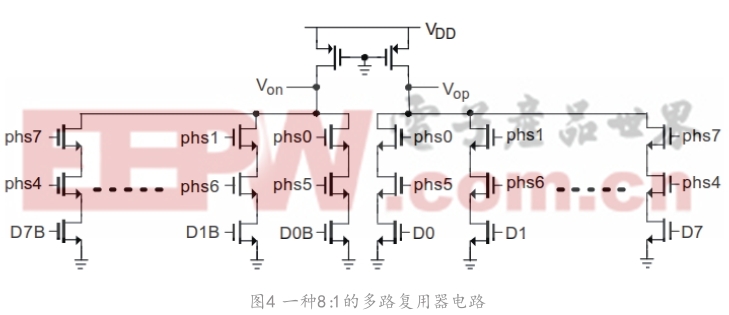

一种8:1的多路复用器如图4所示。Phs0~Phs7是同频率但等相位差的时钟,只要在Phs7和Phs4一起为高时,数据D7B和D7才干被送出;只要在Phs0和Phs5一起为高时,数据D0B和D0才干被送出,顺次类推。

循环的等相位差时钟,将数据D0~D7和D0B ~D7B顺次串行高速输出,即可到达并行转串行的意图。此类结构长处在于电路简略,缺陷是难以运用在数据位宽较宽的场景。而且在高速并串转化时,对时钟相位的颤动等要求很高,而变得难以完成。也就是说,一步式复用器的最高作业速率低于二进制复用器,所以一步式复用器一般运用在低速Serdes并串转化电路中,或许作为不均匀串行器的第1级。

不均匀复用器,既能够灵敏装备位宽,也避免了一步式复用器对多相时钟的高目标要求,而且比二级制复用器更高效,因而是一种很合适高速串行器的结构。

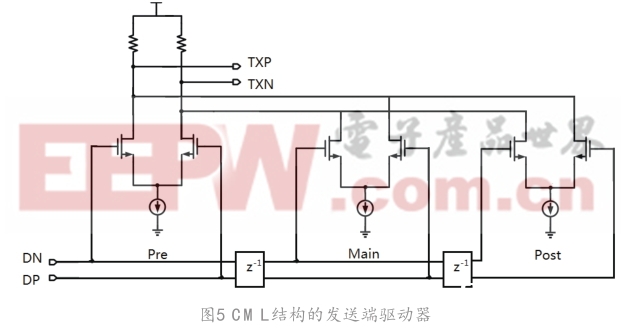

发送端的驱动端电路,常见的是CML和SST结构。

CML结构自身便利电流叠加,所以很简略完成预加剧功用。可是输出摆幅与输出阻抗和驱动电流的乘积相关,输出阻抗一般又被约束在50~100 Ω,因而要取得大摆幅就必须运用较大的驱动电流,使得功耗居高不下。这在功耗问题日益杰出的今日,现已变得无法承受。

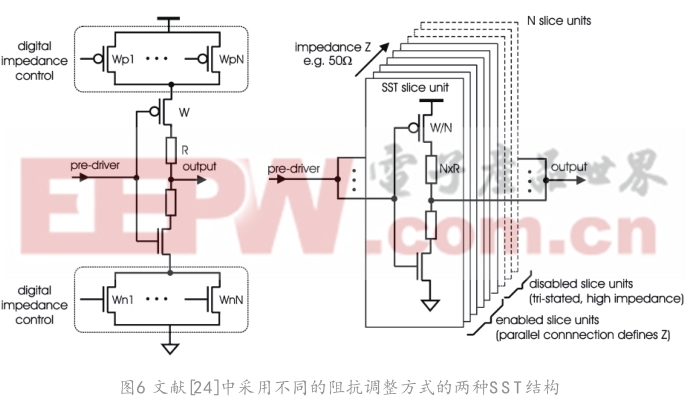

文献[24]中的两种不同阻抗调整方法的SST结构如图所示,SST结构的输出摆幅与其电源电压直接相关,一般来说发生相同摆幅,SST结构的功耗只要CML结构的1/4左右,因而在10 Gbps以上的Serdes中越来越遭到喜爱。

可是SST结构的预加剧信号叠加比较CML结构更为杂乱。使问题愈加困难的是,选用并联SST等结构来完成预加剧功用时,因为开关的MOS管数量不同,阻抗匹配难以确保。因而,一般需求阻抗校准电路和状况机来确保初始化时,Serdes 发送端的阻抗能够匹配在差分100 Ω左右。

6 接纳端

信道的插损与信号频率成正比,频率越高衰减越大。所以跟着Serdes数据率进步,信道的衰减也越来越严峻。为了补偿信道的衰减,一般需求在发送端预加剧功用和接纳端均衡功用。接纳端的均衡器一般由CTLE和DFE构成。CTLE和DFE现已广泛运用于当时的Serdes架构中。

RX规划面对的几个应战是:更优的DFE拓扑和CDR拓扑,以及更优的自适应算法。

DFE架构阅历了全速直接DFE(Full rate directDFE)、半速直接DFE(Half rate direct DFE)、打开全速DFE(Full rate unrolled DFE)、打开半速DFE(Unrolled half rate DFE)和多路复用半速DFE(Multiplexed half rateDFE)等结构。因为打开式和多路复用等结构,不必经过电流加法电路对DFE tap进行求和,而使得时序比直接式DFE更宽松,更合适用于处理速率进步带来的时序严重问题。

依据RX输入数据和本地时钟之间的相位联系,能够把CDR体系结构分为3类 [25] 。

1)运用反应相位盯梢的拓扑,包含依据锁相环结构的CDR(PLL based CDR)、推迟确定回路(DLLbased CDR)、相位插值器(Phase interpolatorbased CDR)和注入确定(Injection-locked basedCDR)结构。

2)无反应相位盯梢的过采样(Over-sampling)拓扑。

3)运用相位对准但无反应相位盯梢的拓扑,包含门控振动器(Gated oscillator)和高Q值带通滤波器结构。

也可依据运用场景将CDR分为突发方式和接连方式的CDR。突发方式体系一般用于点对多点运用中,不同的发送方在突发之间传输具有静默时刻距离的包数据。

每逢恳求传输数据包时,数据传输链路被从头激活,而且在其他时刻坚持不活动状况,如以太网无源光网络(EPON)、千兆无源光网络(GPON)等。突发方式CDR结构一般选用无反应相位盯梢的拓扑结构,如门控振动器和过采样技能。依据相位插值器的CDR不存在颤动峰值或安稳性问题,具有无限的相位捕获规模,但存在量化差错。

因而,需求依据芯片不同的运用场景来挑选最佳的Serdes CDR结构。

自适应算法能够由数字逻辑状况机来履行,也能够固件的方式烧录在片上MCU中履行。例如PCIE等协议在速率切换时,要求24 ms以内到达规则的误码率以下,不然洽谈失利,留给自适应履行的时刻十分有限。

因而,就需求规划合理的自适应算法,或许进步状况机或许MCU的运转频率,才干契合协议要求。

7 信号完好性

因为频率越高插损越大的链路参数特性,跟着Serdes通道的数据率越高,对芯片封装、在测验时常用的Socket夹具、PCB走线处理、衔接器等构成的信号完好性也越灵敏。高速Serdes对PCB走线的信号完好性提出了越来越严苛的要求,例如PCB板材的选取,过孔的处理,是否需求背钻等等,都是信号完好性所要考虑的问题。

在5~8 Gbit/s以下的Serdes单板PCB规划时,一般挑选常用的FR4等级板材就能满意信号完好性的要求;在更高速的PCB运用时,则要考虑M4、M6或许同等级的PCB板材。一起,需求对过孔进行埋孔、背钻等做特别处理,这样也大幅增加了投板本钱。

8 定论

通讯事务关于Serdes数据率的需求日益增长,当时依据CMOS工艺完成的Serdes最高单通道数据率现已到达128 bit/s,不管关于CMOS电路规划仍是链路信号完好性,单通道数据率的进一步进步现已变得越来越困难。与此一起,许多体系运用对Serdes的功耗的还有严苛的要求,也是规划人员面对的巨大应战之一。

硅光子技能能够依据硅和硅衬底资料,使用CMOS制程将电信号转化为光信号传输。光代替链路的铜线,能够得到很好的传输数据率和极低的损耗。假如硅光子技能取得打破和成熟,加上单板的光走线,能够完成芯片与芯片之间的光互联,那么,Serdes技能的侧重点会变得很大的不同,将对驱动才干要求大大的下降。因而,硅光子技能是一种极具可能性的演进方向 [26-28] 。参阅文献

[1] 1000BASE-RH PHY system simulations[S].IEEE802.3bv Task Force,2015.

[2] Cisco SFP Optics For Gigabit Ethernet Applications[J/OL].Cisco Systems,2010.

[3] O’ConnorC M.Highlights of the High BandwidthMemory (HBM) Standard[C].Nvidia Memory论坛,2014.

[4] Morgan T P.Future Nvidia ‘Pascal’ GPUs Pack 3DMemory, Homegrown Interconnect[C].terpriseTech,2014.

[5] HMC联盟.Hybrid Memory Cube Specification2.1[S],2015.

[6] Toprak-Deniz Z.A 128Gb/s 1.3pJ/b PAM-4Transmitter with Reconfigurable 3-Tap FFE in 14nmCMOS[C],ISSCC2019:122-124.

[7] Cevrero A.A 100Gb/s 1.1pJ/b PAM-4 RX with Dual-Mode 1-Tap PAM- 4 / 3-Tap NRZ Speculative DFE in14nm CMOS FinFET[C].ISSCC2019:112-113.

[8] LaCroix M A.A 60Gb/s PAM-4 ADC-DSP Transceiverin 7nm CMOS with SNR-Based Adaptive Power ScalingAchieving 6.9pJ/b at 32dB Loss[C].ISSCC2019:114-116.

[9] Wang L.A 64Gb/s PAM-4 Transceiver Utilizingan Adaptive Threshold ADC in 16nm FinFET[C].ISSCC2018:110-111.

[10] Tang L.A 32Gb/s 133mW PAM-4 Transceiver withDFE Based on Adaptive Clock Phase and ThresholdVoltage in 65nm CMOS[C],ISSCC2018:114-115.

[11] Lv F.A 50Gb/s Low Power PAM4 SerDesTransmitter with 4-tap FFE and High Linearity OutputVoltage in 65nm CMOS Technology[C].IEEE CustomIntegrated,2015:1441-1450.

[12] Huang K.A 80 mW 40 Gb/s Transmitter WithAutomatic Serializing Time Window Search and 2-tapPre-Emphasis in 65 nm CMOS Technology[J].IEEETRANSACTIONS ON CIRCUITS AND SYSTEMS,2015.

[13] Zheng X.An Improved 40 Gb/s CDR with Jitter-Suppression Filters and Phase-CompensatingInterpolators[J].IEEE Asian Solid-State CircuitsConference,2016:85-88.

[14] Pisati M.A Sub-250mW 1-to-56Gb/s Continuous-Range PAM-4 42.5dB IL ADC/DAC-Based Transceiverin 7nm FinFET[C].ISSCC2019:116-117.

[15] Ali T.A 180mW 56Gb/s DSP-Based Transceiver forHigh-Density IOs in Data Center Switches in 7nm FinFETTechnology[C].ISSCC2019:118-119.

[16] Peng P J.A 112Gb/s PAM-4 Voltage-ModeTransmitter with 4-Tap Two-Step FFE and AutomaticPhase Alignment Techniques in 40nm CMOS[C].ISSCC2019:124-125.

[17] Kim J.A 112Gb/s PAM-4 Transmitter with 3-TapFFE in 10nm CMOS[C].ISSCC2018:102-103.

[18] Upadhyaya P.A Fully Adaptive 19-to-56Gb/s PAM-4 Wireline Transceiver with a Configurable ADC in 16nmFinFET[C].ISSCC2018:108-109.

[19] Depaoli E.A 4.9pJ/b 16-to-64Gb/s PAM-4 VSR Transceiver in 28nm FDSOI CMOS[C].ISSCC2018:112-113.

[20] PCI Express® Base Specification Revision 4.0Version 1.0[S].PCI-SIG,2017.

[21] Serial Attached SCSI – 4 (SAS-4) draft[S].2016.

[22] Gigabit-capable Passive Optical Networks (GPON):General characteristics[S].ITU-T,2003-2012.

[23] Fischette D.A 45-nm SOI-CMOS Dual-PLLProcessor Clock System for Multi-Protocol I/O[J].AMD,2011.

[24] Kossel M.A T-Coil-Enhanced 8.5 Gb/s High-SwingSST Transmitter in 65 nm Bulk CMOS With <-16 dBReturn Loss Over 10 GHz Bandwidth[J].IEEE JOURNALOF SOLID-STATE CIRCUITS,2008,43(12).

[25] Hsieh M T.Single chip high-speed serial linkcommunicaitons for multi-channel and multi-standardapplications[J],2008(11).

[26] 我国硅光子职业和硅光子技能开展剖析陈述2017[N].重磅数据,2018.

[27] 王颖轩.硅光子职业剖析[J/OL].2017.

[28] Ahmed A H.A 6V Swing 3.6% THD > 40GHz Driverwith 4.5× Bandwidth Extension for a 272Gb/s Dual-Polarization 16-QAM Silicon Photonic Transmitter[C].

ISSCC2019:484-485.

作者简介:

湛伟(1981—),男,硕士,副主任工程师,首要研讨方向:Serdes电路规划与运用,E-mail:zhanweisu33@126.com。

本文来源于科技期刊《电子产品世界》2019年第9期第48页,欢迎您写论文时引证,并注明出处。