传统嵌入式视觉体系选用FPGA/处理器组合来完结,也有越来越多地运用将高性能处理器与FPGA相结合的片上体系来完结。在本文中咱们将会介绍嵌入式视觉体系的高档元素;怎么简洁便利地运用软件 API 和 IP 库构建嵌入式视觉体系,怎么把算法开发的增值部分添加到图画处理链中。

从监控摄像头号简略监控体系到更高档的运用,例如当今最新款轿车装备的高档驾驶员辅佐体系 (ADAS)和先进出产设备及工厂里运用的机器视觉,嵌入式视觉体系已在一系列运用中得到运用。不管何种运用,嵌入式视觉体系都具有一些共同之处,整体来讲它们可以分为下列三大类:

设备接口 — 供给到所选成像设备的接口。依据挑选的设备类型,供给所需的时钟、偏置和装备数据。这样还可以从设备接纳图画数据,依据需求进行解码和格局化,以供图画处理链做进一步处理。

图画处理链 — 经过设备接口接纳图画数据并进行五颜六色滤波器阵列内插和色域转化(即从五颜六色转化到灰度)等操作。这部分仍处于咱们对接纳到的图画运用很多算法的图画处理链内。这些可以是降噪或边缘增强等简略算法,也可以是方针辨认或光流等杂乱得多的算法。常见状况是在图画处理链的上游部分调用算法完结计划。当然图画处理链上游的完结杂乱性取决于要完结的运用。而输出格局化部分(行将处理后的图画数据转化为正确格局,以输出到显现器或是经过通讯接口输出)被称为下流部分。

体系监督与操控 – 这是一项独立于设备接口和图画处理链的类别,它从两个方面供给体系监督和操控。第一个坐落设备内部,它供给:

图画处理链的装备

图画剖析功用

在算法履行过程中依据要求更新图画处理链

第二个是更广泛的嵌入式视觉体系的操控与办理,它供给:

电源办理和图画设备上电排序

履行自检及其他体系办理功用

网络支撑通讯或点对点通讯

在初次成像操作前经过 I2C 或 SPI 装备图画设备

部分运用答应体系监督功用拜访帧存储器并在其间的帧上履行算法。在这种状况下体系监督可以构成图画处理链的一部分。

这三大类别由于每个阶段内涵的难点不同,需求不同的完结办法。设备接口和图画处理链都要求有才能处理带宽高数据,然后在内部完结图画处理链,在外部从体系传输图画数据。而体系监督与操控要求可以处理和呼应经过通讯接口接纳到的指令并为外部通讯供给支撑。假如体系监督也要构成图画处理链的组成部分,就需求一个高性能处理器。

照此,传统嵌入式视觉体系选用FPGA/处理器组合来完结,也有越来越多地运用将高性能处理器与FPGA相结合的片上体系来完结。在咱们演示上述几个方面怎么结合在一起之前,咱们先来了解一下这三个类别中每一个的不同难点。

设备接口

传感器接口由运用所挑选的设备决议,大多数嵌入式视觉运用运用 CMOS 图画传感器 (CIS)。一般状况下这些传感器运用 CMOS 并行输出总线,用操控信号提示行和帧的有用次序,或许运用速率更高的串行通讯,完结较简略的体系接口,但会导致 FPGA 完结计划略显杂乱。与并行总线比较,这些串行数据流能经过更少数量的通道传输图画,由于它们以快得多的数据速率运转,因而比较并行接口而言,能让成像器支撑更高的帧速率。为完结同步,常见的做法是让包含图画及其它数据字的数据通道与包含用于界说数据通道上的内容的代码字的同步通道相结合。与数据通道和同步通道结合的还有一个时钟通道,由于该接口选用源同步。这些高速串行通道一般完结为 LVDS 或微摆幅差分信号 (Reduced Swing LVDS),以下降体系噪声和功耗。

不管输出图画格局怎么,通常是 CIS 设备在获取任何图画之前需求由嵌入式视觉体系加以装备。这是由 CIS 设备的多功用性形成的。这种多功用性在供给强壮的片上处理功用的一起,也需求在输出图画前运用正确的设置进行装备。这些接口对带宽的要求没有图画传输要求的那么高,因而常常运用 I2C 或 SPI 接口规范。

由于所需的图画数据带宽较高,常常把该接口完结在 FPGA 中,这样更便于与图画处理链集成。该 CIS 设备的装备接口一般运用 I2C 或 SPI,它们既可以用 FPGA 完结,也可以用支撑这种接口的体系监督与操控处理器完结。

图画处理链

图画处理链由上下流元件和接口组成,像素数据经过设备接口输出。可是接纳到的像素的格局或许不能用于正确显现图画。咱们或许需求进行图画校对,尤其是在运用五颜六色成像器的状况下。 为保持所需数据率下的吞吐量,图画处理链常完结在 FPGA 中,以发挥其并行优势。这样可以生成图画处理流水线,使得处理链的每一步都将并行完结,然后取得更高的帧速率。可是对部分运用咱们有必要考虑时延,尤其是对高档驾驶员辅佐体系 (ADAS) 这样的体系而言。为有用树立图画处理链,咱们需求运用通用互联协议作为图画处理内核的根底,然后便利处理 IP 的互联。这样可以带来两重优点:一是可以重复运用的库;二是由于每个 IP 核旨在依据界说的规范接纳和发送数据,然后便利流水线的树立。这里有多种常用的协议可供选用,其间最常见的是 AXI,因其具有一起支撑内存映射接口和流接口的灵活性。

图画处理链内的典型处理阶段包含:

五颜六色滤波器阵列 – 在CIS设备上用贝尔 (Bayer) 滤色片生成每个像素的五颜六色

色域转化 – 从RGB转化为YUV

色度重采样 – 将 YUV 像素转化为更高效的像素编码

运用图画校对算法,比方颜色校对或伽马校对,或是进行图画增强或降噪

在下流侧咱们可以装备视频输出时序,然后在输出到指定的方针前转化回本机并行输出视频格局

部分体系也运用外部内存,例如DDR 的内存作为帧存储,在 SoC 内部 DDR 内存也往往供给给 SoC 的处理器侧。同享内存空间的才能让体系监督侧能经过千兆位以太网或 USB 传输数据,或成为图画处理链的延伸。

体系监督

传统上该功用完结在处理器内部,可以处理相关指令,以按运用需求对图画处理链进行装备。为接纳和处理指令,体系监督功用有必要可以支撑从简略的 RS232、千兆位以太网、USB、PCIe 到 CAN 轿车专用接口等一系列不同的通讯接口。

只需嵌入式视觉体系的架构可以支撑,咱们就能运用处理器来生成图画叠加信息,可供叠加在输出图画上。在可以拜访图画数据的条件下,咱们也可以运用处理器对图画展开进一步处理,或是搜集统计数据(像素值散布柱状图等)。这样体系监督就成为图画处理链的一部分,让开发人员能运用各种开源图画处理库,如OpenCV、OpenCL 和 OpenVX。

EVK运用实例

在说明嵌入式视觉体系的根本元素后,下文将演示这些概念,展现怎么归纳运用它们创立出可作业的体系。该实例将展现咱们怎么运用安富利 MicroZed 嵌入式视觉套件 (EVK)创立嵌入式视觉体系。

该套件运用安森美 Python 1300C 成像设备和赛灵思 Zynq 7020。 Python 1300C 是一个 1280 像素&TImes;1024行的颜色图画传感器,经过 SPI 接口装备。此类型传感器运用串行输出完结高帧率,一起EVK 支撑经过 HDMI 接口输出图画到显现器。

Zynq 7020 为嵌入式视觉体系的完结供给了一个极好的渠道,由于咱们能运用 FPGA 架构中的可编程逻辑 (PL) 完结该设备的接口和图画处理链。而 FPGA 架构中的 ARM A9双核处理器(即处理体系 (PS))可用于依据咱们的需求完结体系监督功用和图画处理链延伸。

为开发该运用,咱们将用到两个 SoC 开发工具。一个是赛灵思 Vivado 2015.4,另一个是赛灵思SDK 2015.4。在 Vivado 中咱们将完结设备的接口、图画处理链,在 Zynq 内装备 PS,树立 PS 到 PL 存储器映射以完结下列操作:

依据图画巨细和帧速率所要求的参数以及所需操作在图画处理链内装备 IP。为此咱们将在 PS和 PL 间运用通用 AXI 互联,以 PS 为主设备。运用该接口咱们能在 PS 和 PL 间完结 高达 1,200Mbps 的传输速率。

如有必要,将处理器的 DDR 内存置于图画处理链中,以便处理器拜访。为此咱们将在 PL 和 PS 间运用高性能 AXI 互联,以 PL 为主设备。运用该接口咱们能在 PL 和 PS DDR 内存间完结高达 2,400Mbps 的传输速率。

该演示将运用 HDMI 展现怎么将图画输出到显现器上。适当有用的是,EVK 制造商安富利为Python 1300C 供给了一个设备接口 IP 模块,并为在 EVK 上接口输出到 HDMI 设备供给了一个 HDMI 输出 IP 模块。咱们将本实例中运用一切这些模块。在 Vivado 中咱们可以运用 IPXact 格局把这些 IP 模块添加到 Vivado IP 目录中。

图画处理链将与安森美设备接口并履行下列处理阶段,除了 Python 1300C 和 HDMI IP 核,一切运用的 IP 核均来自 Vivado 中的规范赛灵思图画处理 IP 库(实践 IP 核的称号在下面显现):

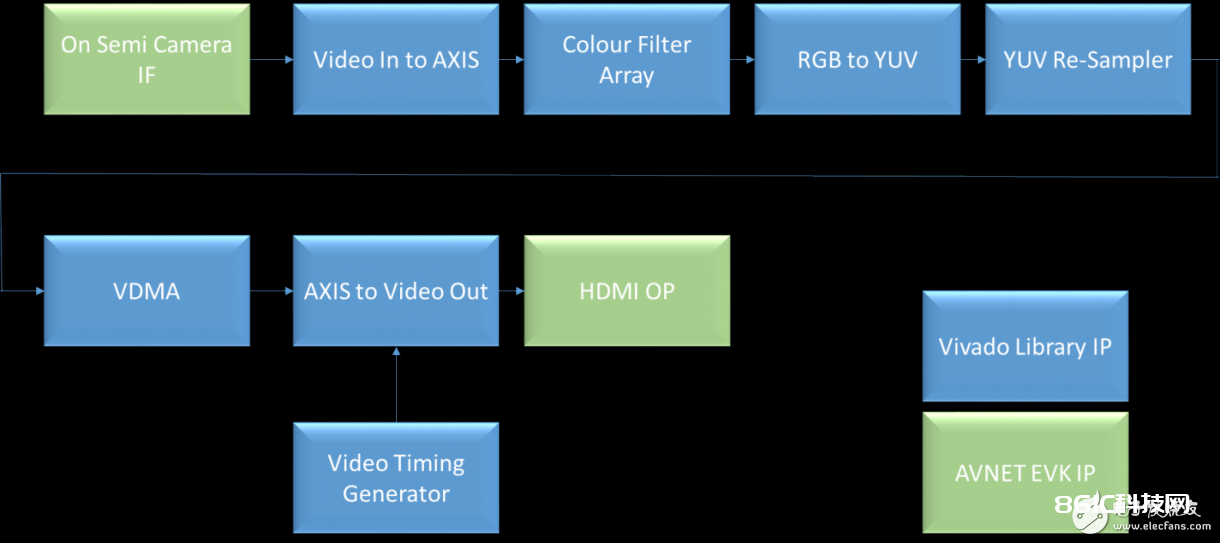

图1:图画处理流程

将来自 Python 接口 IP 的并行视频和水平及笔直同步转化为 AXIS Stream,以便咱们可以将其与后续的图画处理IP核接口。 视频输入到 AXIS (Video in to AXIS)

五颜六色滤波器阵列运用贝尔滤色片为每个输出像素赋予一个 RGB 值(仅以 R、G 或 B 表明)。五颜六色滤波器阵列插值 (Color Filter Array interpolaTIon)

RGB 到 YUV色域转化,将 RGB 色域转化为 HDMI 驱动器优选的 YUV 色域输出格局。RGB 到 YCRCB色域转化器 (RGB to YCRCB Color-Space Convertor)

将 YUV 从 4:4:4 格局从头缩放为 4:2:2 格局。 色度重采样 (Chroma Resampler)

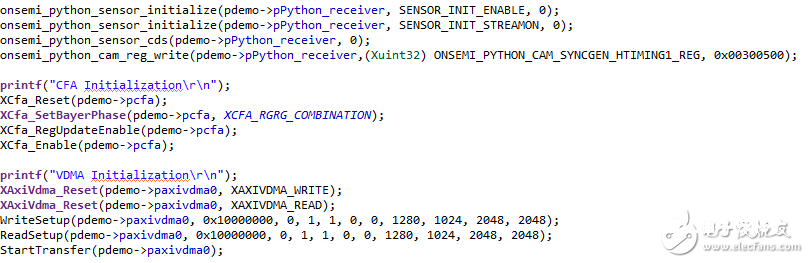

装备视频 DMA 以传输图画帧到 PS DDR。 AXI VDMA

装备同一视频 DMA,以从 PS DDR 读取图画帧。 AXI VDMA

将 AXI Stream 转化回并行格局。 AXIS 到视频输出

为输出视频时序供给时序参阅生成器。 视频时序操控器

除了保证体系正常运转,咱们还需求两个 AXI 互联。一个是高性能 AXI 互联,另一个是通用AXI 互联,以及每个时钟域所需的复位模块。

图画处理运用需求一系列的时钟域,大部分时钟域咱们可以运用 Zynq 内部的 PS 供给给 PL的时钟。就该运用而言,咱们需求下列时钟:

108 MHz – 这是以 1280×1024 分辨率和 60 Hz帧速率输出图画所需的像素时钟速率。

75 MHz – 用于存储器映射的 AXI 和 AXI Lite 接口。

150 MHz – 用于图画处理链,也称为AXI Streaming时钟。AXI Stream 时钟的速率有必要至少与像素速率相同。可是咱们有必要考虑处理链中的一切 IP 核的吞吐量。尽管大多数模块可以每时钟周期处理一个像素,留出部分裕度并削减所需的缓存是正确的做法。

200 MHz – 供给给 Python 1300C CIS 设备作为基准。

为完结像素时钟,咱们需求运用时钟导游来生成该 108MHz 像素时钟,由于该时钟需求极为准确的设置。尽管在用 PL 架构时钟设置时,75MHz和150MHz时钟答应部分容差,但 200MHz时钟也要求准确。与 108MHz 时钟不同的是该时钟可由 PL 架构时钟准确生成。

所运用的 IP 模块的时钟结构如下表所示:

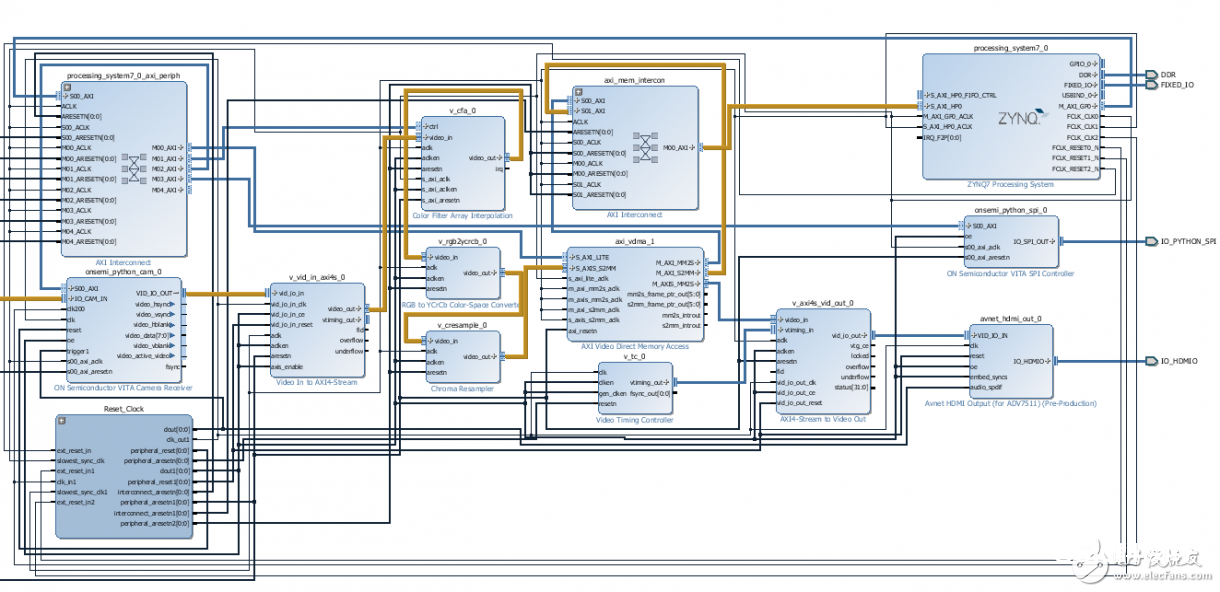

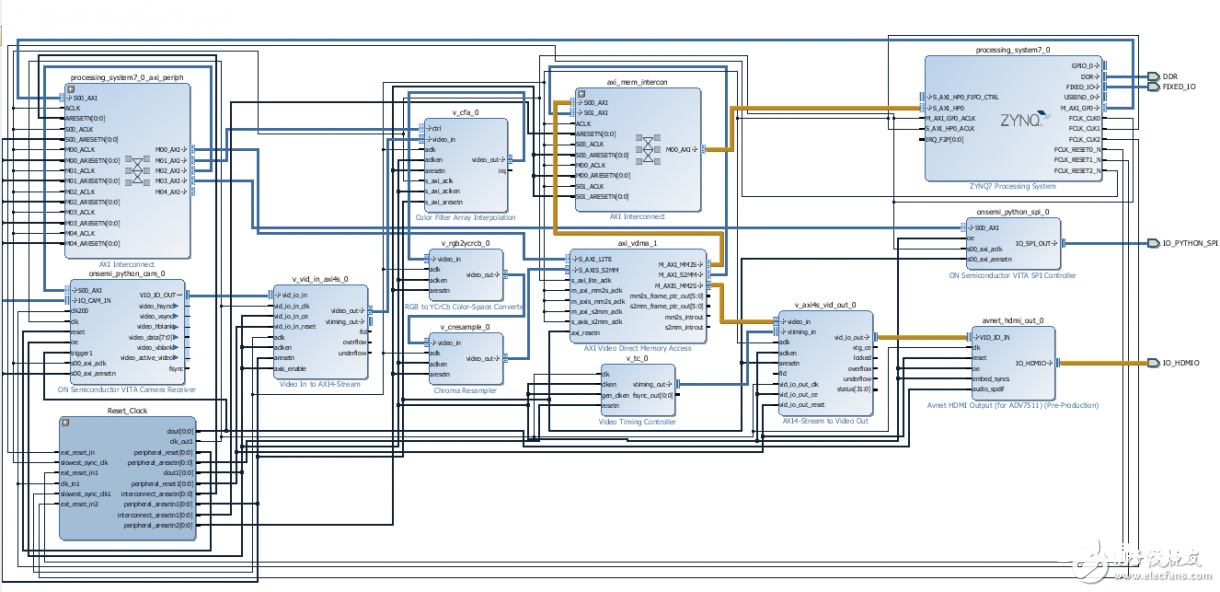

在 Vivavdo 方框图编辑器中的整个完结计划如下面两个图所示。这两个图别离显现的是图画处理链的上游和下流。您还可以看到运用通用 AXI 互联和高性能 AXI 互联完结的 ARM 内核处理器的互联状况。

图2:EVK实例规划 — 杰出显现的是上游图画处理链

图3:EVK实例规划 — 杰出显现的是下流图画处理链

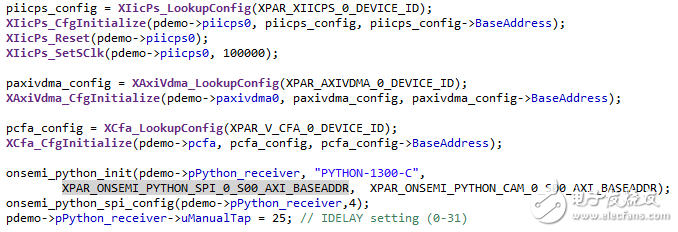

一旦咱们完结规划验证,并为AXI外设分配地址(可主动完结)后,咱们就能在 Vivado 2015.4 中构建硬件并将其导入到 SDK 2015.4 软件开发环境中。咱们需求在该环境中编写一些简略软件,让体系启动并运转。

在 SDK 内部,咱们不只需求在 Zynq 内装备规划,还需求在运用规划之前在 EVK 上装备部分元素。记住在本实例中 PS 起着体系监督和操控功用,因而有必要对整个嵌入式视觉体系进行装备,而不只仅是在 Zynq 中装备 Vivado 规划。

咱们需求开发用于装备下列内容的软件:

运用SPI 接口的 Python 1300C 摄像头

AXI Python 1300C 接口模块

AXI VDMA,从 DDR 内存读取和向 DDR 内存写入帧

AXI 五颜六色滤波器阵列

用于 AD7511 的 HDMI 输出设备。该设备运用 I2C 进行装备

I2C 多路复用器及其衔接的相关外设

用于操控 Python 1300C 设备电源轨的 I2C IO 扩展器

该 EVK 运用 Zynq PS I2C 操控器对 HDMI 输出设备进行装备,来对 Python 设备供电。安富利还向咱们供给了能用来操控 I2C 并进行如下装备的 API:

ADV7511 – 用于 HDMI 输出的 API

CAT9554 – 用于坐落摄像头模块上的 I2C I/O 扩展器的 API

TCA9548 – 用于坐落 EVCC 上的 I2C 多路复用器的 API

PCA9534 – 用于坐落 EVCC 上的 I2C IO 扩展器的 API

OnSemi_Python_SW – 用于 Python 1300C 的 API

XAXIVDMA_EXT – 用于装备 VDMA 的 API

XI%&&&&&%PS_EXT – 用于驱动外部 I2C 的 API

咱们所需做的便是将这些 API 与赛灵思软件 API 耦合,用于图画处理链中的 IP,这样咱们就能快速创立软件可履行文件。要创立软件运用,咱们需求将硬件规划导入到 SDK 中,为硬件创立板级支撑包 (BSP)。该 BSP 内置一切所需的赛灵思 API,在与安富利的 API 耦合后,就可以驱动图画处理链中的硬件和 Zynq。

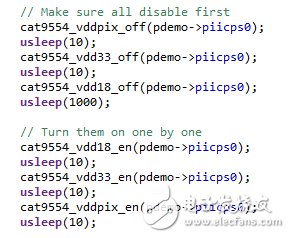

软件自身需求履行下列过程:

初始化一切的 AXI 外设

为图画传感器轨加电

对安森美 Python 1300C、五颜六色滤波器阵列和 VDMA 进行装备

完结这些过程后,当软件运转在 EVK 上您将看到图画正被输出到您所选定的 HDMI 监控器上,如下图所示。

图4:运用演示体系抓取的居民区场景的一帧图画

定论

在本文中咱们介绍了嵌入式视觉体系的高档元素;怎么简洁便利地运用软件 API 和 IP 库构建嵌入式视觉体系,怎么把算法开发的增值部分添加到图画处理链中。