0 引 言

本体系以AD7892SQ和CPLD(杂乱可编程逻辑器件)为中心规划了一个多路信号收集电路,包含模仿多路复用、集成扩大、A/D转化,CPLD操控等。选用硬件描绘言语Verilog HDL编程,经过选用CPLD使数据收集的实时性得到进步。

1 硬件规划

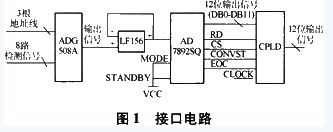

针对多路信号的收集,本体系选用4/8通道ADG508A模仿多路复用器对检测的信号进行挑选,CMOS高速扩大器LF156对选中的信号进行扩大,AD7892SQ完结信号的A/D转化,CPLD完结操控功用。电路如图1所示。

AD7892SQ是美国AD公司出产的LC2MOS型单电源12位A/D转化器,可并行或串行输出。

AD7892SQ A/D转化器具有如下特色:单电源作业(+5 V或+10 V);内部含有采样坚持扩大器;具有高速的串行和并行接口。

AD7892SQ操控字的功用如下:

a)MODE:输入操控字,低电平时为串行输出,高电平时为并行输出,本体系为并行输出;

b)STANDBY:输入操控字,低电平时为睡觉状况(功耗5 mW),高电平时正常作业,一般应用时接高电平;

c)CONVST:发动转化输入端,当此脚由低变高时,使采样坚持器坚持开端转化,应加一个大于25 ns的负脉冲来发动转化;

d)EOC:转化完毕信号,转化完毕时,此脚输出100 ns的低电平脉冲;

e)CS:片选,低电平有用;

f)RD:低电平有用,与CS配合读,使数据输出。

MODE脚接高电平时,AD7892SQ为并行输出,时序如图2所示。

在EOC下降沿时刻内开端采样,便是转化一完毕就开端下次采样,采样时刻fACQ应大于等于200 ns或400 ns,转化完毕后(即E0C的下降沿),当CS和RD有用时,经过t6=40 ns的时刻,就能够在DB0-DB11上取得转化之后的12位数据,CS和一般的片选信号相同,能够一向有用,外加RD的时刻T5也应大于35 ns。CONVST信号t1应大于35 ns,在上升沿时采样坚持器处于坚持状况,开端A/D转化,转化所需的时刻tCONV为1.47μs或1.6μs,转化完毕后,EOC脚输出的t2为大于等于60 ns的负脉冲用来进行中止或数据锁存。由此得出下次采样和本次的输出能够一起进行,因而最小的一次采样转化输出的时刻为1.47+0.2=1.67μs(600 kSPS(千次采样每秒)),最大1.6+0.4=2 μs(即5 00 kSPS),图2中的t9大于等于200 ns,t7近似为5 ns,t3、t4、t8可为0,(此刻t9=tACQ)。

2 程序规划

2.1 体系介绍

体系中的CPLD是结构比较杂乱的可编程逻辑器件,硬件描绘言语规划的操控程序写入CPLD内即可完结其功用。体系收集的数据常常放在数据缓存器中,数据缓存区要求既要有与A/D转化芯片的接口,又要有与体系DSP的接口,以进步数据吞吐率,本体系选用FIF0(先进先出),并且FIF0具有不需求地址寻址的长处[1]。

2.2 体系的软件描绘

本体系选用Verilog HDL言语进行描绘。VerilogHDL被近90%的半导体公司运用,成为一种强壮的规划东西。其长处是[2]:

a)Verilog HDL是一种通用的硬件描绘言语,易学易用;

b)Verilog HDL答应在同一个电路模型内进行不同笼统层次的描绘,规划者能够从开关、门、RTL或许行为等各个层次对电路模型进行界说;

c)绝大大都盛行的归纳东西都支撑VerilogHDL,这是Verilog HDL成为规划者的首选言语的重要原因之一;

d)一切的制作厂商都供给用于Verilog HDL归纳之后的逻辑仿真的元件库,因而运用Verilog HDL进行规划,即可在更广泛的范围内挑选托付制作的厂商;

e)PLI(编程言语接口)是Verilog HDL言语最重要的特性之一,它使得规划者能够经过自己编写C代码来访问Verilog HDL内部的数据结构。

2.3 AD7892SQ描绘

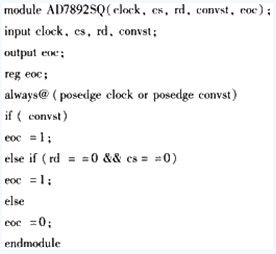

描绘AD7892SQ模块,能够把模块用于收集体系的仿真,以验证FSM(有限状况机)规划的正确性。该模块主要有4个输入信号和1个输出信号,与芯片的操控信号共同。程序如下:

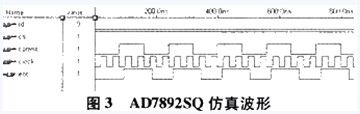

AD7892SQ仿真波形见图3。

2.4 FSM描绘

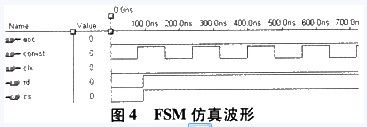

FSM为异步作业。当convst有用时停留在convst_ad状况,且rd和cs都为1,convst为0且处于clock的上升沿时FSM会处于4个状况中的一个状况。图4为FSM仿真波形。

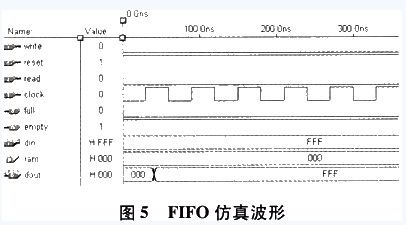

2.5 FIFO描绘

FIFO为同步作业。当reset有用且处于clock的上升沿时,dout为O;reset为1且处于clock上升沿时,read和write组合的4种状况别离对应各自的作业状况。图5为FIFO仿真波形。

3 完毕语

Verilog HDL硬件描绘言语已越来越广泛地应用于EDA(电子规划自动化)范畴,大都EDA规划工程师都用它进行ASIC(专用%&&&&&%)规划和CPLD/FPCA开发。用高档言语进行电路规划,能够灵敏地修正参数,并且极大地进步了电路规划的通用性和可移植性。最终需求指出的是,选用IP核的办法规划电路,不光能够独自运用,并且能够嵌入到AS%&&&&&%或CPLD/FPGA的电路规划中,一起缩短了产品的开发周期,应大力推广。