大多数 FPGA 规划人员都充满热情地展开专业化问题处理和创造性作业,当然,他们作业压力也恰当大,作业流程也十分单调乏味。走运的是,EDA 公司和 FPGA 厂商不断开发新的东西和办法,推动繁琐使命的主动化,协助规划团队集中精力做好创造性作业。下面咱们就来看看 FPGA 东西流程的演进展开,了解一下现代 FPGA 团队是怎么运用 RTL剖析、束缚生成和归纳导历来削减规划迭代的。

如果您现已是一名 FPGA 规划专业人士,那么将具有光辉的作业展开前景,因为越来越多传统上需求 ASIC 完结的规划现已改用 FPGA。跟着新一代芯片工艺技能的推出,规划 ASIC的本钱正呈几何级数增加。与此一起,FPGA 厂商则能运用最新工艺技能完结新一代产品,且不会让客户承当过重的本钱担负。

但不容乐观的是,FPGA 规划恰当杂乱,需求跟 ASIC 流程相同杂乱的东西流程,这往往需求整个规划团队的共同努力才干完结,而不能光靠一名规划人员。因而,FPGA 规划团队在着手ECO 或新项目之前应仔细剖析现有的东西套件。那么好消息呢?便是新一代EDA 东西如漫山遍野般涌出,可助他们一臂之力。规划人员可选择选用规范数据格局且易于装置和运用的东西,简化流程集成作业,并且可以在选定的渠道(不管是 Windows 仍是 Linux)上完本钱机运转。

FPGA 东西流程的展开演进

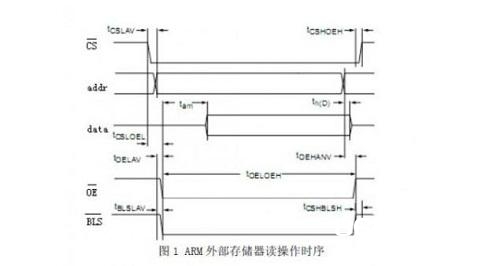

这些年来,FPGA 规划日趋杂乱,东西流程也随之展开,并且越来越像 ASIC流程。上世纪 90 时代,FPGA 流程(见图 1 的流程 A)跟其时的简易 ASIC 流程相同,开始以 RTL 为根底,并选用归纳及布局布线东西。跟着规划变得进一步杂乱化,FPGA 团队在流程中增加了时序剖析功用,协助客户保证规划能按指定的频率运转。今日的 FPGA现已展开为巨大的体系渠道,规划团队一般要经过 RTL 剖析来最小化规划迭代,并保证规划可以完结相应的功能方针。

进而言之,因为今日的 FPGA 规划项目十分巨大杂乱,所以规划人员需求想尽一切办法更好地了解规划的规划和杂乱性,以便更好地操控流程中的东西,加快规划上市进程。现代FPGA 规划团队正在选用一种新式办法,那便是在整个规划流程中贯穿束缚机制。咱们无妨看看当下最盛行的、现已得到赛灵思最新 Vivado 流程支撑的一种束缚办法——Synopsys 规划束缚 (SDC) 格局,以及了解怎么经过 SDC 让规划项目获益。

什么是 SDC?

SDC 是一款根据 TCL 的格局,可用来设定规划方针,包含规划的时序、功耗和面积束缚。一些产品能读取或写入 SDC。一些示例 SDC 束缚包含时序束缚(如创立时钟、创立生成时钟、设置输入推迟和设置输出推迟)和时序破例(如设置过错途径、设置最大推迟、设置最小推迟以及设置多周期途径)。这些 SDC 束缚一般运用于寄存器、时钟、端口、引脚和网络(连线)等规划目标。

需求指出的是,虽然 SDC 是规范化格局,但生成的 SDC 和读取 SDC之间仍是略有差异(不同东西之间有差异)。了解这些差异并活跃采纳办法,有助于防止意外状况的产生。

SDC 不该过于杂乱

SDC 最常见的运用便是束缚归纳。一般说来,规划人员要考虑规划的哪些方面需求束缚,并为其编写 SDC。规划人员一般要履行流程 B 中描绘的流程,初次必定无法进行时序收敛。随后要重复手动盲目测验增加 SDC,以完结时序收敛,或让规划能在指定的频率上作业。许多从事过上述作业的规划人员都诉苦说规划迭代要花好几个星期,往往会延迟规划进程。

迭代的另一个问题在于,数名规划人员可能在不同的地址为 SDC 规划不同的模块。这样规划作业会变得十分杂乱,规划团队有必要想办法验证SDC,防止在芯片级封装阶段呈现层级称号的抵触。要保证进行有用的规划协作,就有必要选用恰当的东西和办法。

流程 C 是现代化流程,除了流程B 的东西之外还选用了剖析、SDC 束缚和高层次归纳技能,在处理上述问题方面发挥了严重作用。

归纳导游

对典型的 FPGA 规划而言,归纳处理计划还处于探究阶段,不管是面积、速度仍是功耗的优化,都存在多个部分最大值和部分最小值。运用智能导游,咱们能完结最佳处理计划,防止归纳东西集合到恣意的部分最小值。最有用的导游之一便是选用过错途径和多周期途径,防止归纳东西为不必要的组件糟蹋名贵的优化时刻。

不过,找到规划中的一切过错途径 (FP) 和多周期途径 (MCP) 并不简略。花上满意的时刻,咱们能找到一些简略的 FP 和 MCP,不过一些触及状态机和计数器的杂乱 FP 和 MCP(特别是在多个层级中)则很难找到。走运的是,FPGA 规划人员可选用Blue Pearl Software 等立异公司推出的东西履行主动化 FP 和 MCO 生成,然后保证完整性、全面性和准确性。此外,这些东西还能为每个 FP 和MCP 供给不同的机制,包含原理图、断言和审阅途径,然后让用户验证其正确性。

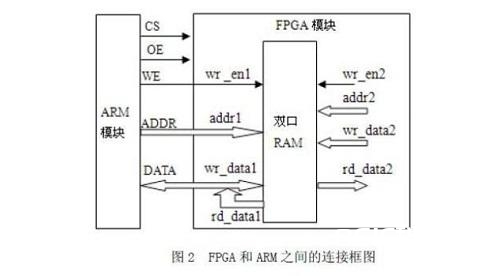

因为 FPGA 厂商和商用 EDA 厂商的协作进一步加强,选用通用接口,规划团队就可以将 Blue Pearl 软件套件集成到他们所喜爱的作业流程中。已然赛灵思的最新 Vivado 规划套件支撑 SDC,那么在不同东西之间交流规划目的就变得极端简略(图 2)。

除了与赛灵思及其他 FPGA 厂商协作外,Blue Pearl 公司还同Synopsys 展开密切协作。这两家公司共同研究怎么让归纳东西承受尽可能多的主动生成的 SDC,一起防止规划人员进行任何手动修正。因为 SDC 格局对不同东西的运用差异很小,因而作业团队快速清晰命名计划是顺利完结互操作性的一大应战。

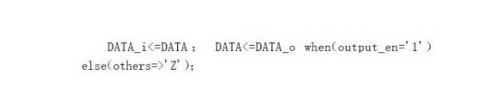

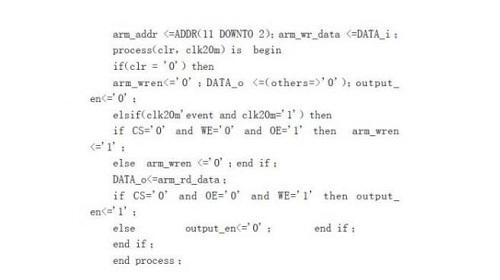

这儿的处理计划是在归纳的第一阶段(编译)后截取映射称号,在 BluePearl 软件套件的 SDC 生成东西中运用称号(见图 3),并为归纳东西的第二阶段(优化)供给恰当的 SDC。该办法给 FPGA 规划人员供给了一个最佳处理计划,无需花时刻处理格局化问题。

以下给出非优化型束缚编写示例:

set_false_path -from

[get_cells

{i_tv80_core.SP[*]}] -to

[get_cells

{i_tv80_core.i_reg.RegsL}]

优化后则为:

set_false_path -from

[get_cells

{i_tv80_core.SP[*]}] -to

[get_cells

{i_tv80_core.i_reg.RegsL_2[7:0]}]

能取得哪些实践的作用?

Blue Pearl 软件套件能完结一些使命的主动化, 规划人员对其成果质量(QoR) 很满意。表 1 显现了用 Blue Pearl 软件套件主动生成 SDC,能将示例规划的 QoR 提高 20%,该示例选用多个 IP 核,其间包含 Verilog 的R1200 和 VHDL 的 AES 加密。

运转 1 未选用 Blue Pearl 软件,成果没有完结时序收敛。规划人员用RTL 规划或东西束缚进行迭代以满意60MHz 的要求很简略就要花上好几个星期的时刻。在运转 2 中,Blue Pearl软件套件几分钟就能生成 SDC,而主动生成的SDC 足以辅导下流东西满意时序要求。

明显,对 FPGA 规划人员来说,下降压力、简化作业的一个好办法便是跟他人相同增加 RTL 剖析、SDC 生成和归纳导游东西。