1.1 CPU 的数据通路

模型计算机硬件体系的数据通路如图 1-1。CPU 的字长为 16 位,内部选用 16 位宽的单总线结构,包含运算器和操控器两个部件。为了便于后边的规划,图中还包含了体系总线和存储器,体系总线选用单总线结构,包含 16 位的数据总线 DB、16 位的地址总线 AB和操控总线 CB。主存、外设与 CPU 共用一组体系总线;CPU 内部总线 IB 与体系总线间经过 DR、AR 相联。主存储器的字长也是 16 位,而且按字编址,不能按字节拜访。

图 1-1 模型计算机硬件体系的数据通路

1.2 指令体系

模型机的指令体系包含各类传送类指令、算术逻辑运算类指令、移位类指令、搬运类指令、子程序调用回来指令、输入输出类指令等。在寻址方法上选用最典型的寻址方法,别离是当即寻址、直接寻址、直接寻址、寄存器寻址、寄存器直接寻址、寄存器变址寻址、相对寻址 7 种。

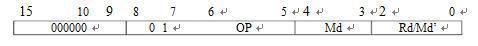

1.2.1 指令格局

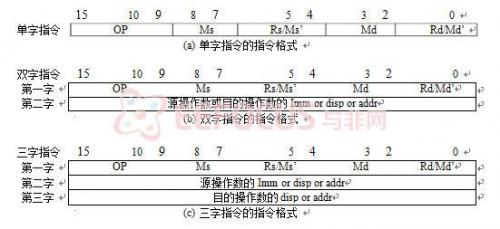

模型机指令格局规整,以单字指令为根底,依据不同的寻址方法可扩展为双字指令和三字指令,如图 1-2所示。指令的第二字和第三字是一些常数,如当即数、直接地址、直接地址、偏移量等。

图 1-2 指令格局

图 1-2中,Ms 表明源操作数的寻址方法,Md 表明意图操作数的寻址方法,Rs 和 Rd别离表明的是源操作数和意图操作数的寄存器号。

1.2.2 寻址方法及编码

在图 1-2中能够看出,寻址方法 Ms、Md 别离由 IR 的 9、8 和 4、3 位表明。各位含义见表 1-1。

2

|

|||||||||||||||||||||||||||||||||||||

表 1-1 寻址方法及编码

1.2.3 双操作数指令

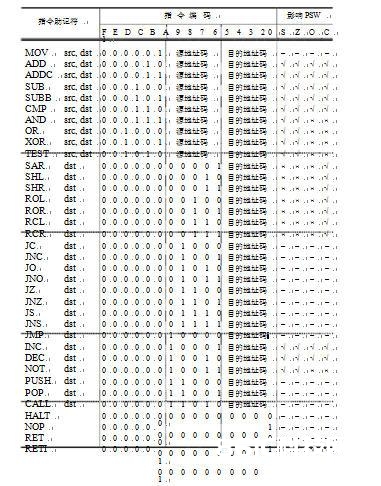

本模型机规划了 9 条双操作数指令:

MOV,

ADD、ADC,SUB、SUBB,CMP

AND、OR、XOR

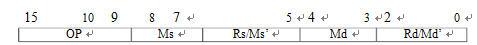

指令编码格局如下:

1.2.4.1 移位类指令

SHL、SHR:逻辑左移、右移

SAR:算术右移

ROL、ROR:循环左移、右移

RCL、RCR:带进位的循环左移、右移

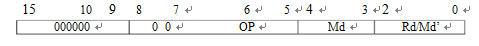

指令编码格局如下:

1.2.4.2 条件搬运指令

JC、JNC、JO、JNO、JS、JNS、JZ、JNZ

指令编码格局如下:

1.2.4.3 单操作数运算指令和无条件搬运指令

INC、DEC、 NOT、JMP

指令编码:

1.2.4.4 仓库指令和子程序调用指令

PUSH、POP、CALL

指令编码:

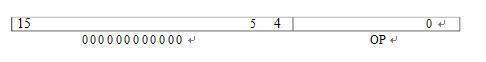

1.2.5 无操作数指令

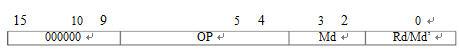

模型机规划有 4 条无操作数指令(NOP、RET、HALT、RETI)。因为没有操作数,(IR15~5

用全 0 表明扩展,(IR4~0)用于表明无操作数指令的操作码,其指令格局如下。

1.2.6 指令操作码编码表

表 1-2 指令操作码编码表

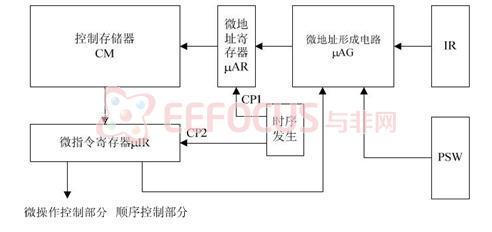

1.3 微程序操控器

1.3.1 微程序操控器的根本构成

微程序操控器由五部分组成,根本组成框图如图 1-3。

图 1-3 微程序操控器的根本组成

(1)操控存储器 CM ,寄存微程序。

(2)微地址寄存器 uAR,寄存 CM 地址。

(3)微指令寄存器 uIR ,寄存由 CM 中取出的微指令。

(4)微地址构成线路 uAG,构成微地址,送给 uAR。

该电路有三个输入,除了 µIR 的次序操控部分之外,还有 IR 和 PSW。IR 首要用于发生微程序的进口地址,比方依据指令的操作码构成对应各指令履行阶段的微程序进口地址。PSW 中的状况标志,在某些需求断定是否契合条件的场合,决议分支搬运的微地址。

(5)时序部件,发生微程序操控器的时钟信号。

微程序操控器的根本时序单位是微周期,微周期是一条微指令履行所需的时刻,一条微指令的履行时刻包含两部分:一部分是从 CM 中读取微指令所需求的时刻,这个时刻就是 ROM 的读出时刻,另一部分是微指令履行所需求的时刻,这个时刻包含微指令译码时刻 CPU 内部数据通路的传输时刻。

本规划中微程序的时序由 CP1 和 CP2 两个等周期信号组成。CP1 信号上升沿的作用是将微地址打入控存微地址寄存器,发动一次读操作。CP2 的上升沿的作用是将从 CM 中读取的微指令打入微指令寄存器,这标志着取微指令的完毕和履行微指令的开端。明显,CP1的上升沿到 CP2 的上升沿为取微指令时刻,而从 CP2 的上升沿至下一个 CP1 的上升沿为履行微指令时刻。

6

图 1-4 微程序操控方法的时序

1.3.2 微指令格局规划

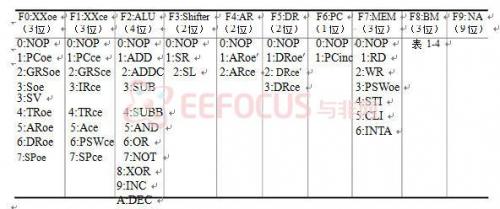

在本规划中,微指令的编码方法选用字段直接编码方法。微指令格局如表 1-3所示,其间数据传送操控类微指令占 1,2 两个字段,操作类指令占 3、4、5 共三个字段,下址字段 占 9 位,微搬运方法字段占 4 位,微搬运方法见表 1-4,微指令的总宽度为 32 位。

表 1-3 模型机微指令格局

表 1-4 模型机微搬运方法字段 BM

|

BM |

操作 |

含义 |

|

0 |

NA→µAR |

固定搬运 |

|

1 |

NA→µAR,,INTR·IF→µAR7 |

依据是否有中止请求且是否答应中止发生两分支 |

|

2 |

NA→µAR, ——— ——— ——— ——— ——— ——— IR 15· IR 14· IR 13· IR 12·IR 11·IR 10→µAR ,1 ——— ——— ——— ——— ——— IR 9· IR · IR · IR8 7 6·IR 5→µAR0 |

构成取源操作数、取意图操作数和履行阶段的微程序入 口地址。如果是双操作数指令,则 µAR =0;如果是单1 操作数指令,则 µAR =1、µAR =0;如果是无操作数指1 0 令,则 µAR =1、µAR =1。1 0 |

|

3 |

NA→µAR, {OP, PSW(Z,O,S, C)}→µAR0 |

依据条件搬运指令操作码和 PSW 的 ZF、OF、SF、CF 状 态标志决议微地址,若满意条件 µAR =1,不然 µAR0 0 =0。 |

|

4 |

按操作码 OP 多路搬运 |

按操作码 OP构成多路微搬运地址 |

|

5 |

NA→µAR,M→µAR1,0 |

按寻址方法 M 构成多路微搬运地址 |

|

6 |

NA→µAR,M ′→µ AR2,1 |

按寻址方法 M′构成多路微搬运地址 |

|

7 |

NA→µAR,IR + IR →µAR4 3 0 |

依据意图操作数是否为寄存器寻址发生两分支:Md=00 (寄存器寻址),µAR =0;不然 µAR =1。0 0 |

7