由于单部仪器上的触发/呼应通道有限,或由于需求混合信号的触发/呼应信道,因而许多测验与丈量运用,将需求对多部仪器进行时刻操控与同步化。举例来说,一部示波器或许最多有 4 个信道,而信号发生器最多有 2 个通道。从电子业的混合信号测验,到科学方面的雷射光谱学,这些运用都需求对较多的通道进行频率与同步化,或有必要针对数字输入与输出信道、模仿输入与输出通道,树立此两分组之间的联系。

一、在运用程序中的频率与同步化

在电子业界,混合信号测验为测验设备与芯片内建体系(SOC) 技能的一个重要层面。跟着将声响、印象,与数据,结合在消费性电子产品与通讯产品中的趋势,关于此类技能的测验需求(从根本产品至RF) 则更需求准确的频率与同步化。

根本上,混合信号设备具有多个数字与模仿信道。这些信道多半在一部 ATE 体系中一起进行测验,以节约测验时刻,并进步处理才能。此外,模仿信道还运用同步取样体系进行测验。同步取样体系需求在模仿转数字 (ADC) 与数字转模仿(DAC) 测验中,将不同的频率进行同步化。在频率范畴丈量中,这种同步作业能够削减频谱走漏 (spectral leakage),因而十分需求此同步化作业。

以下 LabVIEW 图表显现异步取样与同步取样的作用。白色轨道是异步频率,收集几回模仿正弦波周期。FFT 的频谱溢漏形成光谱图中的“下摆”。在相同的取样率下,同步取样体系发生的是赤色轨道。同步取样的重要长处之一,是由于信号收集时刻较短,因而缩短了测验的时刻。之所以能够缩短收集的时刻,是由于不需求收集额定的信号周期(这些额定的数据是运用于数字窗口中,以便消除频谱走漏)。

原则上,能够满意市场上品种多样设备弹性需求的ATE体系应该为仪器供给衍生自首要参看频率的不同频率,以便进行同步取样。此外,这套体系应该能够供给源自首要参看频率的恣意频率频率。

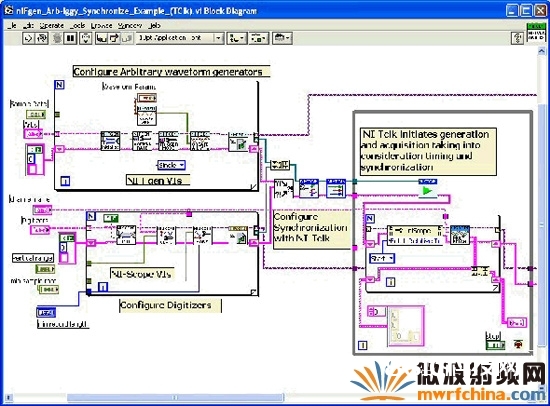

图 1. 以T-Clock (TClk) 同步NI PXI-5421 恣意波形发生器与NI PXI-5122示波器,以更短的时刻与更高的准确度,抵达相位的同步

在通讯方面,模仿及数字基带I/Q信号的发生及收集需求相位偏移 (phase offset) 与操控。数字信号发生器/剖析仪,以同步化恣意波形发生器与示波器,以处理数字与模仿 I/Q 信号的发生与收集。举例来说,在 3G W-CDMA 办法中,以挨近 5 MHz 带宽的信号而言,各信道之间的相位距离值及增益距离值,别离能够低到 0.003% 与 0.1%。在未来的 4G 通讯办法中(例如多重输入、多重输出,MIMO),将深切需以同步化进行多通道的基带、IF,与 RF 信号发生与收集。一项正逐渐成形的技能──数字波束成形(Digital Beamforming),正开端进入多种运用环境中,例如 4G MIMO 通讯、国防,与航天工业的雷达运用。数字波束成形需求具有数字能量降转 (downconversion) 引擎的多信道相位和谐数字化体系。

在半导体业方面,实务上的数字测验或许要耗费数千个数字针脚。市场上典型的整合电路 (IC) 或许要占用数字 I/O 的 200 个针脚。在这种运用环境中,多部数字信号发生器及剖析仪进行同步化,并以不可或缺的针脚对针脚偏斜与颤动,来处理很多接脚的 %&&&&&%。

在消费性电子方面,组件的数字印象信号发生与收集,或许需求多达五种不同的信号:三个首要的印象信号、H-Sync,与 V-Sync。经过频率与同步,可同步化恣意波形发生器和示波器,别离发生并收集高画质的印象信号,像素速率能够迫临 165 MHz。CMOS成像传感器(一种可望跟着印象电话与数字相机遍及,而成为干流的技能),便是混合信号技能的典范。其间的恣意波形发生器、示波器,与数字信号剖析仪经过同步化,供规划验证与查验芯片或芯片组。

在物理科学方面,具有很多信道的数字化体系被运用于电浆交融、雷射涣散试验,与粒子和天体物理学的光子/粒子侦测和追寻。在这些比如里,具有很多信道的数字化体系用于以 2D 或 3D 办法重建时空现象。这种运用办法需求多个通道一起取样,有时乃至超越数百个通道。

在医疗诊断体系方面,由于出现低价位 12 与 14 位的 50 MHz ADC,3D 数字成像体系正在敏捷替代模仿体系。这类体系往往具有数百到一千多个通道。在非破坏性测验中,3D 超音波成像是经过包括 50 MHz 示波器的多信道体系所完结。一种比超音波成像更为前进的成像办法──光学同调断层扫描术(Optical coherence tomography,OCT),或许需求数个示波器通道,以交流多种光电二极管,进行同步取样。

正如这许多运用范畴所出现的趋势,频率与同步技能,将是多信道信号/数据发生并收集的重要元素。

二、NI的模块仪器渠道

现在的NI模块仪器硬件渠道为PXI3 与PCI。这2 种渠道在实质上即为模块形状,并且运用PCI 总线做为PC 和仪器之间的接口。

于 1997 年推出的 PXI 是一项敞开规范,许多厂商供给各种 PXI 模块,包括从印象收集到 RF 矢量信号剖析仪。PXI 开端敏捷取得选用,主因是其小体积、可移植性、因选用 PCI 总线的高处理才能,与较低的价格;而 PXI 之所以具有以上的特性,是因其选用巨大 PC 产品所开发出来的规范商业技能。

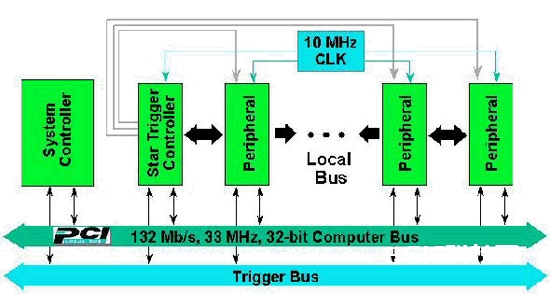

就功用而言,PXI 扩大了 CompactPCI 规范,参加部分总线与同步化功用。就同步丈量而言,内建至 PXI 中的重要组件包括参看频率、触发总线,与星型触发总线3。

图 2. CompactPCI 渠道的 PXI 频率与触发延伸图解

| 部分总线 | 触发器 | 频率 | 星状触发器总线 | |

| PXI | 13条线路 | 8 TTL | 10 MHz TTL | 每个扩展槽1个 |

三、同步化的建构组件

要在多部设备之间取得同步化,则有必要检视频率和触发器的散布。同步化有两种首要办法,可是在评论这些办法之前,咱们有必要先界说以下的用语。

取样频率、参看频率、触发器,与首要设备和隶属设备

由于并未规范化将丈量设备同步化的信号称号,或许会由于设备类型和制作商而有所不同。本文件运用以下名词来指称高速丈量设备,以阐明用于操控丈量的不同类型信号。

取样频率是时刻信号,用于操控示波器与信号发生器上的ADC 与DAC,以别离进行模仿转数字与数字转模仿操作。取样频率亦操控数字信号发生器/示波器,于取得或发生数字波型速度时的信号。在大多数的情况下,取样频率是一个周期信号,源自设备上的一个晶体振荡器。晶体振荡器技能的类型包括电压操控式晶体振荡器(VCXO)、温度操控式晶体振荡器(TCXO),与恒温晶体振荡器(OCXO)。

参看频率──许多仪器内含相位确定环路(PLL)。PLL 可将其输出频率确定为其输入端口的参看频率。在仪器方面,尽管有许多仪器供给多种可答应的频率做为参看频率,可是常见的频率为10 MHz。PLL 的输出一般便是取样频率。PLL 答应取样频率频率确定为参看频率频率。因而取样频率的肯定频率准确度与参看频率的频率准确度相同。

触发器信号操控在最高层级时的数据收集。外部事情或触发器是发动收集与信号发生的首要办法。触发器有各种不同的办法,包括模仿、数字,与软件。

首要设备及隶属设备──在树立同步化之丈量体系时,一般将指定一部设备做为首要设备,其他一或多部设备为隶属设备。首要设备担任发生用于操控体系中一切丈量设备的信号。隶属设备则接纳来自首要设备的操控信号。

同步化的方针,是准确地让多部硬设备发生并接纳模仿与数字信号。频率与同步的分级之一,称为同质频率(homogeneous timing) 与同步化──2 部设定相同的相同设备,其取样频率之间具有准确的相位联系,一起开端发生并/或收集信号。以下的典范阐明同质同步化:

• 2 部示波器以200 MS/s 的速度收集数据,其取样频率之间具有准确的相位联系:在同一时刻触发、笔直增益设定、AC/DC 巧合设定、输入阻抗设定、DC 偏移量设定,与模仿过滤器设定皆相同。

前一个典范中有一重要现象,便是同质同步化的许多设定相关。举例来说,示波器前端的增益阶段与模仿过滤器的推迟,将导致前端接头与ADC 之间的推迟。

同质同步化或许意指许多不同的情况。以下的一些比如都可用于阐明同质同步化:

• 2 部示波器别离以200 MS/s 与100 MS/s 的速度收集数据,其取样频率之间具有准确的相位联系:在同一时刻触发、笔直增益设定、AC/DC 巧合设定、输入阻抗设定、DC 偏移量设定,与模仿过滤器设定皆相同。

• 恣意波形发生器与示波器均以100 MS/s 的速度进行取样,其取样频率之间具有准确的相位联系,并在收到触发器信号时,以设定的时刻推迟开端操作。

• 1 部示波器、数字信号发生器/剖析仪,与恣意波形发生器,别离以50 MS/s、200 MS/s,与100 MS/s 进行取样,其取样频率之间具有准确的相位联系,并在收到触发器信号时,以设定的时刻推迟开端操作。

以上的比如清楚阐明同质频率与同步有许多或许性,得以处理运用方面的需求。各设备上的不同设定,可导致在同一时刻点上进行取样的信号/数据发生推迟。要害在于经过同步化的体系校对,这一点将在本文后边进行评论。

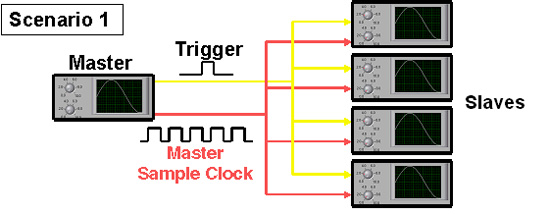

四、同步化办法之一:运用取样频率进行同步化

首要设备可输出触发器信号与取样频率至隶属设备,以操控丈量体系的运作。举例来说,由多部示波器与信号发生器构成的体系,将具有由首要设备供给的取样频率。如图3 所示,首要设备的取样频率,将直接操控一切设备上的ADC 与DAC 频率。举例来说,NI 动态信号剖析仪(如NI 4472 与NI 4461,别离为24 位104 kS/s 与208 kS/s) 即运用这种技能进行同步化,运用于声响与振荡丈量。

这种办法是最单纯的相位衔接取样办法;多部设备接纳相同的取样频率。因而一切设备都取得相同的取样频率正确性、偏移,与颤动。这种办法的缺陷在于无法满意一切相位衔接同质频率的需求。

图 3. 运用取样频率进行同步化

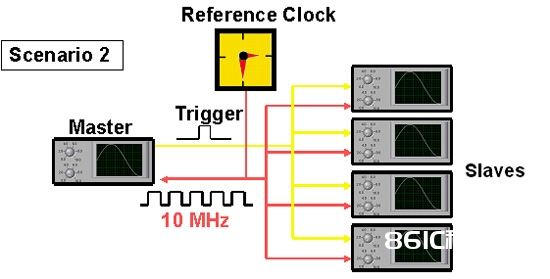

五、同步化办法之二:运用参看频率进行同步化

亦可在多部丈量设备之间运用相同触发器与参看频率,以到达同步化。在这种办法中,参看频率能够由首要设备供给(首要设备有必要内建参看频率),或是由专用的高精度频率来历供给参看频率。

这种办法的长处,即可从单一参看频率取得相同的取样频率,让一切的取样频率皆确定于此相位。缺陷是各设备上的相位衔接取样,并不如直接运用取样频率那样单纯,由于每一部设备的时刻都会发生影响,因而有必要考虑到设备频率的颤动问题。

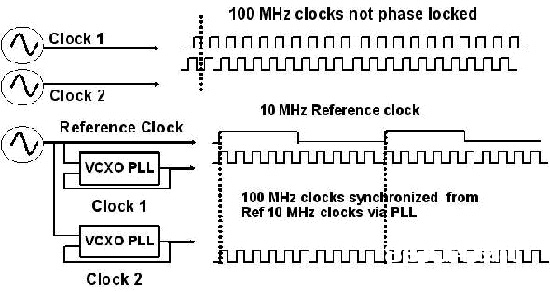

PLL 即常常选用此种办法进行同步化,并发生取样频率。

图 4. 运用参看频率进行同步化

图 5. 高速的取样频率运用 PLL 进行同步化。

六、同步化的问题

发送频率与触发器以取得高速同步化之设备,遭遇到少许的问题。针对同步化而言,有必要和谐多部丈量设备的潜在要素与时刻不确定性;关于高速丈量体系而言更是如此。工程师往往在开端的体系规划时刻中忽视这些问题,而约束同步化体系的速度与准确性。在发送频率与触发器时的2 个首要问题,即为偏斜(skew) 与颤动(jitter)。

七、取样频率同步化

以实质来说,混合信号测验需求在各仪器上选用不同的取样率,由于模仿波形 I/O 与数字波形 I/O 有必要选用不同的取样率;可是均有必要进行同步化。更重要的一点,有必要在各仪器上,以正确的取样频率边际进行数据取样。

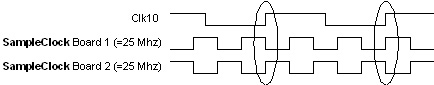

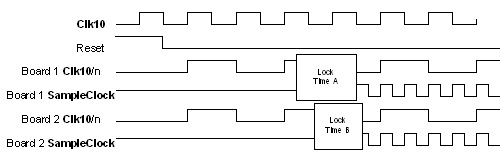

当不同仪器上的取样频率均为 10 MHz 参看频率的整倍数时,一切的仪器都将具有与其他仪器同步的取样频率──一切取样频率的进步距离都与 10 MHz 频率边际 (edge) 相符。如图 6 所示,尽管已确定相位为 10 MHz 参看频率,但当取样频率不为整倍数时(如 25 MHz),就不能保证取样频率同相 (in phase)。现在运用规范技能来处理这个问题,即一起从头设定一切的 PLL,使得同频率的取样频率变成同相,如图 7 所示。即便此刻一切的取样频率皆为同相,可是此处理办法依然不彻底。彻底同步化为:从设备到设备的数据时刻,坐落一个取样频率周期中。彻底同步化的要害在于触发,将于下文中评论。

图 6. 未校准之 25 MHz 取样频率

图 7:运用重设使 PLL 同步化

频率偏斜(skew)与颤动(jitter)

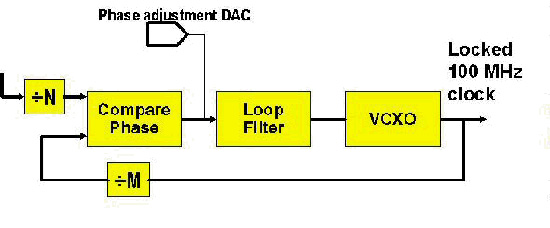

工程师有必要细心规划取样频率与/或参看频率的发送。举例来说,一个经同步化的丈量体系若要以 200 MS/s 取样率,于 20 个通道一起进行取样。则表明要将频率发送到 10 个双通道的示波器。假如取样频率偏斜 1%,则偏斜不能大于 25 ps。这样一个体系看起来极具应战性。还好,偏斜约束可针对每部丈量配备的偏斜进行校对来处理;能够在取样数据中,就偏斜部份加以补偿。真实的问题是频率频率。无论是发送一个 200 MHz 直接取样频率或 10 MHz 参看频率,都会在体系中形成颤动。发送体系的物理性质,在发送频率的准确性上扮演重要人物;假如频率的途径简略遭到高频电子噪音的影响,那么频率颤动就会成为显着的问题。针对用于发送高频取样频率的渠道,制作、测验,与校对都变得极为贵重。因而在许多高频体系中,遍及会运用较低频的参看频率来进行校对。图 8 是装置在NI SMC 模块仪器中的典型 VCXO PLL。回路带宽维持在最低,以防止来自参看频率的颤动,一起设备 VCXO 的颤动则低于 1 psrms。这样的体系能够有效地成为一个低颤动的同步体系。

NI 的 PLL 规划中,有一项十分有用的特性,便是运用一颗相位 DAC。运用相位 DAC 时,可将“VCXO 输出”和“输入的参看频率”进行相位对正。表面上,VCXO 输出与参看频率同相;但或许有必要将 VCXO 输出略为偏斜,使输出的相位略微偏斜。当送进各设备中的参看频率由于传送推迟而有少许偏斜时,则该项功用关于校准多部设备的取样频率就十分重要。举例来说,在 NI PXI-1042 的机架中发送 10 MHz 参看频率时,插槽至插槽的偏斜最高有 250 ps,最多有 1 psrms 的颤动。尽管 250 ps 的插槽至插槽偏斜对大部份运用而言没有问题,但或许不合适极高速运用;由于其相位准确度很重要。为了处理这个偏斜问题,相位 DAC 的输出可加以调整,以校对偏斜。在 NI PXI-5422,200 MS/s取样率的恣意波形发生器,与 NI PXI-5124,200 MS/s 取样率的示波器中,取样频率的相位/推迟调整为 5 ps,因而运用者在同步化多部设备时,可具有极大的弹性。

图 8. 具有相位调整 DAC 的 PLL──相位 DAC 使取样频率对应于参看频率的推迟愈加有弹性。

触发器偏斜与歪曲

在处理取样频率同步化的问题之后,别的一个首要问题便是发送触发器以发动同步作业。触发器或许来自1 个数字事情,或来自契合触发条件的模仿信号。一般来说,在多信道体系中,其间1 部设备被设定为首要设备,其他的则指定为隶属设备。在这个情况下,首要设备将发送触发信号给体系的一切隶属设备(包括其自身)。这儿出现的2 个问题为触发推迟 (delay) 和偏斜 (skew)。从首要设备发送到一切隶属设备时会发生触发推迟,而每部隶属设备之间会发生歪曲;此现象虽无法防止,可是此种推迟与偏斜均可加以丈量,并进行校对。

然而在丈量推迟与偏斜时,所面临的应战分红两个阶段:

1. 主动丈量首要设备和每一部隶属设备之间的触发推迟,并进行补偿。

2. 保证隶属设备之间的偏斜极小,以保证一切设备皆在相同的频率规模内收到触发器。

将触发信号发送到多部设备,需求将触发信号传送到取样频率的频率规模中,使触发器能在正确的时刻点上传送到每一部设备。

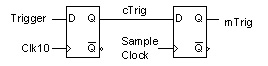

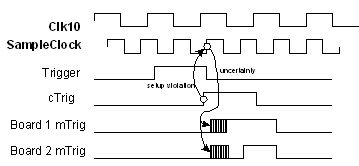

在取样频率低于或等于 100 MS/s 时,偏斜会成为触发器正确发送的首要妨碍。举例来说,若体系内含10 部 200 MS/s 取样率的设备,每部设备有必要在 5ns 的时刻规模内收到触发。则此约束关于想要供给 100 MHz 以上频率与同步的渠道形成显着担负。触发信号有必要以低于取样频率的频率规模发送,不然有必要树立1 个未经总线的办法来发送触发器信号(如点对点联机)。这种渠道的价格过高,并非运用干流。因而有必要选用别的一个发送通道:让触发器信号运用低频率规模,以安稳地发送,并且传送到高速取样频率规模。抱负的挑选之一,即为同步化触发器信号的发送与 10 MHz 的参看频率。可是,当取样频率并非10 MHz 参看频率的整倍数时,就无法保证2 组适配卡能于同一个取样频率周期中收到触发器信号。为了阐明这一点,假定2 部设备具有图 9 所示之简略回路4,供触发器从 10 MHz 参看频率规模传送到取样频率规模。

图 9. 10 MHz 触发器自参看频率规模传送至取样频率规模

即便设备的取样频率相同,以下的频率图表显现在2 部设备中,无法于相同取样频率周期中看到触发的原因。

图 10. 亚安稳 (Metastability) 在触发器上的作用

第一次触发器的输出(cTrig) 或许发生在过于挨近取样频率升高边际的当地,导致mTrig 变成亚安稳(metastable) 状况。当安稳状况安靖下来时,在不同的设备上或许有不同的处理办法,导致将同一个触发器信号视为发生在不一起刻的2 个事情。

八、SMC模块仪器与TClk

2003 年时,NI 以同步化与内存中心(Synchronization and Memory Core,SMC) 为根底,推出第一代PXI 示波器、恣意波形发生器,与数字信号发生器/剖析仪。SMC 中运用的要害技能之一,便是供频率与同步运用的T-Clock (TClk) 技能。

TClk

NI 开发1 种同步化的办法,当布署别的的信号频率规模时,可启用取样频率校准,与触发的发送和接纳。Tclk 技能的方针包括2 方面:

• TClk 可针对已相位确定10 MHz 参看频率,但却未校准的取样频率进行校准。

• TClk 可正确触发同步化后的设备。

TClk 同步化即具弹性,并且规模宽广;可运用于下列环境中:

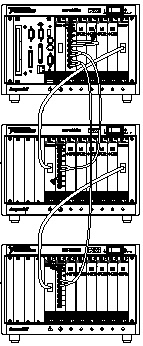

• 运用NI PXI-6653 Slot 2 体系频率与操控模块,从单一PXI 机架延伸至多部PXI 机架的同步化,以合作大型通道之用。

• 同质予异质同步化──运用外部或内部取样频率,以相同或不同取样率运作的设备。

• TClk 同步化能够运用在办法一与办法二中,如上文所描绘。

图 11. 运用 NI PXI-6653 体系频率与操控模块进行多机架同步化;由主控机架发送 10 MHz 参看频率至一切的隶属机架。NI MXI-4 可操控一切的隶属机架。

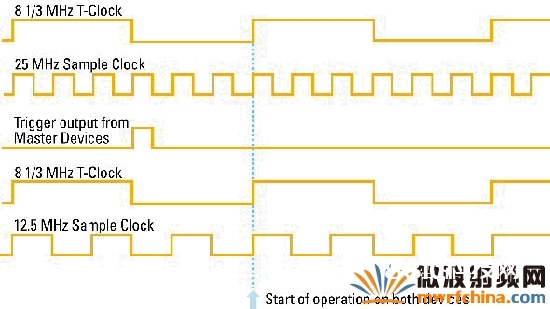

TClk 同步化的意图,是让设备能够一起对触发器呼应。“一起”指在同取样时段中,并且尽或许校准其取样频率。到达 TClk 同步化的办法,是让每一部设备依据取样频率发生一个触发频率 (TClk)。触发器与 Tclk 脉冲进行同步化。从外部来历接纳的触发器,或是在内部自行发生的设备,将于 TClk 的负缘 (falling edge) 上传送信号至一切设备(包括自身)。TClk 频率低于取样频率与 PXI 的 10 MHz 参看频率,以合作 NI PXI-1045 的18 槽机架(从插槽 1 至插槽 18 之间的传达推迟,或许会延伸至数个毫微秒)。假如运用程序呼叫多部机架时,传达推迟高于一般正常机架间的推迟,则可设定 TClk 频率。

此刻即出现“实时”数据收集的问题;假如契合触发器条件,并且有必要触发 10 部示波器,那么由于触发器对 TClk 的同步化操作,潜在的问题就会显现。处理这个问题的办法,是运用设备样本内存缓冲区中的触发前样本与触发后样本。一切的 TClk 设备,均能承受因触发器对 TClk 进行同步化而形成的时刻推迟。举例来说,将10 部示波器设定为一起收集 10,000 个样本。取样率为 200 MS/s (取样时刻5 ns),而引用之 TClk 频率则设定为 5 MHz (取样时刻200 ns)。这表明因 TClk 对触发器同步化所导致的收集推迟,或许高达 40 个样本。TClk 设备的规划会主动添补内存缓冲区,以补偿触发事情和开端收集之间的推迟,而 NI-TClk 驱动程序软件会主动调整一切示波器上的时刻符号,以反响开端收集与触发事情之间的时刻联系。

运用内部(PXI)参看频率,或运用者参看频率进行TClk运作的概述

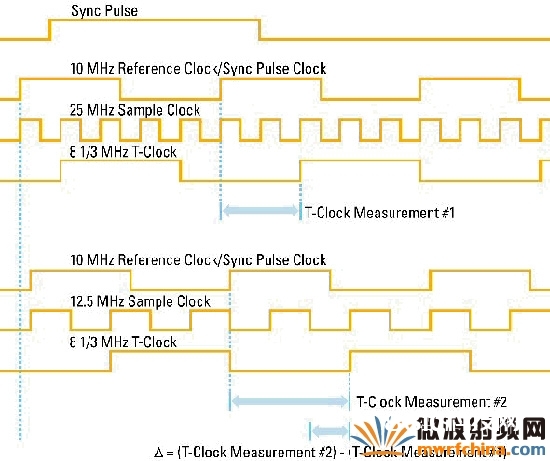

一切设备以下列的办法进行同步化。请参看图 12 的计时图表,了解取样频率的校准;图 13 则阐明触发器的发送与接纳。

1. 每部设备都设定1 个取样频率,并且设定为接纳TClk触发器。

2. NI-TClk 软件依据取样频率与设备数目,来主动核算TClk 频率,每部设备皆发生TClk (自该设备的取样频率而来)。

3. PXI 10 MHz 参看频率(在PCI 环境中,则运用某一个设备的内建参看频率) 发送至一切设备,确定一切设备的取样频率相位。

4. 每一部设备的取样频率相位皆确定于10 MHz 参看频率,可是在这个阶段中,并不一定和互相同相(in phase)。

5. 一个称为同步脉冲频率(Sync Pulse Clock) 的时刻信号,将经过PXI 触发器总线(在PCI 适配卡上则经过RTSI 总线),发送给一切频率相似参看频率的设备。10 MHz 参看频率在此除了是参看频率之外,也扮演同步脉冲频率的人物。

6. 当PXI 触发器总线(在PCI 适配卡上则为RTSI 总线) 上的同步脉冲频率(10 MHz 参看频率) 够高时,即从其间一部设备发生同步脉冲。

7. 在收到同步脉冲时,每设备经过初始化,以寻觅同步脉冲频率的第一个正缘(rising edge)。

8. 在侦测到同步脉冲频率的第一个正缘时,每部设备均程序规划为丈量此正缘和TClk 设备第一个正缘之间的时刻。一切设备均会丈量这2 道正缘之间的时刻。

9.一切设备上的TClk 丈量成果,将比较另一个TClk 参看丈量(NI-TClk 驱动程序会主动挑选其间一部设备),并且一切设备的取样频率与TClk,均藉由调整一切设备上的相位DAC 输出,以主动进行校准。

10. 在校准一切设备的取样频率之后,触发器信号即从指定的首要设备,经过TClk 发送至其他一切设备。触发器信号跟着首要设备的TClk 负缘发送,一切的设备都被设定于TClk 的下一个正缘时,发动信号发生或收集。这个信号也经过PXI 触发器总线(PCI 适配卡则经过RTSI 总线) 来发送。请参看图13。

T-Clock 同步化有2 项特点可影响此办法:

• 同步脉冲的发送关于TClk 同步化而言极为重要。同步脉冲有必要抵达每一部设备,让每一部设备在进行TClk 丈量时,都寻觅同步脉冲频率的同一段正缘。偏斜(skew) 不能超越同步脉冲频率的期间。只需同步脉冲频率期间为100 ns,这个问题很简略就能够处理。TClk 同步化可轻易地从在一部机架内扩大到数10 部机架,由于每呎50 奥姆缆线的规范推迟是2 ns。

• 取样频率校准的正确性与同步脉冲频率(参看频率) 的偏斜休戚相关。参看图12,则可看到2 部设备接纳到的参看频率均发生偏斜。假定已校准2 部设备的TClk 丈量的同步脉冲频率;2 个TClk 丈量之间的差异用于移动取样频率,使之进行校准。一起鄙人一节中咱们也能够看到,运用现在的技能,能够抵达2 个层次的效能:实时效能与校对效能。

图 12. 运用 TClk 校准取样频率的时刻图表。

图 13. 运用 TClk 进行触发器发送的时刻图表

概论:以用户供给之外部取样频率进行TClk 作业

在这个图表中,TClk 同步化不会校准各设备上的取样频率,由于是略过 PLL 回路,从外部供给取样频率。TClk 同步化保证发动/中止触发器的发送,使每一部设备都在相同的取样频率边际开端及中止收集/发生信号。TClk 到达这项操作的办法是选用和以上所介绍的、从取样频率取得 TClk 以发送触发器信号的相同办法。

在这儿,正确的取样频率校准作业由你供给的取样频率来担任。为了保证最佳的效能,在取样率高于 100 MS/s 时,应该运用同长度的缆线,从频率来历衔接至体系中的每一部设备,供给低颤动取样频率(小于 1 psrms)。

参看图13,可了解触发器发送与接纳的景象。

1. 每一部设备皆设定为接纳TClk 触发器与外部取样频率。

2. NI-TClk 主动依据取样频率与设备数量核算TClk 频率。然后,各设备依据设备的取样频率发生TClk。

3. 触发器信号运用TClk,从指定的首要设备发送至其他一切的设备;触发器信号跟着首要设备的TClk 负缘发送,一切的设备都设定于TClk 的下一个正缘时发动信号发生或收集。此信号也经过PXI 触发器总线(PCI 适配卡则经过RTSI 总线) 来发送。请参看图 13。

九、TClk技能的功能

实时功能

多部设备若要取得安稳的同步化,能够将设备参加PXI 机架中,再运用NI-TClk 软件来履行这些设备(请参看图14 的阐明)。要害的软件组件包括3 个VI/函式,而运用者有必要设定其参数。

图 14. 在多部恣意波形发生器和示波器之间,运用 TClk 同步化的 LabVIEW 程序区──NI TClk 供给的3 个 VI/函式将设备同步化

在NI PXI-1042 机架中,TClk 同步化可于各设备间偏移低于1ns 的情况下,使各设备同步化。规范的偏移规模在200 ps 至500 ps 之间。各设备之间的信道对信道颤动(jitter),将遭到设备的内蕴体系颤动影响。举例来说,NI PXI-5421 为100 MS/s 取样率,16位分辨率的AWG 体系总颤动量为2 psrms。由TClk 同步化的NI PXI-5421 设备,该信道对信道颤动一般低于5 psrms。运用NI PXI-5122 的100 MS/s 取样率、14位分辨率示波器时,其信道对信道颤动常低于10 psrms。

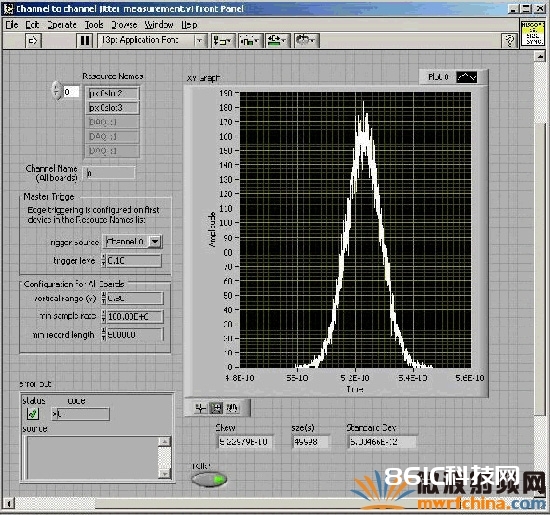

图 15. 2 部示波器进行 TClk 同步化的实时效能

图15 中的LabVIEW 人机接口,正丈量装置于NI PXI-1042 机架中的2 组NI PXI-5122 之间偏移量。在这个丈量设定中,偏移量约为523 ps。每示波器皆设定为以100 MS/s 取样率,对相同5 MHz 的方波进行取样。信号运用相同长度的缆线,分隔输入各示波器中。信道对信道颤动大约是6 psrms。数据是由方波的49,998 个过零(zero crossing) 所编译出来的。直方图中的高斯散布,反响出颤动是由随机噪声发生的,而不是体系中的固定噪声源。

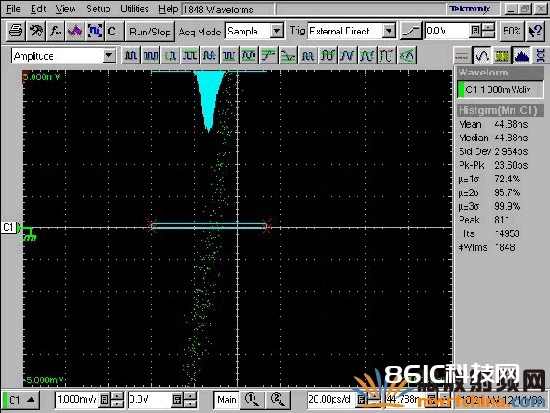

图 16:以 TClk 同步化的 NI PXI-5421 恣意波形发生器信道对信道颤动丈量

图16 是对2 部以TClk 同步化的NI PXI-5421 恣意波形发生器,所进行的信道对信道颤动丈量。2 部设备都设定为以100 MS/s 取样率发生1 个10 MHz 方波。此为Tektronix 高效能颤动丈量通讯信号剖析仪(CSA) 8200渠道上,以80E04 TDR 模块所进行的丈量。图16 中的直方图数据反响出信道对信道颤动低于3 psrms。直方图所报答的数据并非信道之间的偏斜;而是从方波的过零触发,到受丈量方波的下一个正缘之间的推迟(亦即1 个通道用于触发第2 个通道的过零丈量)。直方图出现丈量成果,并反响出信道对信道颤动的景象。

校对TClk同步化

正如从前所说到的,规范的偏斜规模或许在 200 ps 至 500 ps 之间。这个偏斜规模或许无法满意部份运用程序的要求,由于此丈量要求通道间有必要要有更高的相位准确度。在这种情况下有必要进行手动校对。手动校对能够将设备间的偏斜降至 30 ps 以下。图17 的 LabVIEW 人机界面显现 NI PXI-5122,100 MS/s 取样率示波器,与NI PXI-5124,200 MS/s 取样率示波器之间的偏斜。可发现偏斜是大约是 15 ps,信道与信道间的颤动大约是 12 psrms。数据是由方波的 10,000 个过零点编译而得。

图 17. 经校对的 2 部示波器TClk 同步化──100 MS/s 取样率的NI PXI-5122,与 200 MS/s 取样率的 NI PXI-5124──典型的偏斜大约是15 psrms,信道与信道间颤动大约是12 psrms。

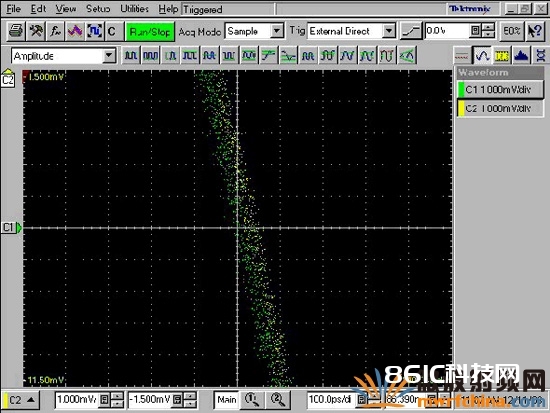

图 18. 手动校对 TClk 同步化的 NI PXI-5421 恣意波形发生器 10 MHz 方波负缘扩大图──偏斜大约是 20 ps。

图18 为运用CSA 8200 进行手动校对TClk 同步化的2 部NI PXI-5421 恣意波形发生器,中心所发生的偏斜。留意:偏斜约为20 ps。2 部设备发生的波形是一道10 MHz 方波。

手动校对包括运用 PLL 回路(参看图8) 中的相位调整 DAC,以调整各设备的取样频率。举例来说,在将2 部恣意波形发生器进行同步化时,同步化之输出可经过高速示波器加以检视,而 AWG 的取样频率也可运用相位调整 DAC 移到其它设备。经过这个手动进程,多部恣意波形发生器之间的偏斜,可从数百个兆分之一秒(picosecond) 削减到 30 ps 以下。

在对2 部示波器进行同步化时,会运用相同长度的缆线,将1 个低相位噪声信号输入每示波器中。偏斜能够用软件来丈量,示波器的取样频率也可依据其他示波器的相对联系进行调整。相同的办法亦用于数字波形发生器/剖析仪的同步化。

可用高分辨率调整取样频率。在 100 MS/s 取样率的设备上(如 NI PXI-5122、NI PXI-5421,与 NI PXI-6552),取样频率的推迟调整分辨率为 10 ps,可调整为±1 个取样频率期间 (10 ns)。在 200 MS/s 取样率的设备上(如 NI PXI-5422 与 NI PXI-5124),调整分辨率为 5 ps,则可调整为 ±1 个取样频率期间 (5 ns)。因而,设备之间的偏斜可进行准确手动校对。