时序脉冲发生和分频电路

时钟电路是数字体系不行短少的一个重要组成部分,由于数字电路只要在时钟电路的驱动下才可正常作业。依据运用场合的不同,不同数字电路挑选运用不同类型的时钟发生器。因交通灯控制体系的秒信号精度不高,故可选用555定时器,也可选用RC环行振荡器,考虑到红灯亮的时刻与倒计数的时刻共同,本体系选用CD4060计数器来得到一个时钟脉冲。

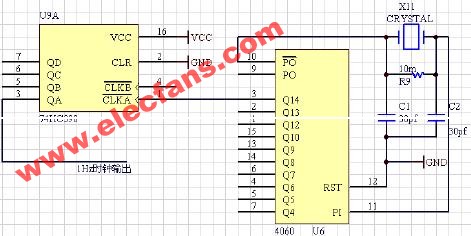

本规划经过CD4060计数器发生的是2Hz的时钟脉冲,不符合体系要求的1Hz时针脉冲,所以需求一个分频电路,即把CD4060所发生的信号进行2分频。该分频电路能够用任何一个二进制计数器来完成。本文选用74HC390计数器来完成,74HC390是一个双二-五-十进制加法计数器,其引脚接法及功用如下所示:

① 每个集成块中由2组计数器,每组计数器由两个计数器组成,共有4个计数器。

② 每组计数器内有1个一位二进制计数器和1个五进制计数器。它们能够独自计数,但清零时一起清零。A,B为时钟脉冲的输入,下降沿触发。QA,QB,QC,QD为计数输出。

③ 如1位二进制计数器的输出QA接上五进制计数器的时钟脉冲的输入B,则构成8421BCD码十进制的计数器。A为时钟脉冲的输入,QA,QB,QC,QD为输出,QD是最高位;五进制计数器的输出QD接上二进制计数器时钟脉冲输入A,则构成5421BCD码十进制的计数器,B为时钟脉冲的输入,QA,QB,QC,QD为输出,QA是最高位。

④ 清零RD为异步清零,高电平有用。

在本电路中,将clka与CD4060脉冲发生器的时钟输出相连,Qa即为1Hz时钟输出。其详细电路如图3所示。