导言

MPEG-4视频编码技能能够在较小的带宽下传输高质量的视频数据,节约很多存储空间,但编码杂乱度也较高,现在丰要有3种完结计划:在通用PC上编程完结;通过ASIC硬件完结以及运用通用DSP芯片完结。与前两者比较,通用DSP芯片完结计划具有以下优势:运算功用强;可晋级性好,与PC相似,通用DSP芯片的功用仍是通过编程来完结的,能快速、便利地进行软件晋级及增加新的功用,以习惯技能发展和商场改变;成本低、功耗低、习惯场合广泛。

体系硬件规划

编码体系处理中心为ADSP-BF533(以下简称BF533),运用其多功用并行接口PPI收集视频数据,该PPI具有DMA功用,无需内核干涉便可进行高速数据传输,传输完结后可主动向内核宣布DMA中止。

视频收集部分选用0mniVision公司的CIF级五颜六色CMOS图画传感芯片OV6630,其最大分辨率为352×288,收集速率最高可达60fps,且片内硬件完结了原始RGB数据到4:2:2YUV格局数据的转化,用户无需自行编写杂乱的RGB转YUV应用程序,大大削减了代码量,很合适用作MPEG-4编码。

设置OV6630输出为4:2:2 YUV视频数据格局,BF533的PPI即可直接接纳该格局视频数据。二者可完结无缝衔接,无需中心电路。

考虑到现在还有很多模仿制式的摄像机仍在广泛应用,体系中还增加了视频ADC ADV7183,该芯片能够把PAL制模仿电视信号转为ITU-R656规范4:2:2格局数字视频,相同将ADV7183输出端口与BF533的PPI相连。这样,既能够选用体系自带CMOS图画传感器收集视频,也能够外接PAL制模仿摄像机,用户可自由选择。

由于BF533片内存储空间有限,而视频收集、编码数据量巨大,选用一片Hynix公司的4MBSDRAM HY57V56162(内含4个内部子集)作为BF533片外大容量动态存储器。一起,为寄存程序发动代码,运用一片容量为1MB的闪存芯片PSD4256G6V构成BF533的片外非易失性存储器。体系硬件构成如图1所示。

编码器规划完结

存储器空间分配

BF533选用一致的32位、共4GB可寻址空间,包含坐落片内的L1高速SRAM,片外的同步存储器空间SDRAMSpace,以及异步存储器空间(A syn chronousMemory Space)。

片内Ll SRAM包含:64KB指令SRAM、16KB指令Cache/SRAM、32KB数据SRAM、32KB数据Cache/SRAM,以及4KB便签存储器。

L1 SRAM作业在内核时钟频率,内核能够对其进行高速带宽拜访。它是一切存储器中拜访速度最快的,但容量有限,因而,只应将那些最要害的代码和数据寄存在L1SRAM里。一起,指令Cache和数据Cache悉数使能,这样能够大大提高拜访片外存储器的功率。Cache设置是通过相应的I M E M_C O N T R O L、DMEM_CONTROL,以及CPLB寄存器装备完结的。

由于BF533片内存储空间有限,而原始视频数据量较大:CIF级4:2:2格局每帧图画占用的空间为202752字节,假如选用模仿PAL制式视频输入,每帧占用空间更是高达829440字节,只能将其放至SDRAM中。相同,视频编码数据也应寄存在SDRAM中。此外,体系发动完结Boot loader引导后,首要要害代码放在片内L1程序SRAM中履行,但大部分程序代码仍需从SDRAM中履行。由于SDRAM特别的读/写办法,假如下次拜访内存页与当时活动页(Active Page)不同,即呈现了页失去(Page Miss),SDRAM就必须首要封闭当时页,再翻开新的页,大大降低了SDRAM读写速率。而该体系中SDRAM又需存储多种数据,内核、DMA均需求频频拜访SDRAM,因而,应精心分配SDRAM空间,以使页失去现象尽量少产生。

BF533的SDRAM控制器(SDC)能够支撑SDRAM每个内部子会集的一个活动页,且在这4个I-Bank中进行切换时无需任何推迟。这样,将不同的数据、代码映射至不同的I-Bank,可使页失去现象降到最少,然后改进拜访SDRAM的功率。

由于需求实时编码,为确保视频收集和紧缩能够同步履行,选用乒乓缓冲技能:设置了两块视频帧接纳缓冲区BUF1和BUF2,选用BF533的DMA传输链办法进行传输。当某一DMA缓冲区填满后,内核对其作MPEG-4编码(一起也在构建参阅帧),此刻DMA开端对另一块缓冲区进行填充。由于BUF1、BUF2、程序代码以及参阅帧均坐落不同的I-Bank,削减了SDRAM页面切换的时机,完结了对SDRAM的高效拜访。

MPEG-4程序流程

MPEG-4编码是根据宏块(Macro Block)进行的,每个宏块包含4个8×8亮度子块和2个8×8色度子块。MPEG-4编码原理首要包含对I帧和P帧的编码,P帧比I帧多出了运动估量和补偿模块,二者编码流程如图2所示。

代码编写及优化

BF533支撑C/C++高档言语,但高档言语履行功率较低,为到达最大履行功率,选用全汇编言语完结MPEG-4编码。

关于I帧编码,首要的运算量是前向离散余弦改换FDCT和反向离散余弦改换IDCT,这儿选用了ADI供给的优化代码,它根据chen氏快速DCT算法,很多运用了BF533特有的并行指令,完结一次8×8 DCT仅需293个时钟周期。

与I帧比较,P帧编码相对杂乱,其间,运动估量是P帧编码最费时的部分,即在参阅帧中查找与当时编码宏块或子块最匹配的方位。

SAD(绝对误差和)原则具有无需乘除运算、完结简略便利等长处,选用它作为运动估量匹配原则。

运动估量查找算法则选用菱形查找法(又称钻石查找法),查找精度为半像素,菱形查找法具有简略、鲁棒、高效的特色。

Blackfin汇编指令会集有专门用于SAD核算的指令SAA(src_reg_O,src_reg_1),一条该指令即可一起完结4个字节的SAD核算。此外,归纳运用其它一些视频专用操作指令,如BYTEPACK(_将4个字节打包至一个3 2位寄存器中)、BYTEUNPACK(与BYTEPACK功用相反)、BYTEOPl6M(对4个字节作减法处理),能够使代码运转功率得到明显改进。

BF533集成开发环境VisualDSP++中还供给了Profile功用,能够运用该功用对程序代码功用进行评价,发现程序履行的瓶颈,然后进行有针对性的优化。首要的优化办法有:

1.尽量削减分支、条件判别指令,由于这些指令会损坏BF533流水线,形成额定的时钟推迟;一起,对部分较简略的子程序用宏改写,免除子程序调用进程中的仓库操作和参数传递;

2.选用并行履行指令,BF533并非超标量结构DSP,但仍能有限地支撑最多3条指令并行履行,如:saa(r1:0,r3:2)Ⅱr0=[i0++]Ⅱr2=[i1++];运用该并行指令即可在一个时钟周期内完结4个字节的SAD核算,一起完结r0、r2的数据更新,以便下次核算;

3.在DCT/IDCT的量化进程及其它一些模块中,要牵涉到除法,而BF533核算除法需求消耗很多时钟周期,因而,这儿将除法变为乘以量化因子的倒数,求倒数能够通过查找表办法完结。再结合移位操作,即可在基本不丢失精度的一起到达高效核算除法的意图。

通过前述的优化进程后,成功地在BF533上完结了MPEG-4 SP的CIF级实时编码。此外,关于CIF级CMOS传感器OV6630,体系能够直接对其实时编码。但假如是外接PAL制式模仿摄像头,经ADV7183作A/D转化后,其分辨率为720×576,受BF533的功用约束,尚无法对该等级分辨率做到实时编码,因而,应先使其分辨率降为352×288,然后再作:MPEG-4编码。

试验成果

BF533内核时钟(CLK)设为594MHz,体系时钟(SLK)为118.8MHz。选取CIF级规范测验序列flower(帧速率为25fps,共75帧)对体系进行验证。

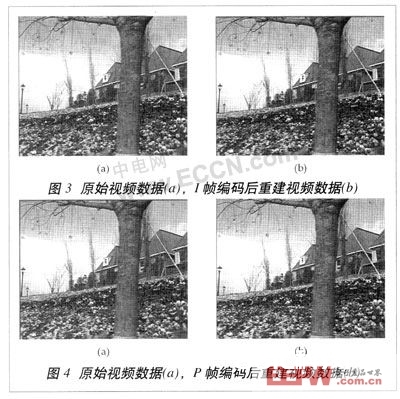

图3、图4给出了别离选用I帧编码和P帧编码后的重建图画。I帧编码紧缩率为11.5:1,重建图画信噪比为33.43dB。P帧编码紧缩率则到达了65.7:1,重建图画信噪比为32.65dB。经选用BF533片内实时时钟RTC准确计时,整个视频序列共75帧,编码消耗2.27s,均匀编码率到达了33fps,满意实时编码要求。

结语

本文介绍了CIF等级的MPEG-4 SP实时编码在BF533 DSP;DSP片上的完结,该编码器能够灵敏地选用体系自带CMOS传感器及用户自选PAL制模仿摄像机两种视频收集源。该体系能够用在IP可视电话、交通检测、超市监督、智能小区安保等范畴,具有很强的实用价值。