1 导言

在基站的模仿测验体系中,终端操控子体系担任生成上行测验数据并将其发送到被测基带板,测验基带板上行接纳的功用及功用;一起依据后台操控收集下行发射的基带数据并送后台进行剖析,测验其发射功用。而FPGA部分归于终端操控子体系的前台部分,担任IQ数据的发送及收集,基带测验板的功用首要在这里边完结。

整个体系的速率瓶颈在网口上,因为基带数据速率很高,每根逻辑天线的数据数率达122.88Mbps,而FTP传输数据的速率远远不够,故选用FPGA将高速基带数据缓存在板上的SDRAM中,能够很好的处理速率相差很大的接口问题。一起其开发周期较短,体系易于保护和扩展,无需改动硬件规划。

2 计划技能关键

2.1 基带测验板概述

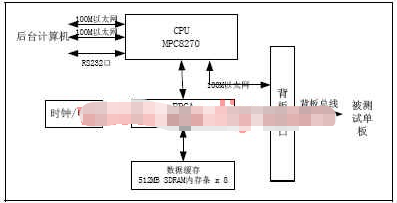

2.1.1 CPU模块

CPU模块是基带测验板的操控中心,完结:

和后台计算机通讯

加载FPGA

整体操控基带测验板的作业

CPU模块的中心是MOTOROLA 的POWER QUICC II系列的 MPC8270处理器。CPU的60X BUS外挂:

16Mx64 SDRAM。

8Mx16 FLASH。存储FPGA数据和运用程序。

512Kx8 FLASH。作为BOOT ROM,存储BOOT程序和VxWorks操作体系。

FPGA的CPU接口。

CPU经过PHY芯片,完结3个以太网口,其间2个用来和后台通讯一个和主控板通讯。

2.1.2 FPGA模块

FPGA模块是基带测验板的拓扑中心节点,完结:

将后台生成的上行测验数据写入SDRAM,并按CPU装备的图样发送到指定的发射端口。

依据CPU的装备,收集特定时间段的接纳端口的数据,完结之后经过CPU送给后台PC进行处理

和CPU模块通讯

SDRAM的读写操控

FPGA模块的中心是1片FPGA芯片,首要外部接口包含:

CPU接口。用来和MPC8270通讯。

LVDS接口。用来和背板接口模块的LVDS器材通讯。

SDRAM接口。用来和数据缓存模块的内存条通讯。SDRAM时钟由时钟电源模块供给。

测验用接口。

2.1.3 数据缓存模块

数据缓存模块由8条512MB SDRAM内存条构成4GB的大容量存储器,用来缓存天线数据。8片内存条的16根片选信号由FPGA别离供给;其它信号,包含地址、数据、字节使能、时钟等共用。

2.1.4 时钟电源模块

时钟电源模块为基带测验板的其它模块供给电源和各个时钟信号。

FPGA时钟:100MHz

MPC8270时钟:100MHz

以太网时钟:25MHz

3 本计划中FPGA的规划思路

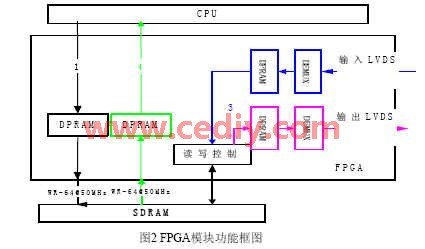

咱们将整个FPGA首要分为4个大的模块:发送处理模块,接纳处理模块,时钟/寄存器模块,SDRAM操控模块。FPGA的上下行接纳模块功用框图如图2:

上面的处理包含4个进程如下:

1. 将CPU写入到DPRAM中的数据写入SDRAM,此进程重复履行,一切数据写完停止;

2. 依照CPU装备的发送图样,接连从SDRAM相应地址中读取数据,经过复用后发送到发送端口;

3. 依照CPU装备将接纳端口的数据进行解复用,然后经过DPRAM将数据存入SDRAM.

4. 数据收集完结后,将缓存在SDRAM中的数据经过DPRAM上报给CPU;

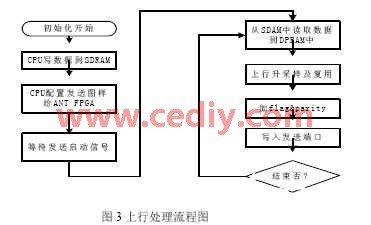

3.1 发送处理模块

发送处理模块首要包含上面处理进程1,2。其完好的流程如下图3:

发送模块首要处理将后台生成的上行测验数据发射出去,送到被测基带板,故发送处理模块需求依照被测基带板上行接纳的格局进行复用。上行处理进程是:先从SDRAM中读出数据缓存在双口RAM中,然后对其进行升采样(简略重复)及复用操作,最终加flag和parity bit后,由本来的下行发送端口送出。在循环发送上行数据前,与CPU合作,要将后台生成好的数据写入SDRAM中;另,在将数据从SDRAM中读取到DPRAM中时,需求依照CPU装备的发送图样(即数据块的发送次序)进行。其间发送图样能够灵敏装备,详细完结能够选用乒乓DPRAM的办法。

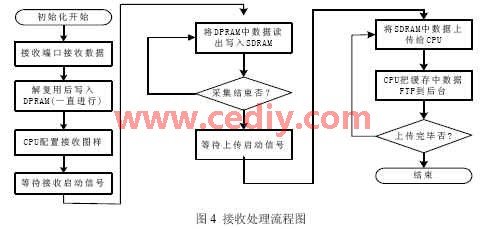

3.2 接纳处理模块

接纳模块包含处理进程3,4。图4是收集数据上报的流程图:

接纳处理模块完结的首要功用是依据CPU装备的数据收集规模(若干帧),在SFN等于装备的开端SFN时,将来自被测基带板的若干帧下行发射数据收集到SDRAM中缓存;收集完结之后,再上报给CPU,最终由CPU将缓存数据上报给后台进行剖析。

3.3 时钟/寄存器模块

时钟/寄存器模块依据输入的16chip时钟和从时钟板送来的串行帧号,发生内部其他模块运用各种时钟、帧信号。板内时钟与16chip时钟上升沿对齐。帧信号周期为10ms,是负脉冲,宽度为1/16chip,在1chip上升沿改变。供给寄存器接口,由CPU操控,供给告警中止等。本模块还依据输入的100Mhz时钟发生外接SDRAM用的时钟。

3.4 SDRAM操控

首要依据发送收集等模块的状况来操控SDRAM操控器的输出,发生SDRAM需求的/CS、/RAS、/CAS、/WE等各种操控信号,从而对SDRAM进行操作。

4 器材阐明

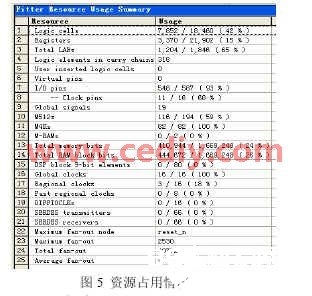

归纳考虑速度和资源,FPGA芯片咱们选用了Altera公司Stratix系列的EP1S20F780C7。这个芯片是780Pin FineLine BGA封装,最多可用IO587个,具有逻辑单元18460个,内部有194个块M512 RAM、82个块M4K RAM、2个块M4Kx144 RAM (可灵敏装备为不同的数据口宽,可是容量不变)。StraTIx系列内核选用1.5V供电,IO支撑1.5V/1.8V/2.5V/3.3V多种接口标准,支撑高速外部存储器接口,包含ZBT,QDRSDRAM,DDRSDRAM,FCRAM和SDRAM。为了与单板其他部分合作,咱们IO选用了3.3V供电。图5显现该芯片能够满意需求。

5 定论

实践成果证明,该计划规划的基带测验体系能够一起收集和发送12个逻辑天线的数据,彻底能够满意测验的需求。

本规划充分利用了FPGA并行处理多路信号和处理高速数据的才能,经过对SDRAM的操控来完结速率相差很大的后台与测验环境之间的数据交换。不失一般性,该规划的思路也能够推行到其他测验和运用场合。

责任编辑:gt