一、导言

SPI串行通讯接口是一种常用的标准接口,因为其运用简略便利且节约体系资源,许多芯片都支撑该接口,运用适当广泛。SPI接口的扩展有硬件和软件两种办法, 软件模仿 SPI接口办法尽管简略便利, 可是速度受到限制,在高速且日益杂乱的数字体系中,这种办法明显无法满意体系要求,所以选用硬件的办法完成最为切实可行。当时,依据主从处理器结构的体系架构现已成为一种干流(如 DSP+FPGA,MCU+FPGA等),FPGA是在 ASIC的根底发展出来的,它克服了专用 ASIC不行灵敏的缺陷。与其他中小规划集成电路比较,其长处首要在于它有很强的灵敏性,即其内部的详细逻辑功用能够依据需求装备,对电路的修正和保护很便利。现在, FPGA的容量现已跨过了百万门级,使得 FPGA成为处理体系级规划的重要挑选计划之一。在这种架构下,运用 FPGA来构建 SPI通讯接口是切实可行的。传统 SPI接口的 FPGA完成往往运用厂家供给的 IP核完成,可是经笔者实践发现,这种办法尽管能够满意根本 SPI通讯要求并且速度比较快,可是规划不行灵敏,不利于功用扩展,例如用户无法知道其内部作业状况,操控信号时序杂乱等,用户运用时往往觉得困难,别的,该 IP核不是免费的。依据此,本文将提出一种新的依据 FPGA的 SPI接口规划办法。

二、SPI总线原理

SPI总线由四根线组成:串行时钟线(SCK),主机输出从机输入线(MOSI),主机输入从机输出线(MISO),还有一根是从机挑选线(SS),它们在与总线相连的各个设备之间传送信息。

SPI总线中所有的数据传输由串行时钟SCK来进行同步,每个时钟脉冲传送1比特数据。SCK由主机发生,是从机的一个输入。时钟的相位(CPHA)与极性(CPOL)能够用来操控数据的传输。CPOL=“0”表明 SCK的停止状况为低电平,CPOL =“1”则表明SCK 停止状况为高电平。时钟相位(CPHA)能够用来挑选两种不同的数据传输形式。假如 CPHA =“0”,数据在信号 SS声明后的第一个 SCK边缘有用。而当 CPHA=“1”时, 数据在信号 SS声明后的第二个 SCK边缘才有用。因而,主机与从机中 SPI设备的时钟相位和极性必需求共同才干进行通讯。

SPI可作业在主形式或从形式下。在主形式,每一位数据的发送接纳需求 1次时钟效果,而在从形式下, 每一位数据都是在接纳到时钟信号之后才发送接纳。 三、规划原理

本体系用硬件描绘言语 VHDL描绘,可 IP复用的通用结构。 1、典型运用

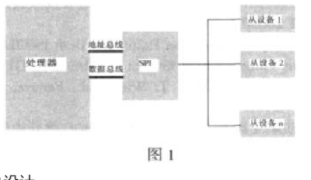

SPI接口的典型运用如图 1所示。微处理器与从设备经过发送指令的方法完成双向数据传输。

2、模块规划

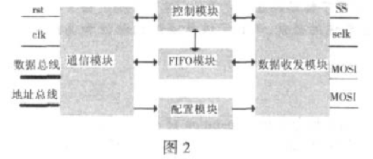

依据 SPI总线的原理,可分为以下功用模块:通讯模块,操控模块,FIFO模块(缓冲存储器),装备模块,数据收发模块,如图 2所示。

2.1通讯模块

这个模块完成与微处理器的通讯,接纳微处理器的数据和指令,经过指令解析,宣布操控信号。该模块界说的寄存器包含发送数据寄存器,接纳数据寄存器,测验数据寄存器,接纳测验数据寄存器,指令寄存器,装备寄存器,状况寄存器,各寄存器详述如下:

发送数据寄存器:可写寄存器,接纳微处理器发送的数据,然后暂存于 FIFO模块中;

接纳数据寄存器:可读寄存器,当收到读数据指令时,该寄存器将从 FIFO中读入数据且经过数据总线发送至微处理器;

测验数据寄存器:可写寄存器,用于在测验形式下接纳测验数据,然后暂存于 FIFO模块中;

接纳测验数据寄存器:可读寄存器,当收到读测验数据指令时,该寄存器读入 FIFO中的测验数据,并经过数据总线发送至微处理器,以测验各功用模块作业是否正常;

指令寄存器:可写寄存器,接纳微处理器的指令,经过指令解析后,往其它模块宣布相应的操控信号,包含发送数据指令,读数据指令,复位指令,写测验数据指令,读测验数据指令;

装备寄存器:可写寄存器,用于保存 SPI装备参数,包含时钟分频倍数、相位、移位次序、帧长度等。该寄存器的值将被转发至装备模块。

状况寄存器:只读寄存器,操控模块将状况机状况写入该寄存器,供微处理器查询 SPI

作业状况;

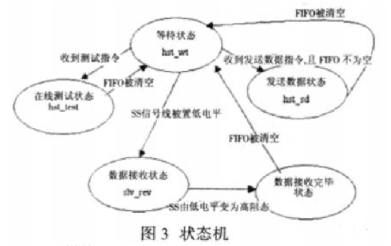

2.2操控模块

操控模块是本体系的中心,操控着整个作业流程,为了便利结构化规划,本模块规划了状况机。依据 SPI总线的原理可将总线分为五种状况,分别是等候状况、数据发送状况、数据接纳状况、数据接纳结束状况、在线测验状况。各状况之间的联系如图 2所示:

2.3 FIFO模块因为微处理器的写数据速率远比串口输出速率快得多,所以有必要先将数据保存于缓冲区,FIFO的容量应依据通讯数据量的巨细来确认,在本规划中,因为数据量不大,所以界说了一个 64 X 8位的异步 FIFO寄存器,用于保存收发数据,用 VHDL硬件描绘言语描绘的FIFO是一个 64 X 8位的数组。模块包含两个时钟信号,写入和读出数据总线,满标志和空标志信号,当 FIFO为满标志时,写入的数据将被疏忽。

2.4装备模块 该模块规划了2 个 3 X 12位的RAM,一个用于保存主机模块装备参数,另一个用于保存从机形式装备参数,每次主从机形式切换时将装备参数发送到数据收发模块。数据收发模块依据装备参数调整分频倍数、相位、输出次序(高位先出或低位先出)、帧长度等。

2.5数据收发模块

该模块完成与从设备的通讯。在主机形式下,将 FIFO的并行数据进行并串改换,然后经过 MOSI引脚输出数据,并一起输出驱动时钟和操控信号(低电平)。在从机形式下将串行输入的数据串并改换后写入 FIFO模块中。

四、仿真与验证

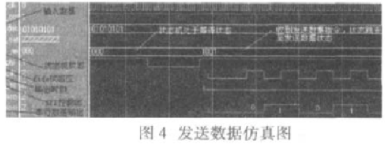

将用 vhdl描绘好的 SPI接口电路用 synplify进行归纳,然后用 modelsim软件进行仿真。先仿真微处理器经过 SPI接口发送数据进程,在地址总线上输入指令寄存器地址,在数据总线上输入发送数据指令,作业时钟为89.6M,然后在地址总线上输入写数据寄存器地址,在数据总线上输入数据 01010101。得到如图 3所示的部分管脚的波形。

然后仿真从设备发送数据进程,首先往 SPI模块的 ss管脚输入低电平,一起从 sclk管脚输入驱动时钟,在 mosi管脚输入数据,得到图 4所示的波形。

用 quartus软件进行编译后,将生成的网表文件经过 JTAG下载到 altera公司的 acex1k系列 EP1k30TC144-3运转,合作规划好的单片机程序,分别给 FPGA输入 44.8M和 89.6M作业时钟,在 quartus的 signal tap的辅佐剖析下都得到了正确的成果。 EP1k30TC144-3芯片共有1728个逻辑单元,本规划运用了 138个,占体系资源的7%,是个比较抱负的成果。

五、结束语跟着半导体技能的前进,FPGA的价格越来越廉价,作业频率越来越高,运用 FPGA完成 SPI通讯接口是切实可行的,本文作者立异点: 1、将总线操控信号封装成指令,运用者只需经过发送指令的方法操作,避免了杂乱的

时序逻辑规划问题。 2、能够在 SPI作业进程中随时调整装备参数。 3、充分考虑了可测验性规划,运用者可随时检查 SPI总线作业状况。

责任编辑:gt